- •Лекция 1. Основы цифровой техники.

- •Лекция 2. Синтез кцу

- •Лекция 3. Шифраторы. Дешифраторы.

- •Синтез и анализ работы шифраторов на микросхемах логических элементов.

- •1 Элемент 5и-не.

- •Контрольные вопросы:

- •Лекция 4-5. Преобразователи кодов. Мультиплексоры и демультиплексоры.

- •Контрольные вопросы:

- •Лекция 6. Сумматоры. Цифровые компараторы. Арифметическо-логические устройства (алу).

- •Лекция 7-8. Раздел 3. Последовательностные цифровые устройства. Интегральные триггеры.

- •§ 4.3. Структура и особенности работы

- •Лекция 10-11. Счетчики.

- •Лекция 12. Запоминающие устройства.

- •Лекция 13-14. Системы управления.

- •Лекция 15. Общие сведения о микропроцессорах (мп) и микропроцессорных системах (мпс).

- •§ 5.4. Структура и назначение основных узлов микропроцессора серии кр580.

- •Форматы команд.

- •Система команд.

- •Способы адресации.

- •Разработка линейных программ.

- •5. Число "а" из озу

- •7. Вычитание без переноса

- •Микроконтроллеры.

- •1. Структура и назначение основных узлов микропроцессора серии кр580.

- •Практическая работа №1 «Анализ работы логических элементов»

- •Практическая работа №2 «Синтез и анализ работы кцу в базисе и,или,не»

- •Практическая работа № 4 «Синтез и анализ работы шифратора»

- •Практическая работа № 5 «Синтез и анализ работы дешифратора»

- •Практическая работа № 6-7 «Синтез и анализ работы преобразователя кодов»

- •Практическая работа № 10-11 «Синтез счетчика с параллельным переносом»

- •Практическая работа № 12-13 «Построение зу заданной емкости и разрядности»

- •Практическая работа № 14-15 «Синтез и анализ работы уу со схемной логикой»

- •Приложение 1. Справочный материал по микросхемам

- •Сумматор, компаратор, схема контроля ч етности, алу и схема ускоренного переноса.

- •И нтегральные триггеры.

- •Регистры и регистровые файлы.

- •Счетчики.

- •10. Запоминающие устройства.

Лекция 13-14. Системы управления.

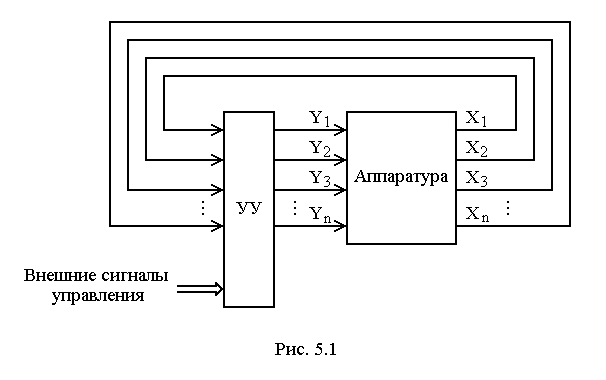

При разработке систем управления используются два принципиально разных подхода:

Принцип схемной (жесткой) логики. Здесь в процессе проектирования подбираются микросхемы и разрабатывается такая схема их соединения, которая обеспечивает функционирование системы для управления каким-то одним, строго определенным процессом (или несколькими, но, как правило, не очень сложными), происходящим в аппаратуре. Например, для автоматического выбора диапазонов и настройкой на заданные частоты в радио- и телеприемниках, запоминания номеров наиболее часто вызываемых абонентов и организацией повторных вызовов в телефонных аппаратах и т.д.

П

ринцип

программируемой логики. В этом случае

с помощью одной или нескольких БИС

строится универсальное устройство,

способное решать множество самых

разнообразных задач по комплексному

управлению работой аппаратуры. По

своему основному узлу – микропроцессору

(МП) – такие УУ обычно называют

микропроцессорными системами

управления (МПС). Например, МПС сейчас

используются для управления работой

целых АТС (электронных и квазиэлектронных),

усилительных подстанций и радиорелейных

станций, кабельных и радиорелейных

магистралей и т.д.Любое УУ связано с

аппаратурой, для управления которой

оно и предназначено, в основном двумя

группами цепей (рис. 5.1):

ринцип

программируемой логики. В этом случае

с помощью одной или нескольких БИС

строится универсальное устройство,

способное решать множество самых

разнообразных задач по комплексному

управлению работой аппаратуры. По

своему основному узлу – микропроцессору

(МП) – такие УУ обычно называют

микропроцессорными системами

управления (МПС). Например, МПС сейчас

используются для управления работой

целых АТС (электронных и квазиэлектронных),

усилительных подстанций и радиорелейных

станций, кабельных и радиорелейных

магистралей и т.д.Любое УУ связано с

аппаратурой, для управления которой

оно и предназначено, в основном двумя

группами цепей (рис. 5.1):

Управляющие цепи ,

,

,

,

… ,

,

… ,

,

идущие от УУ к аппаратуре. Появление

активного сигнала в одной управляющей

цепи "Y" вызывает

срабатывание соответствующего ЦУ в

аппаратуре, выполняющего нужную

микрооперацию (МО), которую разделить

на более простые действия невозможно.

Активный сигнал на любом управляющем

выходе Y может

одновременно поступать на два или более

цифровых устройства в аппаратуре и

вызывать их одновременное срабатывание.

Такая совокупность активных сигналов

с какого-либо выхода Y

управляющего устройства, под действием

которых происходит одновременное

выполнение нескольких МО в разных узлах

аппаратуры в одном тактовом интервале,

называется микрокомандой (МК).

Последовательность определенного

количества МК, необходимых для решения

поставленной задачи (напоминаем, что

для нас – это задача управления работой

аппаратуры), называется микропрограммой

(МП) решения этой задачи.

,

идущие от УУ к аппаратуре. Появление

активного сигнала в одной управляющей

цепи "Y" вызывает

срабатывание соответствующего ЦУ в

аппаратуре, выполняющего нужную

микрооперацию (МО), которую разделить

на более простые действия невозможно.

Активный сигнал на любом управляющем

выходе Y может

одновременно поступать на два или более

цифровых устройства в аппаратуре и

вызывать их одновременное срабатывание.

Такая совокупность активных сигналов

с какого-либо выхода Y

управляющего устройства, под действием

которых происходит одновременное

выполнение нескольких МО в разных узлах

аппаратуры в одном тактовом интервале,

называется микрокомандой (МК).

Последовательность определенного

количества МК, необходимых для решения

поставленной задачи (напоминаем, что

для нас – это задача управления работой

аппаратуры), называется микропрограммой

(МП) решения этой задачи.Цепи обратной связи , , , …,

сигналов "флагов" (признаков),

которые формируются в аппаратуре и

идут к УУ. При формировании управляющих

сигналов на выполнение очередной

микрооперации УУ очень часто должно

учитывать результат предыдущей МО. В

этом случае полученный в аппаратуре

результат МО в виде сигнала флага "Х"

по соответствующей цепи обратной связи

поступает в УУ, которое вырабатывает

очередные управляющие сигналы уже с

учетом этого флага.

сигналов "флагов" (признаков),

которые формируются в аппаратуре и

идут к УУ. При формировании управляющих

сигналов на выполнение очередной

микрооперации УУ очень часто должно

учитывать результат предыдущей МО. В

этом случае полученный в аппаратуре

результат МО в виде сигнала флага "Х"

по соответствующей цепи обратной связи

поступает в УУ, которое вырабатывает

очередные управляющие сигналы уже с

учетом этого флага.

Синтез и анализ работы УУ

со схемной логикой.

У У

со схемной логикой по своей структуре

более простые, поэтому мы с них и начнем.

Для разработки схемы такого УУ необходимо

знать только одно: алгоритм

функционирования аппаратуры (то есть

последовательность выполнения операций

в этой аппаратуре), для управления

работой которой и будет предназначено

данное УУ.

У

со схемной логикой по своей структуре

более простые, поэтому мы с них и начнем.

Для разработки схемы такого УУ необходимо

знать только одно: алгоритм

функционирования аппаратуры (то есть

последовательность выполнения операций

в этой аппаратуре), для управления

работой которой и будет предназначено

данное УУ.

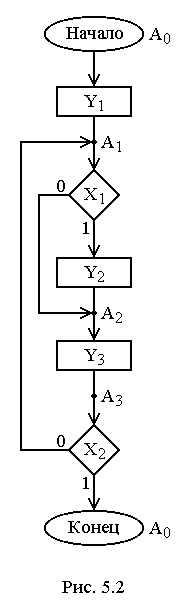

Определяем количество состояний А0, А1, А2 и т.д., в которых могут находиться узлы аппаратуры в процессе работы, и указываем их в алгоритме (рис. 5.2).

Начальное состояние обозначим А0. В дальнейшем каждая микрокоманда Y вызовет срабатывание одного или нескольких устройств аппаратуры, и состояние их меняется: после – A1, после – А2, после – А3. В момент окончания работы аппаратура должна возвратиться в исходное состояние А0 и быть готовой к выполнению следующего цикла работы с новыми исходными данными.

Определяем количество и вид триггеров в регистре состояний.

Для запоминания состояний, в которых будут находиться узлы аппаратуры в отдельных тактовых интервалах, введем в УУ запоминающее устройство – регистр состояний. Количество триггеров в этом регистре n из соотношения 2n ≥ А (где А = 4 – количество состояний) получается равным: n = 2. Как известно, для построения регистра в принципе можно использовать любые триггеры, но в данном случае они должны быть обязательно синхронными для тактирования работы УУ. Возьмем, например, синхронные JK-триггеры.

Таблица истинности регистра состояний (табл. 5.1).

Табл. 5.1

Состояния |

Код состояния на выходах регистра |

|

Q1 |

Q0 |

|

А0 |

0 |

0 |

А1 |

0 |

1 |

А2 |

1 |

0 |

А3 |

1 |

1 |

Здесь

каждому состоянию присвоим свой (в

данном случае двухразрядный) код, который

и будет храниться на выходах регистра

![]() и

и

![]() .

Какой конкретно код какому состоянию

присвоить – в принципе безразлично, но

лучше всего – код номера состояния.

.

Какой конкретно код какому состоянию

присвоить – в принципе безразлично, но

лучше всего – код номера состояния.

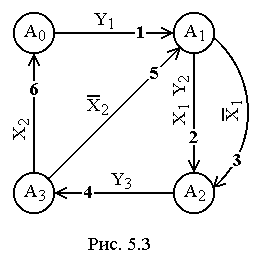

Р азрабатываем

граф-схему переходов (рис. 5.3).

азрабатываем

граф-схему переходов (рис. 5.3).

Здесь,

пользуясь алгоритмом (см. рис. 5.2), кружками

обозначаем состояния А, стрелками

(каждая такая стрелка называется: граф

перехода) – переходы из одного

состояния в другое ближайшее. Рядом с

каждой стрелкой указываем условия

данного перехода: какие требуются

микрокоманды Y и какие

флаги Х нужно при этом учесть (если

переход выполняется при условии X=1,

то указываем просто: Х; если же Х

= 0, то указываем:

![]() .

Пронумеруем все переходы в любой

последовательности: хотя бы так, как на

рис. 5.3.

.

Пронумеруем все переходы в любой

последовательности: хотя бы так, как на

рис. 5.3.

Составляем таблицу истинности УУ (табл. 5.2):

Табл. 5.2

Номер перехода |

Состояния |

Флаги |

МК |

Сигналы на входах триггеров регистра состояний |

||||||||

предыдущее |

последующее |

|||||||||||

А |

Q1 |

Q0 |

A |

Q1 |

Q0 |

Х |

Y |

J1 |

K1 |

J0 |

K0 |

|

1 |

A0 |

0 |

0 |

A1 |

0 |

1 |

- |

|

0 |

x |

1 |

x |

2 |

A1 |

0 |

1 |

A2 |

1 |

0 |

|

|

1 |

x |

x |

1 |

3 |

A1 |

0 |

1 |

A2 |

1 |

0 |

|

- |

1 |

x |

x |

1 |

4 |

A2 |

1 |

0 |

A3 |

1 |

1 |

- |

|

x |

0 |

1 |

x |

5 |

A3 |

1 |

1 |

A1 |

0 |

1 |

|

- |

x |

1 |

x |

0 |

6 |

A3 |

1 |

1 |

A0 |

0 |

0 |

|

- |

x |

1 |

x |

1 |

П р и м е ч а н и е : сигналы на входах триггеров регистра состояний определяются по таблице переходов соответствующих триггеров (см. табл. 4.4 из § 4.11).

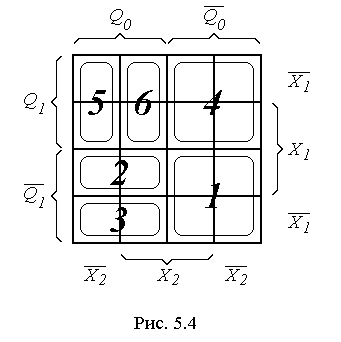

Определяем порядок заполнения карт Вейча.

Для каждой строки табл. 5.2 записываем многочлены СДНФ:

1.

![]() 2.

2.

![]() 3.

3.

![]() 4.

4.

![]() 5.

5.

![]() 6.

6.

![]()

и определяем их место в карте Вейча (рис. 5.4).

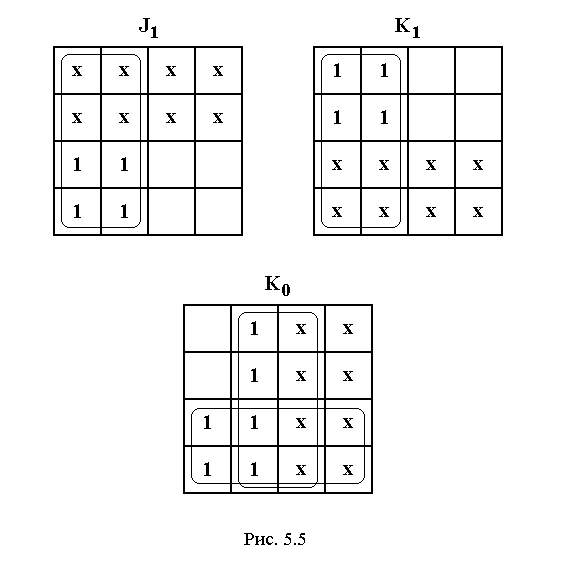

Д ля

входов J и К всех

триггеров заполняем карты Вейча и

производим объединение клеток (рис.

5.5).

ля

входов J и К всех

триггеров заполняем карты Вейча и

производим объединение клеток (рис.

5.5).

Для

![]() сейчас карту Вейча чертить не обязательно

(см. § 4.11), так как сразу по табл. 5.2 видно,

что

не содержит нулевых значений и,

следовательно, будут заполнены и

объединены все 16 клеток.

сейчас карту Вейча чертить не обязательно

(см. § 4.11), так как сразу по табл. 5.2 видно,

что

не содержит нулевых значений и,

следовательно, будут заполнены и

объединены все 16 клеток.

Записываем МДНФ для входов J и К всех триггеров:

![]() ;

; ![]() ;

; ![]() .

.

Переходим к базису И-НЕ и определяем требуемое количество элементов:

![]() ;

элементы не нужны.

;

элементы не нужны.

![]() ;

1 элемент 2И-НЕ.

;

1 элемент 2И-НЕ.

![]() ;

элементы не нужны.

;

элементы не нужны.

И еще

потребуется 1 элемент 2И-НЕ для отрицания

в логическом выражении для

![]() .

.

Записываем логические выражения для микрокоманд Y в виде отдельных многочленов СДНФ:

![]() ;

;

![]() ;

; ![]() .

.

Переходим к базису И-НЕ и определяем требуемое количество элементов.

Поскольку здесь каждое логическое выражение содержит только один многочлен, то переход к базису И-НЕ проще производить так, так мы делали в § 3.7, то есть проинвертируем обе части каждого выражения:

![]() ;

1 элемент 2И-НЕ.

;

1 элемент 2И-НЕ.

Аналогично выполняем переход и для остальных логических выражений:

![]() ;

1 элемент 3И-НЕ.

;

1 элемент 3И-НЕ.

![]() ;

1 элемент 2И-НЕ.

;

1 элемент 2И-НЕ.

Определяем общее количество компонентов в схеме УУ.

2 синхронных JK-триггера + 4 элемента 2И-НЕ + 1 элемент 3И-НЕ.

Подбираем микросхемы.

По одной микросхеме КР1533ТВ6, КР1533ЛА3 и КР1533ЛА4.

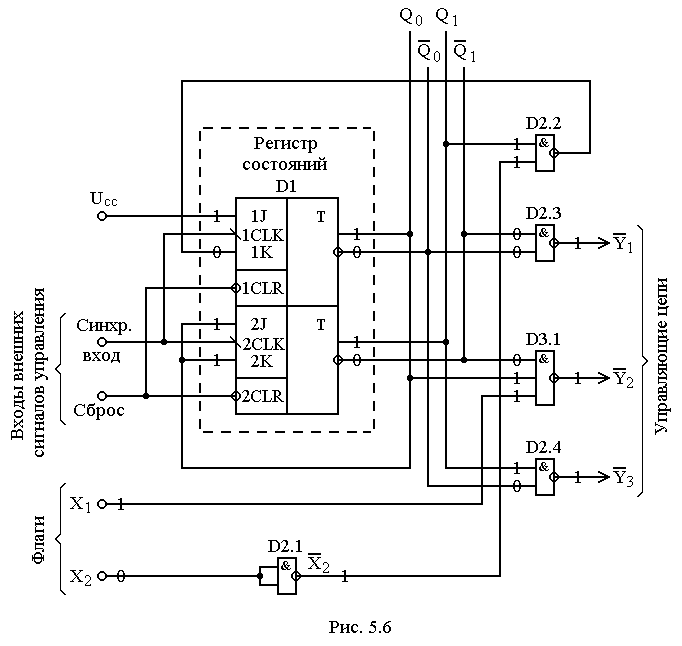

Строим

схему УУ (рис. 5.6).

Строим

схему УУ (рис. 5.6).

Составляем перечень элементов к этой схеме (табл. 5.3):

Поз. обозначение |

Наименование |

Кол. |

Примечание |

D1 |

КР1533ТВ6 |

1 |

|

D2 |

КР1533ЛА3 |

1 |

|

D3 |

КР1533ЛА4 |

1 |

2 элем. не использ. |

Рассмотрим принцип работы УУ на следующем примере: аппаратура находится в состоянии А3; Показать срабатывание УУ, которое обеспечит переход аппаратуры в состояние А1 (переход № 5 по граф-схеме переходов рис. 5.3).

16.1.

Если аппаратура находится в состоянии

А3,

то согласно таблице истинности регистра

состояний (табл. 5.1) на выходах этого

регистра удерживаются сигналы:

![]() ,

,

![]() .

Покажем их в схеме рис. 5.6.

.

Покажем их в схеме рис. 5.6.

16.2.

Согласно граф-схеме переходов (рис. 5.3)

УУ при формировании сигналов управления

для перехода № 5 должно учесть флаг

![]() (на граф-схеме -

).

В рассматриваемом переходе флаг

не учитывается, поэтому его значение

может быть любым: возьмем для определенности

(на граф-схеме -

).

В рассматриваемом переходе флаг

не учитывается, поэтому его значение

может быть любым: возьмем для определенности

![]() .

Покажем и эти значения в схеме рис. 5.6.

.

Покажем и эти значения в схеме рис. 5.6.

16.3. По схеме рис. 5.6 определяем значения сигналов в выходных управляющих цепях, а также на входах J и К всех триггеров регистра состояний.

16.4. На всех управляющих выходах Y сформировались пассивные сигналы логической 1 (все выходы – инверсные, поэтому здесь активным сигналом является 0), то есть ни на одном выходе активный сигнал 0 не появляется. Проверяем полученный результат по граф-схеме переходов (рис. 5.3): действительно, для обеспечения перехода № 5 никакой микрокоманды Y управляющее устройство вырабатывать не должно.

16.5. В определенный момент времени на синхронизирующий вход поступает очередной тактовый импульс, и от его отрицательного перепада (входы CLK триггеров – инверсные динамические, поэтому здесь активным сигналом является отрицательный перепад напряжения) срабатывают триггеры регистра состояний под действием сигналов на входах J и К:

,

.

В данном случае активный сигнал 1

действует на входе J

(это вход установки), поэтому на прямом

выходе

этого триггера устанавливается 1.

.

В данном случае активный сигнал 1

действует на входе J

(это вход установки), поэтому на прямом

выходе

этого триггера устанавливается 1.

,

,

.

Здесь активные сигналы действуют на

оба входа, поэтому (см. пункт 2 из § 4.3)

триггер переключается в другое состояние,

то есть на его выходе

вместо 1

устанавливается 0.

.

Здесь активные сигналы действуют на

оба входа, поэтому (см. пункт 2 из § 4.3)

триггер переключается в другое состояние,

то есть на его выходе

вместо 1

устанавливается 0.

16.6.

В результате срабатывания на выходах

триггеров регистра состояний

устанавливаются сигналы:

![]() ,

.

Согласно таблице истинности этого

регистра (табл. 5.1) указанные сигналы

соответствуют состоянию А1.

Полученный результат проверяем по

граф-схеме переходов: действительно,

переход № 5 идет в состояние А1.

,

.

Согласно таблице истинности этого

регистра (табл. 5.1) указанные сигналы

соответствуют состоянию А1.

Полученный результат проверяем по

граф-схеме переходов: действительно,

переход № 5 идет в состояние А1.

Вывод: Для обеспечения аппаратуры из состояния А3 в состояние А1 управляющее устройство сработало правильно.

Контрольные вопросы:

Принципы подхода к проектированию систем управления. Особенности построения и функционирования систем управления со схемной и программируемой логикой.

Что такое микрооперация, микрокоманда, микропрограмма?

В чем заключается смысл термина "флаг"?

Тестовые вопросы

Указать основное назначение ЗУ (запоминающего устройства).

Хранить более одного кодового слова

Подключать свой информационный вход к любому из выходов

Использование в качестве делителя частоты импульсной последовательности

Подсчет поступающих на его счетный вход цифровых сигналов

Как называется ЗУ, в котором хранящаяся информация непрерывно обновляется в процессе работы?

ОЗУ (оперативное запоминающее устройство)

МПЗУ (масочное постоянное запоминающее устройство)

РПЗУ ЭС (репрограммируемое постоянное запоминающее устройство с электрическим стиранием информации)

ППЗУ (программируемое постоянное запоминающее устройство)

The glossary

Қазақша |

Орысша |

Ағылшынша |

Граф-схема |

|

flowgraph

|

|

буферное устройство |

buffer unit |

|

вход выбора режима работы (чтение/запись) - |

WR/RD (write/read)

|

Задание для СРС

1. УУ с программируемой логикой.Л.1, стр.159.

Задание для СРСП

По индивидуальному заданию выполнить синтез и анализ работы УУ со схемной логикой.