- •Содержание

- •Раздел 1. Технологические основы автоматизации машиностроительной промышленности 2

- •Раздел 2. Автоматические системы 42

- •Раздел 3. Основы цифровой электроники 58

- •Раздел 1. Технологические основы автоматизации машиностроительной промышленности Введение

- •1.1 Принципы технической политики автоматизации машиностроительного производства

- •1.2 Социальные последствия автоматизации производства

- •1.3 Основные положения, понятия и определения автоматизации как науки

- •1.4 Технологический процесс автоматизированного производства

- •1.4.1. Технологичность конструкций изделий для условий автоматизированного производства

- •1.4.2. Элементы автоматизированного технологического процесса

- •1.4.3. Характеристики технологических процессов автоматизированного производства

- •1.4.4. Этапы и методологические особенности проектирования автоматизированного технологического процесса

- •Раздел 2. Автоматические системы

- •2.1 Управление технологическими объектами и его виды

- •2.2 Системы автоматизации и управления.

- •Одноуровневая децентрализованная система.

- •Одноуровневая централизованная система.

- •Многоуровневая система.

- •2.3 Системы автоматического контроля (сак)

- •2.4 Системы автоматической защиты (саз)

- •2.5 Системы автоматической блокировки

- •2.6 Системы автоматического регулирования (сар)

- •2.7 Системы автоматического управления

- •Многоканальная цифровая сау с аналоговыми контурами управления.

- •Многоканальная цифровая сау с цифровыми контурами

- •Дискретная сау

- •Раздел 3. Основы цифровой электроники

- •3.1 Базовые логические схемы

- •1. Инвертор

- •3.2 Шифраторы

- •2. Приоритетные шифраторы.

- •3.3 Дешифраторы

- •3.4 Мультиплексоры

- •3.5 Демультиплексоры

- •3.6 Сумматоры

- •3.7 Триггеры.

- •3.8 Счетчики.

- •3.9 Регистры

- •3.10 Устройства памяти.

- •3.11 Аналого – цифровое и цифро – аналоговое преобразование

3.9 Регистры

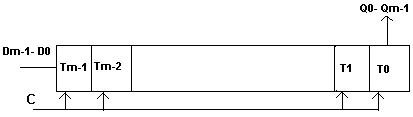

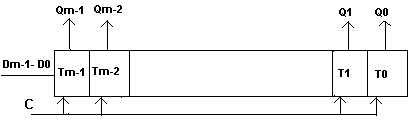

Регистром называется функциональный узел, выполняющий хранение двоичных чисел или их сдвиг на определенное число разрядов. Они строятся на основе рассмотренных выше триггеров. По способу приема и выдачи информации регистры делятся на следующие группы: с параллельным приемом и выдачей (рис. 3.17); с последовательным приемом и выдачей (рис.3.18); с последовательным приемом и параллельной выдачей (рис.3.19); с параллельным приемом и последовательной выдачей (рис.3.20).

Рис.3.17. Регистр с параллельным приемом и выдачей

Рис.3.18. Регистр с последовательным приемом и выдачей

Рис.3.19. Регистр с последовательным приемом и параллельной выдачей

Рис.3.20. Регистр с параллельным приемом и последовательной выдачей

Регистры с параллельным приемом и выдачей служат для хранения информации и называются регистрами памяти. Изменение хранящейся информации (ввод новой информации) происходит после соответствующего изменения сигналов на входах при поступлении определенного уровня(С = 0 или С=1) или фронта синхросигналов. В качестве разрядов регистра памяти используются синхронизируемые уровнем или фронтом триггеры: D- триггеры

Регистры с последовательным приемом или выдачей информации (рис. 3.18-3.20) называются сдвиговыми регистрами. В регистре с последовательными приемом и выдачей первый разряд вводимого числа D0 подается на вход одного, крайнего слева, разряда регистра Tm-1 и вводится в него при поступлении первого синхроимпульса: Qm-1=D0. При поступлении следующего синхроимпульса значение D0, поступающее с выхода разряда Tm-1, вводится в разряд Tm-2, т.е. устанавливается Qm-2=D0, в разряд Tm-1 поступает следующий разряд числа D1: устанавливается Qm-1=D1 и т.д. Таким образом, производится последовательный сдвиг поступающей на вход информации на один разряд вправо в каждом такте синхросигналов. После поступления m синхроимпульсов весь регистр оказывается заполненным разрядами числа D и первый разряд числа (D0) появляется на выходе Q0 регистра. В течение последующих m синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным.

Сдвиговые регистры обычно реализуются на D- триггерах (рис.3.22) или RS- триггерах (рис.3.23), где для ввода информации в первый разряд включается инвертор.

Рис.3.22.Схема сдвигового регистра на D- триггерах

Для сдвиговых регистров обязательным является применение триггеров, синхронизируемых фронтом.

Сдвиговые регистры могут быть реверсивными, т.е. выполняющими сдвиг в любом направлении: слева направо или наоборот. Направление сдвига определяется значением управляющего сигнала на специальном входе регистра.

Условное графическое изображение регистра показано на рис.3.24.

Рис.3.24. Схематическое изображение регистра

3.10 Устройства памяти.

Назначение, основные параметры и классификация.

Для кратковременного хранения небольших объемов кодовых слов обычно используют регистры. При необходимости длительного хранения или хранения больших объемов информации применяют запоминающие устройства (ЗУ), выполненные на специализированных ИС. Применение ЗУ, использующих ИС, позволяет максимально упростить аппаратную часть электронных устройств. Любое ЗУ, не зависимо от его выполнения и назначения, характеризуется рядом параметров. Рассмотрим основные из них.

Емкость ЗУ (М) определяет максимально возможный объем хранимой в нем информации.

Динамические характеристики ЗУ в общем случае определяются большим числом различных временных параметров, основными среди которых являются времена выборки (обращения) циклов адреса в режимах чтения и записи

Временем выборки 1л называется временной интервал между подачей на вход памяти заданного сигнала и получением на выходе данных при условии, что все остальные сигналы поданы.

Временем цикла адреса в режиме записи называет минимальное время совпадения сигналов на управляющих входах памяти, необходимое для надежной записи в нее информации.

По выполняемой функции ЗУ можно классифицировать на оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ).

К оперативным относят ЗУ, использующиеся для хранения информации, получаемой в процессе работы устройства и обеспечивающие соизмеримые времена ее считывания и записи.

Оперативные ЗУ могут быть выполнены как статическими, так и динамическими. В статических ОЗУ записанная информация постоянно хранится в выделенном для нее месте и не разрушается при ее считывании Разрушение информации возможно только при ее принудительном стирании или отключении напряжения источника питания

В динамических ОЗУ информация постоянно циркулирует в массиве, отведенном для ее хранения При этом считывание информации сопровождается ее разрушением. Для сохранения информации ее необходимо перезаписать заново.

Основным требованием, предъявляемым к ОЗУ, является обеспечение максимально возможного быстродействия при заданных объеме и организации.

Для обозначения на принципиальных электрических схемах ИС озу используется сокращение RAM (random access memory).

Постоянные ЗУ предназначены для хранения информации, остающейся неизменной в течение всего времени эксплуатации устройства. Обычно это либо неизменные последовательности кодов, определяющие алгоритмы, по которым функционирует устройство, либо некоторые константы, требуемые для выполнения определенных вычислений.

В зависимости от возможности записи информации ПЗУ подразделяются на три подкласса: масочные ПЗУ, программируемые ПЗУ, репрограммируемые ПЗУ.

Для обозначения на принципиальных электрических схемах ИС ПЗУ используется сокращение ROM (read only memory).

ЗУ с одномерной адресацией.

В зависимости от способа нахождения нужного элемента в массиве других однотипных элементов различают структуры с одномерной (линейной) и двумерной адресацией.

На рис. 8.1. в качестве примера приведена структурная схема ЗУ (М=16, организация 4Х4) с одномерной адресацией. Данная структура содержит матрицу 4Х4 ЭЗЭ, каждый из которых. снабжен тремя выводами: входом информации (IN), выходом информации (OFF) и выходом разрешения работы—выбора кристалла (CS—chip select), дешифратор адреса, входные и выходные ключи на элементах 2И.

Если

на вход дешифратора подано некоторое

адресное слово, на соответствующем его

выходе формируется сигнал лог. 1, который

выбирает все ЭЗЭ, расположенные в одной

из строк матрицы. Дальнейшая работа

устройства зависит от того, какой режим

работы задан управляющими сигналами.

Если подан сигнал «чтение» (![]() = 1), то информация

из выбранных ячеек подается на первые

входы выходных элементов 2И. На вторые

входы этих ключей подан единичный

(пассивный) логический сигнал. Информация,

хранившаяся в выбранных ЭЗЭ, попадает

на выходные выводы DO0,

DO1,

DO2

,

DO3.

= 1), то информация

из выбранных ячеек подается на первые

входы выходных элементов 2И. На вторые

входы этих ключей подан единичный

(пассивный) логический сигнал. Информация,

хранившаяся в выбранных ЭЗЭ, попадает

на выходные выводы DO0,

DO1,

DO2

,

DO3.

Если на схему подан сигнал «запись» ( =0), то информация с входных шин DI0, DI1, DI2 , DI3. через входные элементы 2И подается на входы ЭЗЭ и записывается в них.

Особенностью данной структурной схемы является одновременная запись и считывание информации, хранящейся в строке матрицы ЭЗЭ. Поэтому при заданной разрядности хранимого слова наращивание объема памяти может выполняться только за счет увеличения числа строк матрицы.

Рис 8.1. Структурная схема ЗУ с одномерноп адресацией

Это, в свою очередь, ведет к значительному увеличению количества выходов дешифратора, т е. к усложнению аппаратной реализации.

С точки зрения упрощения дешифратора желательно выполнять матрицу ЭЗЭ прямоугольной. Однако при использовании рассмотренной структуры это предполагает увеличение разрядности выходного слова.

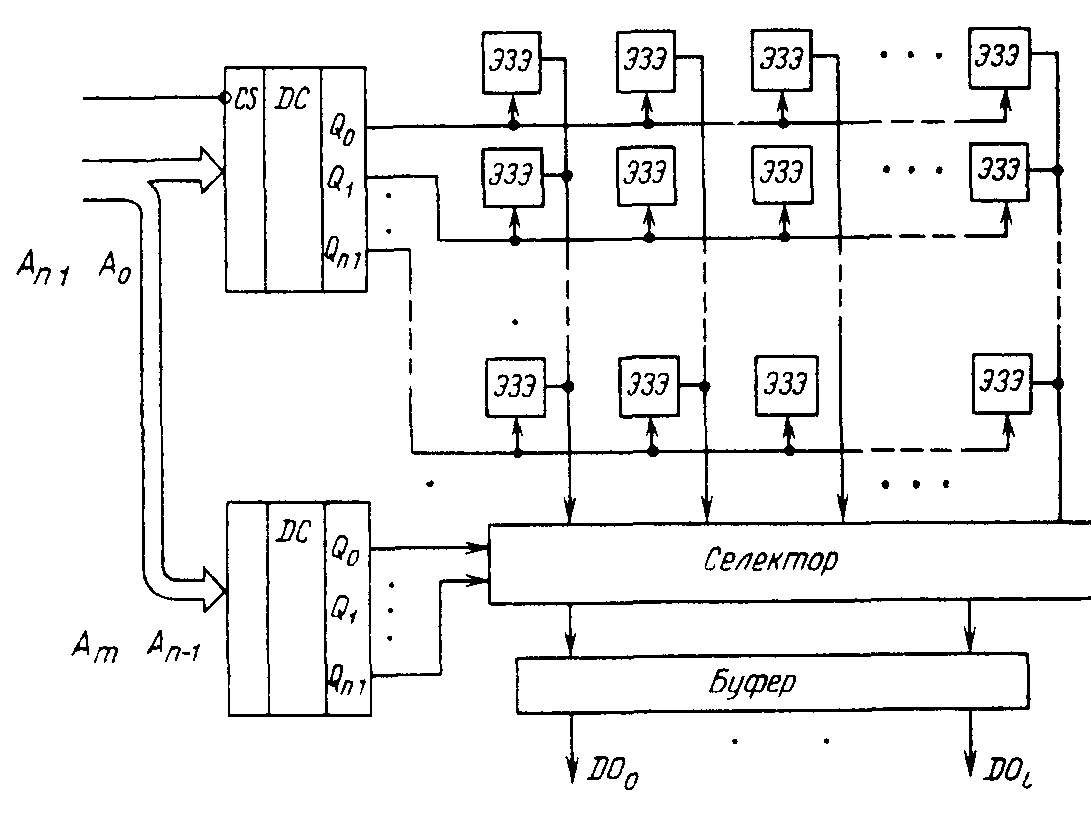

Решить это противоречие можно, если в качестве входных и выходных ключей ИС использовать соответственно схемы демультиплексоров и мультиплексоров. Применительно к ЗУ их принято называть селекторами. При этом часть разрядов адресного слова используется для управления селекторами.

ЗУ с двумерной адресацией.

При необходимости побитовой записи-считывания информации применяют структуру памяти с двумерной адресацией (рис. 8.2.).

Данная структура содержит матрицу ЭЗЭ, статический регистр адреса, дешифраторы строки и столбца, усилители записи и считывания, входной и выходной буферные триггеры.

Однако, в отличие от схемы рис. 8.1, каждый ЭЗЭ матрицы содержит не один, а два вывода разрешения работы (CS1 и CS2). При этом информационные выводы p1 и р2 являются обратимыми, т. е. позволяют как записывать так считывать информацию. Для выбора нужной ячейки на оба входа CS необходимо подать акгивные логические уровни.

Рис. 8.2. Структурная схема ЗУ с двумерной адресацией

Цепи управления матрицей ЭЗЭ обеспечивают реализацию одного из трех режимов работы:

хранения, при котором ЭЗЭ отключены от входа и выхода ИС;

чтения, при котором информация из ЭЗЭ, выбранного по соответствующему адресу, выдается на выход ИС;

записи, при которой информация со входа ИС записывается по указанному адресу.

Каждому ЭЗЭ матрицы присваивается определенный адрес, поиск которого производится указанием номеров соответствующих строки и столбца. Эти номера формируются на выходах дешифраторов. Адрес ЭЗЭ в виде двоичного числа принимается по адресной шине регистром адреса. Число разрядов регистра адреса однозначно связано с объемом памяти ИС. Число строк и столбцов матрицы ЭЗЭ обычно выбирается равным целой степени числа 2, причем общий объем памяти определяется произведением числа строк на число столбцов:

![]() ;

;

где n=n1+n2 - число разрядов регистра адреса.

так

как в этом случае организация памяти

![]() ,

то для доступа ко всей хранящейся

информации необходимо 10-разрядное

адресное слово (А9...А0),

т. е. n=10.

Если выбрать n1+n2=5,

то число строк и столбцов будет равно

32 и матрица ЭЗЭ будет квадратной.

,

то для доступа ко всей хранящейся

информации необходимо 10-разрядное

адресное слово (А9...А0),

т. е. n=10.

Если выбрать n1+n2=5,

то число строк и столбцов будет равно

32 и матрица ЭЗЭ будет квадратной.

Разряды регистра адреса делятся на две группы: одна (n1) определяет двоичный адрес строки (RA), другая (n2) —двоичный адрес столбца (СА). Каждая группа разрядов адреса подается на соответствующий дешифратор (строк и столбца). Выходные сигналы дешифраторов выбирают требуемый ЭЗЭ из матрицы.

При чтении (WR/RD=1) содержимое этой ячейки через усилитель считывания выводится в выходной триггер.

Режим записи устанавливается путём подачи в усилитель записи сигнала разрешения записи ( =0) Этот сигнал открывает усилитель записи, и бит входной информации поступает на внутреннюю шину ИС, с которой переписывается в выбранный по соответствующему адресу ЭЗЭ.

Указанные процессы считывания-записи могут осуществляться только в случае, если на вход CS, соединенный с входом стробирования дешифратора строки, подан разрешающий сигнал. Обычно это сигнал лог. 0. При отсутствии этого сигнала работа дешифратора строки блокируется, что эквивалентно запрещению выборки ЭЗЭ по указанному адресу. В этом случае ИС находится в режиме хранения информации, и ее выходы отключены от матрицы ЭЗЭ.

Рассмотренная

организация памяти обеспечивает хранение

![]() кодовых слов, т. е. заданному адресу

соответствует один бит информации.

Использование метода двумерной адресации

позволяет максимально упростить схему

ИС, что при заданной площади кристалла

является предпосылкой получения

максимально больших объемов памяти.

кодовых слов, т. е. заданному адресу

соответствует один бит информации.

Использование метода двумерной адресации

позволяет максимально упростить схему

ИС, что при заданной площади кристалла

является предпосылкой получения

максимально больших объемов памяти.

Увеличение объема памяти ЗУ.

С использованием описанных структур можно строить память с любым заданным объемом информации. Однако на практике приходится иметь дело со стандартным рядом ИС, организация и объем памяти, которых заданы. Как правило, эти показатели не совпадают с требованиями конкретной аппаратуры, и встает задача построения на ИС ЗУ заданной организации ЗУ с требуемой организацией

Рис. 8.3. Организация ЗУ при наращивании разрядности выходного слова |

Рис. 8.4. Организация ЗУ при наращивании числа хранимых слов слова

|

Для этой цели используются два технических решения: наращивание разрядности хранимых слов; наращивание числа хранимых слов. Используя одновременно оба этих метода, можно увеличить как разрядность, так и количество хранимой информации.

Увеличить

разрядность хранимых в памяти слов

можно параллельным включением нескольких

одинаковых ИС. На рис. 8.3. показано

построение ЗУ с организацией

![]() бит на основе ИС с организацией

.

Для этого один и тот же адрес необходимо

подать одновременно на адресные входы

4-х ИС. С выхода D0

каждой ИС по указанному адресу будет

считан 1 бит информации. Следовательно,

подключив выходы ИС к соответствующим

разрядам 4-х разрядной шины, с последней

можно считать 4-х разрядное слово. Таким

образом, наращивание разрядности

хранимых информационных слов не требует

применения дополнительных технических

средств и может быть выполнено простым

соединением имеющихся ИС.

бит на основе ИС с организацией

.

Для этого один и тот же адрес необходимо

подать одновременно на адресные входы

4-х ИС. С выхода D0

каждой ИС по указанному адресу будет

считан 1 бит информации. Следовательно,

подключив выходы ИС к соответствующим

разрядам 4-х разрядной шины, с последней

можно считать 4-х разрядное слово. Таким

образом, наращивание разрядности

хранимых информационных слов не требует

применения дополнительных технических

средств и может быть выполнено простым

соединением имеющихся ИС.

Сложнее обстоит дело при необходимости увеличения количества хранимых в памяти слов. Ранее отмечалось, что количество хранимых в памяти кодовых слов однозначно связано с разрядностью используемого адресного слова. Поэтому его увеличение требует увеличения разрядности шины адреса. Однако, так как разрядность адресного слова для конкретного типа ИС задана, решить эту задачу без привлечения дополнительных аппаратных средств не представляется возможным.

Практически

задача увеличения количества хранимых

слов решается с использованием

дополнительного дешифратора,

предназначенного для формирования

сигнала разрешения работы нескольким

параллельно включенным по выходам ИС.

Данное решение иллюстрируется рис. 8.4.

на котором показано выполнение памяти

![]() на основе ИС с собственной организацией

.

Для обращения к объему памяти в 4К

необходимо 12-разрядное адресное слово.

Интегральная схема заданного типа

управляется 10-разрядным адресным словом.

Два старших разряда адреса А11 и А10

подаются на адресные входы дополнительного

дешифратора, выходы которого подсоединены

к входам

на основе ИС с собственной организацией

.

Для обращения к объему памяти в 4К

необходимо 12-разрядное адресное слово.

Интегральная схема заданного типа

управляется 10-разрядным адресным словом.

Два старших разряда адреса А11 и А10

подаются на адресные входы дополнительного

дешифратора, выходы которого подсоединены

к входам

![]() соответствующих ИС. Поэтому при подаче

адреса дешифратор старших разрядов из

четырех ИС выберет только ту, в которой

хранится нужная информация. Выходы

остальных ИС будут отключены от выходной

шины данных, с которой будет считана

только соответствующая поданному адресу

информация.

соответствующих ИС. Поэтому при подаче

адреса дешифратор старших разрядов из

четырех ИС выберет только ту, в которой

хранится нужная информация. Выходы

остальных ИС будут отключены от выходной

шины данных, с которой будет считана

только соответствующая поданному адресу

информация.

Постоянные ЗУ (ПЗУ).

Постоянные ЗУ предназначены для хранения информации которая остается неизменной в течение всего времени работы устройства. Эта информация не исчезает при снятии напряжения питания.

Поэтому в ПЗУ возможен только режим считывания информации, причем считывание не сопровождается ее разрушением.

Класс ПЗУ не однороден и, как отмечалось ранее, может быть разбит на несколько самостоятельных подклассов. Однако все эти подклассы используют один и тот же принцип представления информации. Информация в ПЗУ представляется в виде наличия или отсутствия соединения между шинами адреса (ША) и данных. В этом смысле ЭЗЭ ПЗУ подобен ЭЗЭ динамического ОЗУ, в котором конденсатор памяти Сп либо закорочен, либо исключен из схемы.

Проиллюстрируем

этот принцип на простом примере. На рис.

21.13 приведена схема простейшего ПЗУ с

организацией 4х8. Она включает дешифратор

с двумя адресными шинами, восемь

балластных резисторов

![]() выходных шин и диоды, число которых

равно числу лог. 1 в информационных

словах, записанных в ПЗУ.

выходных шин и диоды, число которых

равно числу лог. 1 в информационных

словах, записанных в ПЗУ.

Работа ПЗУ сводится к следующему. После появления на выходе дешифратора напряжения высокого уровня при наличии связи через диод между ША и ШД, это напряжение прикладывается к соответствующему балластному резистору, что в положительной логике воспринимается как появление на шине сигнала лог. 1. При отсутствии связи ток через соответствующий резистор не протекает, что при тех же допущениях классифицируется как сигнал лог 0. Информация, записанная таким образом в ПЗУ рис. 21.13, соответствует следующей таблице истинности (табл. 21.1).

В зависимости от типа и способа организации связи между шинами адреса и данных все ПЗУ могут быть разбиты на три подкласса: масочные; прожигаемые (программируемые); репрограммируемые.

Таблица истинности ПЗУ |

|||||||||

А1

|

А0

|

DO0

|

DO1

|

DO2

|

DО3

|

DO4

|

DO5

|

DO6

|

DO7

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

Следует отметить, что ПЗУ хранят информацию в виде многоразрядных слов и поэтому их структура строится по принципу одномерной адресации. При этом, если разрядность хранимого в ПЗУ информационного слова превышает разрядность необходимого выходного слова, на выходе матрицы ЭЗЭ используются дополнительные селекторы выходного слова. Рассмотрим подробнее перечисленные подклассы ПЗУ.

Масочные ПЗУ.

Масочные ПЗУ. К масочным относятся ПЗУ, информация в которые записывается непосредственно в процессе их изготовления. Само название данного подкласса устройств связано с технологическим процессом их изготовления. Известно, что нанесение «рисунка» структуры на исходный полупроводниковый материал выполняется при помощи нескольких последовательных циклов фотолитографии (проецирование рисунка через фотошаблон называемый маской) При этом отдельные элементы формируемых полупроводниковых приборов выполняются с использованием различных масок, например, коллекторные и эмиттерные переходы биполярных или выводы стока и истока полевых транзисторов.

Первоначально изготавливаются все фотошаблоны, обеспечивающие соединение всех ША с ШД. В этом случае по всем адресам из ПЗУ считывается одинаковый сигнал, например лог. 1. Далее один из шаблонов заменяют другим, в котором отсутствуют некоторые области приборов (например, коллекторные переходы транзисторов), расположенные согласно таблице истинности между шинами в тех местах, где соединение должно отсутствовать. Данный метод позволяет для изготовления ПЗУ с различной информацией заменять только один из фотошаблонов, что существенно ускоряет и удешевляет процесс производства.

Как следует из описания, масочные ПЗУ имеют простую и регулярную структуру, что предполагает выполнение ИС, способных хранить большие объемы информации.

Прожигаемые ПЗУ.

Прожигаемые ПЗУ, или однократно программируемые ПЗУ, относятся к классу устройств, которые программируются один раз непосредственно их потребителем. По своей структурной схеме это устройство с одномерной адресацией, в котором для выделения выходного информационного слова нужной длины используется выходной селектор (рис 9.1.).

Первоначально по всем адресам таких ИС записаны сигналы либо лог. 0, либо лог. 1. Пользователь по своему усмотрению перезаписывает по необходимым адерсам отличные от исходных логические константы. Физически процесс записи осуществляется путем разрушения (пережигания) специально для этого предусмотренных перемычек между шинами дешифрированного адреса и выходными выводами. Такие перемычки изготавливаются из нихрома, поликремния или титаната вольфрама и имеют собственное сопротивление в несколько десятков ом Перемычка обычно включается в эмиттерную цепь транзистора. При программировании для разрушения такой перемычки через транзистор достаточно пропустить импульс тока в 20 .. 30 мА при длительности порядка 1 мс.

В нормальном режиме работы токи схемы существенно меньше необходимых для программирования. Поэтому записанная в ЭЗЭ информация при чтении не разрушается.

Рис 9.1. Структурная схема прожигаемого ПЗУ

Импульс тока записи формируется путем кратковременного повышения напряжения питания ЭЗЭ до необходимого для прожи-гания перемычки значения Очевидно, что записанная таким образом информация не может быть изменена, за исключением случаев, в которых необходимо изменить информацию по ранее незапрограммированным адресам.

Репрограммируемые ПЗУ.

Отличаются от вышеперечисленных возможностью многократной записи и стирания информации. К таким ПЗУ относятся и современные флеш-карты.