- •“Вычислительная техника”

- •Триггеры: асинхронные, синхронные, одноступенчатые, двухступенчатые rs-, т-, d-, jk-триггеры. Схемы, уго, переключательные таблицы, временные диаграммы.

- •[Править] т-триггер асинхронный

- •Функции.

- •Назначение входов и выходов.

- •29.Защита рэа от механических воздействий. Виды механических нагрузок. Причины мех. Разрушения. Различия м/у понятиями виброустойчивости и вибропрочности.

- •1)Стадии разработки конструкторской документации (кд). Виды работ, выполняемые на каждой стадии.

- •32.Определение эргономики. Структура эргономики как науки.Инженерная психология. Система чпс.Латентный период

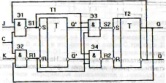

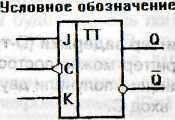

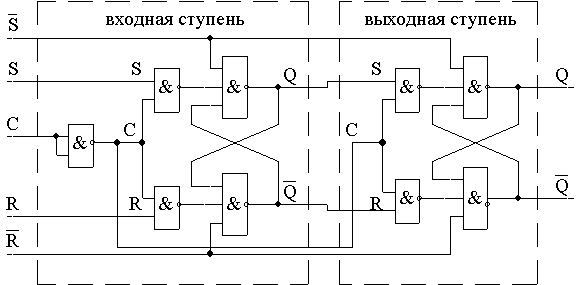

№9 Двухступенчатый синхронный jk-триггер.

JK-триггер может иметь статические или динамические входы. Может быть синхронным и асинхронным.

JK-триггер - универсальный триггер, так как он может работать как любой тип триггеров: RS, Т, D. JK-триггер не имеет запрещенных комбинаций. Наибольшее распространение получили двухтактные синхронные JK-триггеры. Логическая структура

Логическая структура включает два RS-триггера с инверсными входами и четыре элемента И-НЕ.

Допустим, что триггер Т1 находится в единичном состоянии при отсутствии синхросигнала С=0, тогда S=1, R=1, эти сигналы удерживают триггер в исходном состоянии Q'=1.

При Q'=1, S1=1, R1=1 на выходе элементов ЭЗ, Э4 - S2=0, R2=1, которые устанавливают триггер Т2 в состояние Q=1. При С=0 как бы ни менялась информация, на входах J и К триггер, будет сохранять состояние Q=1.

Подадим импульс, на входе триггера Т1 С=1, если J=0, К=0, то S=1, R=1 -состояние триггера не.меняется.

При С=1, Q' =1, J=0, К=1 на выходе элементов Э1 и Э2: S1=1, R1=0, Q'=0, на

выходе элементов ЭЗ и Э4: S2=1, R2=1 - состояние триггера Т2 не изменяется. По

окончании действия синхроимпульса С=0 на выходе элементов Э1 и Э2: S1=1, R1=1

триггер Т1 останется в исходном состоянии, на выходе элементов ЭЗ и Э4: S2=1, R2=0,

триггер Т2 установится в состояние Q=Q.

При С=1, Q' =0, J=1, К=0 на входе элементов Э1 и Э2: S1=0, Ri=1, Q'=1, на выходе элементов ЭЗ и Э4: S2=1, R2=1 - состояние триггера Т2 не меняется.

По окончанию действия синхроимпульса С=0 на выходе элементов Э1 и Э2: S1=1, R1=1 триггер Т1 остается в исходном состояние, на выходе элементов ЭЗ и Э4: S2=0, R1=0, триггер Т2 устанавливается в состояние Q=1, т.е. переключается в инверсное состояние.

При С1 , Q' =0, J=1, К=1 на выходе элементов Э1 и Э2: S1=0, R1=1, Q'=0, на выходе элементов ЭЗ и Э4: S2=1, R2=1 - состояние триггера Т2 не меняется.

По окончанию действия синхроимпульса С=0 на выходе элементов Э1 иЭ2 S1=1, R1=1 триггер Т1 остается в исходном состояние, на выходе элементов ЭЗ и Э4 . , S2=0, R1=0, триггер Т2 устанавливается в состояние Q=1, т.е.переключается в инверсное состояние.

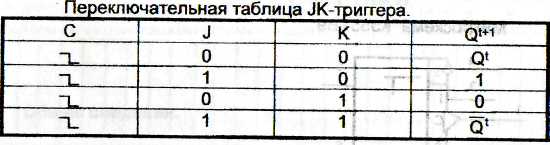

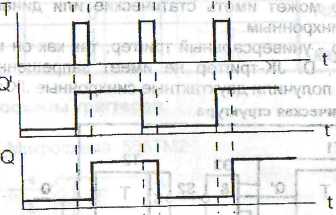

№8 Двухступенчатый D-триггер.

При

подаче на D

единицы

,

и при

,

и при

на выходе

на выходе

устанавливается единица. При этом на

входе С триггера

устанавливается единица. При этом на

входе С триггера

ноль. Он информацию не принимает. По

окончанию синхроимпульса на входе С

триггера

единица и он принимает информацию

ноль. Он информацию не принимает. По

окончанию синхроимпульса на входе С

триггера

единица и он принимает информацию

и

устанавливается в состояние 1. Если

,

то

и по срезу синхроимпульса на выходе

триггера устанавливается 0. Таким

образом, D

триггер записывает тоже состояние , что

и на входе D,

но с задержкой.

и

устанавливается в состояние 1. Если

,

то

и по срезу синхроимпульса на выходе

триггера устанавливается 0. Таким

образом, D

триггер записывает тоже состояние , что

и на входе D,

но с задержкой.

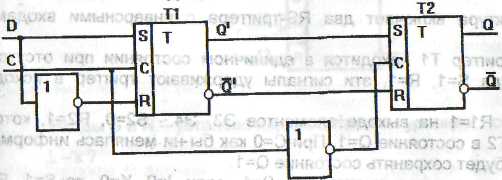

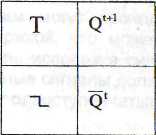

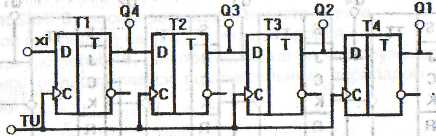

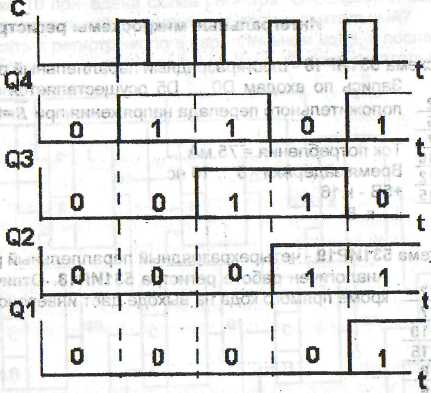

№7 Двухступенчатый Т-триггер.

При

подаче на вход триггера T

единицы, то

принимает информацию, поступившую на

его входы.

При

этом на входе С триггера

ноль, он информацию не принимает . По

окончанию синхроимпульса на

ноль. Триггер

информацию не принимает, на входе С

триггера

единица.

Триггер переключается в инверсное

состояние. С выходов триггера информация

поступает на входы триггеров

.

Поэтому если им подать следующий счетный

импульс, то триггер опять переключится.

Таким образом, триггер по срезу

переключается в инверсное состояние.

.

Поэтому если им подать следующий счетный

импульс, то триггер опять переключится.

Таким образом, триггер по срезу

переключается в инверсное состояние.

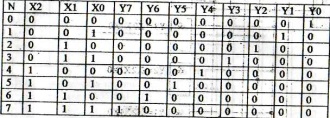

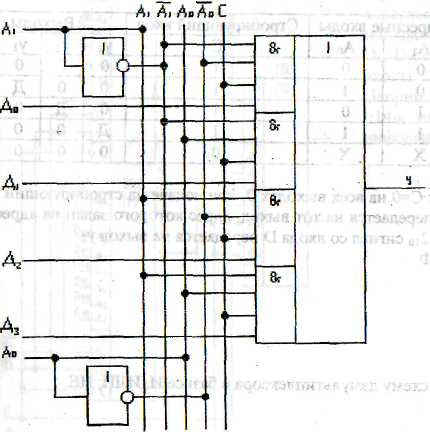

№10 Линейный дешифратор.

Дешифратором называется цифровое устройство ,в котором каждой комбинации входных сигналов соответствует наличие сигнала на определенном выходе. Дешифраторы применяются для сопряжения с цифровыми системами ,в преобразователях кодов, например, |двоичного кода в десятичный. Если дешифратор имеет n входов (разрядов) и 2n выходов,то он называется полным.

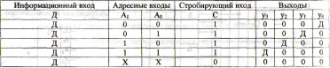

Синтез линейного дешифратора с числом входов п=3. Таблица истинности

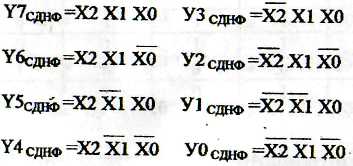

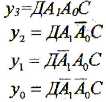

Запишем СДНФ

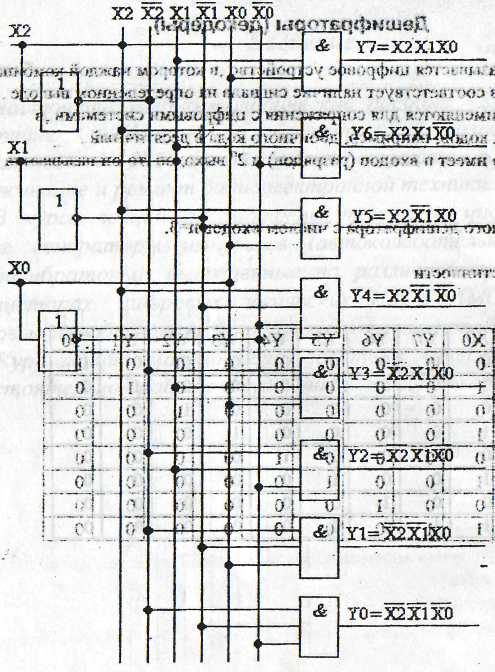

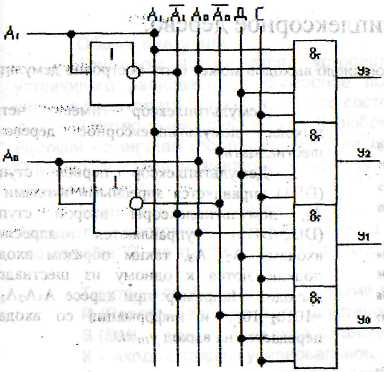

Построим схему дешифратор в базисе И, ИЛИ, НЕ по полученным выражениям

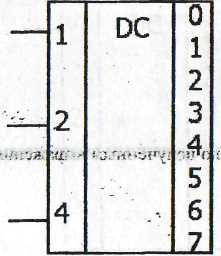

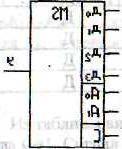

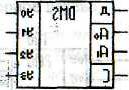

Обозначение дешифратора в схеме

№14 Мультиплексор.

Мультиплексор имеет n адресных входов (А), 2n информационных входов (Д), стро-бирующий вход С и один выход у.

Мультиплексор - коммутатор, в котором каждому информационному входу присвоен номер (адрес). Мультиплексор выбирает один из информационных входов, адрес которого задан двоичным кодом на адресных входах и подключает его к выходу при наличии строби-рующего сигнала на входе С.

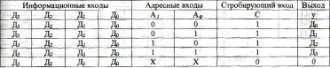

Таблица функционирования мультиплексора, имеющего два адресных входа и четыре -информационных входа.

Из таблицы видно, что при С=0 на выходе 0, при подаче на стробирующий вход сигнала С=1 на выход передается информация с того информационного входа, адрес которого задан на адресных входах, например: при A1Ao=102=210 на выход передается информация со входа Д2.

По таблице запишем СДНФ.

![]()

По выражению построим схему мультиплексора в базисе И, ИЛИ, НЕ-

Условное графическое, изображение мультиплексора

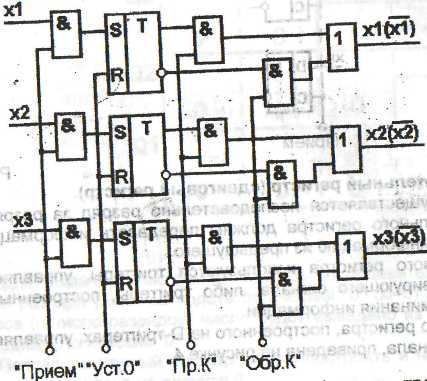

№18 Параллельный регистр.

Ввод и вывод информации осуществляется параллельно.

Можно построить на любом типе триггеров, кроме триггера Т.

Запись числа:

1) Обнуление: путем подачи 1 на вход установки 0

2) Подать 1 на ПРИЕМ и подать число на входы.

3) Считывание числа: Чтобы получить число в ПР входе нужно: на шину ПРЯМОЙ подать 1, а на шину обратной код – 0.

Чтобы получить число в обратном коде, необходимо на шину ОБР. подать 1, на шину ПРЯМОЙ КОД – 0

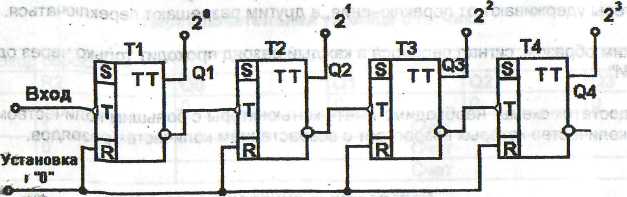

№17 Асинхронный вычитающий двоичный счетчик.

Асинхронный вычитающий двоичный счетчик.

Чтобы записать в счетчик число из которого будет вычитать, нужно сначало его обнулить, а затем по входам S нужно записать необходимое нам число.

1010=5

0100=4

Предворительно счетчик обнулили, подав 1 на шину установки нуля. Затем по входам S записываем число 5 – верхняя строчка. Подадим первый счетный импульс, по его срезу Т1 переключиться в инверсное состояние 0. На инверсном выходе триггера сформировался перепад 0/1 – фронт, который поступает на вход Т второго триггера. Второй триггер не переключается. В счетчике записано 4 – вторая строчка.

Подадим второй счетный импульс. По его срезу Т1 переключиться в инверсное состояние 1, на инверсном выходе сформировался перепад с 1/0 – срез, Т2 – переключиться в инверсное состояние 1.На инверсном выходе сформировался перепад с 1/0 – срез, Т3 перекллючиться в инверсное состояние – 0. На инверсном выходе сформируется перепад 0/1 – фронт, Т4 – не переключиться.

В счетчике записано число 3.

№15 Демультиплексор.

Демультиплексор имеет n адресных входов, один информационный вход D, строби-рующий вход С и 2n выходов.

Демультиплексор - коммутатор, в котором каждому выходу присвоен номер (адрес). Демультиплексор выбирает один из выходов, адрес которого задан двоичным кодом на адресных входах и подключает его ко входу при наличии стробирующего сигнала на входе С.

Таблица функционирования демулътиппексора, имеющего два адресных входа.

Из таблицы видно, что при С=0 на всех выходах 0, при подаче на cnробирующий вход сигнала С=1. Сигнал со входа D передается на тот выход, адрес которого задан на адресных входах, например: при A1A0=102=210 сигнал со входа D передается на выходу.

По таблице запишем СДНФ.

По выражениям построим схему демультиплексора в базисе И, ИЛИ, НЕ.

Условное графическое изображение демультитексора

№19 Последовательный регистр.

Вход и выход числа осуществляется последовательно.

Триггеры в регистре должны принимать информацию с предыдущих и передоваться в последующие.

Будем записывать число начиная с младшего разряда.

После действия первого тактового импульса старший разряд регистр записывает в младший разряд числа. Подадим второй тактовый импульс и второй разряд числа.

После действия второго тактового импульса число сдвигается на один разряд вправо. В регистре теперь уже записано два разряда числа. Подадим следующий разряд числа и третий тактовый импульс.

После действия третьего тактового импульса все разряды числа записаны.Числа записаны в соответствующих разрядах регистра. Чтобы считать число нужно подать на Xn-0, а на не Xn- 1. И после действия трех тактовых импульсов регистр очиститься.

“Вычислительная техника”

Триггеры: асинхронные, синхронные, одноступенчатые, двухступенчатые rs-, т-, d-, jk-триггеры. Схемы, уго, переключательные таблицы, временные диаграммы.

Т риггер

- это устройство, обладающее двумя

состояниями устойчивого равновесия.

Триггер еще можно назвать устройством

с обратными связями. На рисунке изображена

схема триггера на логических элементах

ИЛИ-НЕ.

риггер

- это устройство, обладающее двумя

состояниями устойчивого равновесия.

Триггер еще можно назвать устройством

с обратными связями. На рисунке изображена

схема триггера на логических элементах

ИЛИ-НЕ.

Рис. 1 Схема простейшего RS-триггера

Т акая

схема называется асинхронным RS-триггером.

акая

схема называется асинхронным RS-триггером.

S |

R |

Q(t) |

Q(t) |

Q(t+1) |

Q(t+1) |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

ервый

(сверху) выход называется прямым, второй

- инверсным. Если на оба входа (R и S) подать

лог. нули, то состояние выходов определить

невозможно. Триггер установится как

ему заблагорассудится, т. е. в произвольное

состояние. Допустим, на выходе Q

присутствует лог. 1, тогда на выходе не

Q (Q с инверсией) обязательно будет лог.

0. И наоборот. Чтобы установить триггер

в нулевое состояние (когда на прямом

выходе лог. 0, на инверсном - лог. 1)

достаточно на вход R подать напряжение

высокого уровня (про уровни напряжений

здесь).

Если высокий уровень подать на вход S,

то это переведет его в состояние 1, или

как говорят, в единичное состояние (на

прямом выходе лог. 1, на инверсном - лог.

0). И в том, и в другом случаях напряжение

соответствующего уровня может быть

очень коротким импульсом - на грани

физического быстродействия микросхемы.

То есть, триггер обладает двумя устоячивыми

состояниями, причем эти состояния

зависят от ранее воздействующих сигналов,

что позволяет сделать следующий вывод

- триггер является

простейшим элементом памяти.

Буквы R и S по-буржуйски set - установка,

reset - сброс (предустановка). На рис. 2

RS-триггер показан в "микросхемном

исполнении".

ервый

(сверху) выход называется прямым, второй

- инверсным. Если на оба входа (R и S) подать

лог. нули, то состояние выходов определить

невозможно. Триггер установится как

ему заблагорассудится, т. е. в произвольное

состояние. Допустим, на выходе Q

присутствует лог. 1, тогда на выходе не

Q (Q с инверсией) обязательно будет лог.

0. И наоборот. Чтобы установить триггер

в нулевое состояние (когда на прямом

выходе лог. 0, на инверсном - лог. 1)

достаточно на вход R подать напряжение

высокого уровня (про уровни напряжений

здесь).

Если высокий уровень подать на вход S,

то это переведет его в состояние 1, или

как говорят, в единичное состояние (на

прямом выходе лог. 1, на инверсном - лог.

0). И в том, и в другом случаях напряжение

соответствующего уровня может быть

очень коротким импульсом - на грани

физического быстродействия микросхемы.

То есть, триггер обладает двумя устоячивыми

состояниями, причем эти состояния

зависят от ранее воздействующих сигналов,

что позволяет сделать следующий вывод

- триггер является

простейшим элементом памяти.

Буквы R и S по-буржуйски set - установка,

reset - сброс (предустановка). На рис. 2

RS-триггер показан в "микросхемном

исполнении".

RS-триггер можно соорудить и на элементах И-НЕ, как показано на рисунке 3. Такая конструкция встречается довольно часто.

Рис. 3 RS-триггер на логических элементах И-НЕ

Принцип работы такой же, как у триггера на элементах ИЛИ-НЕ, за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

Если схему асинхронного триггера немного дополнить, то получим вот такое:

Р ис.

4 Синхронный RS-триггер на логических

элементах И-НЕ

ис.

4 Синхронный RS-триггер на логических

элементах И-НЕ

C |

S |

R |

Q(t) |

Q(t+1) |

0 |

x |

x |

0 |

0 |

1 |

1 |

|||

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

не определено |

1 |

1 |

1 |

1 |

не определено |

Алгоритм функционирования синхронного RS-триггера можно представить формулой

![]()

где x — неопределённое состояние.

В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов лог. 1 на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными.

RS-триггер

двухступенчатый со сложной логикой

RS-триггер

двухступенчатый со сложной логикой

D-триггер

D-триггеры также называют триггерами данных, так как на них строятся регистры данных.

D -триггер

отличается от синхронного RS-триггера

тем, что у него только один информационный

вход D. D-триггер показан на рисунке 5.

-триггер

отличается от синхронного RS-триггера

тем, что у него только один информационный

вход D. D-триггер показан на рисунке 5.

Рис. 5 D-триггер на логических элементах И-НЕ

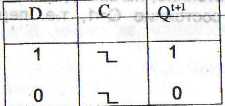

D |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится лог. 1. Если на вход D подать лог. 0, на С импульс, то на Q установится лог. 0. Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был лог. 0, то станет лог. 1. При следующем импульсе триггер снова переключится, т. е. лог. 1 сменится лог. 0. Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетным или Т-триггером. Этот режим (режим деления частоты) используется довольно широко.

Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2.