- •Звіти до лабораторних робіт № 1 - 3 «Проектування комп’ютерних систем та мереж»

- •Сапр Xilinx WebPack

- •Імплементування vhdl моделей операційного та керуючого пристроїв (автоматів)

- •Автомат Мура

- •Імплементування vhdl моделей двохнаправленої шини та lvds шини

- •Шина lvds

- •Синтез та дослідження dll/dcm тактування проектів на пліс

Синтез та дослідження dll/dcm тактування проектів на пліс

Мета: Опанувати технікою тактування поектів на ПЛІС

Завдання:

В САПР ISE WebPack/ModelSim імплементувати в ПЛІС Віртекс базовий і власний розширений проект «DLL тактування». Імплементації верифікувати.

Хід роботи:

Текст модуля наведено нижче:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity L3 is

Port ( CLKIN : in STD_LOGIC;

RESET : in STD_LOGIC;

CLK0 : out STD_LOGIC;

CLK2X : out STD_LOGIC;

LOCKED : out STD_LOGIC);

end L3;

architecture Behavioral of L3 is

component IBUFG

port(O : out STD_ULOGIC;

I : in STD_ULOGIC);

end component;

component IBUF

port(O : out STD_ULOGIC;

I : in STD_ULOGIC);

end component;

component CLKDLL

port ( CLKIN : in std_ulogic := '0';

CLKFB : in std_ulogic := '0';

RST : in std_ulogic := '0';

CLK0 : out std_ulogic := '0';

CLK90 : out std_ulogic := '0';

CLK180 : out std_ulogic := '0';

CLK270 : out std_ulogic := '0';

CLK2X : out std_ulogic := '0';

CLKDV : out std_ulogic := '0';

LOCKED : out std_ulogic := '0');

end component;

component BUFG

port(O :out STD_ULOGIC;

I :in STD_ULOGIC);

end component;

component OBUF

port(O : out STD_ULOGIC;

I : in STD_ULOGIC);

end component;

signal CLKIN_w, RESET_w, CLK0_dll, CLK0_g, CLK2X_dll, LOCKED_dll : std_logic;

begin

clkpad : IBUFG port map (I=>CLKIN, O=>CLKIN_w);

rstpad : IBUF port map (I=>RESET, O=>RESET_w);

dll : CLKDLL port map (CLKIN=>CLKIN_w, CLKFB=>CLK0_g, RST=>RESET_w,

CLK0=>CLK0_dll, CLK90=>open, CLK180=>open,

CLK270=>open, CLK2X=>CLK2X_dll, CLKDV=>open,

LOCKED=>LOCKED_dll);

clkg : BUFG port map (I=>CLK0_dll, O=>CLK0_g);

clk2xg : BUFG port map (I=>CLK2X_dll, O=>CLK2X);

lckpad : OBUF port map (I=>LOCKED_dll, O=>LOCKED);

CLK0 <= CLK0_g;

end Behavioral;

Автоматично згенерована схема проекту наведена на рисунку 1.

Рис. 1 RTL – схема проекту.

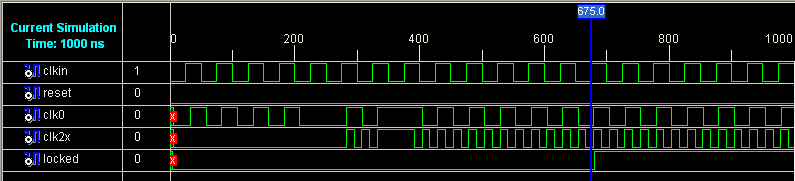

Рис. 2 Часова діаграма симуляції проекту за допомогою TEST-BENCH.

Як видно з часової діаграми сигнал CLK0 повністю повторює вхідний сигнал синхронізації. А сигнал CLK2X формується з частотою, вдвічі швидчою ніж попередній, отже модуль працює правильно.