- •Звіти до лабораторних робіт № 1 - 3 «Проектування комп’ютерних систем та мереж»

- •Сапр Xilinx WebPack

- •Імплементування vhdl моделей операційного та керуючого пристроїв (автоматів)

- •Автомат Мура

- •Імплементування vhdl моделей двохнаправленої шини та lvds шини

- •Шина lvds

- •Синтез та дослідження dll/dcm тактування проектів на пліс

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ „ЛЬВІВСЬКА ПОЛІТЕХНІКА”

Звіти до лабораторних робіт № 1 - 3 «Проектування комп’ютерних систем та мереж»

Виконав:

ст. гр. КСМсі-11з

Мархоцький В.С.

Прийняв:

Бачинський Р.В.

Львів – 2013

ЛР № 1

Сапр Xilinx WebPack

Мета роботи: Опанувати методами роботи в САПР Xilinx WebPack. Дослідити властивості, поведінку та варіанти використання базового примітивного елементу ПЛІС, що отримав назву функційної таблиці (в оригіналі – Look-Up Table (LUT)).

Хід роботи:

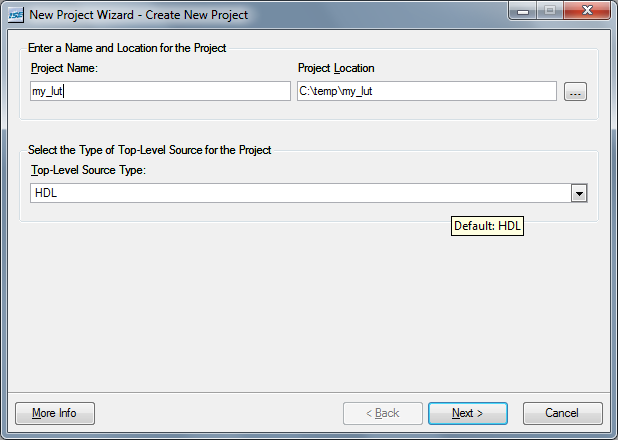

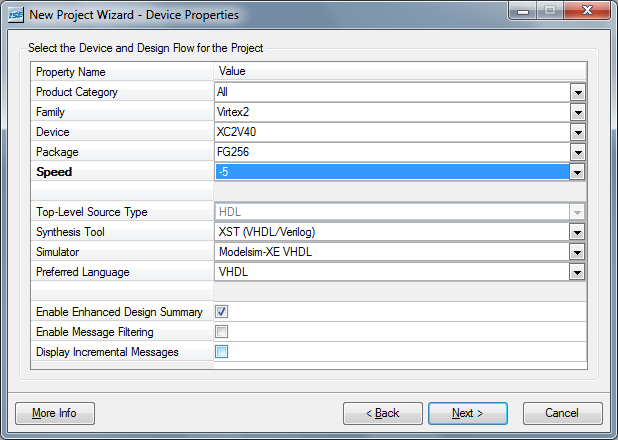

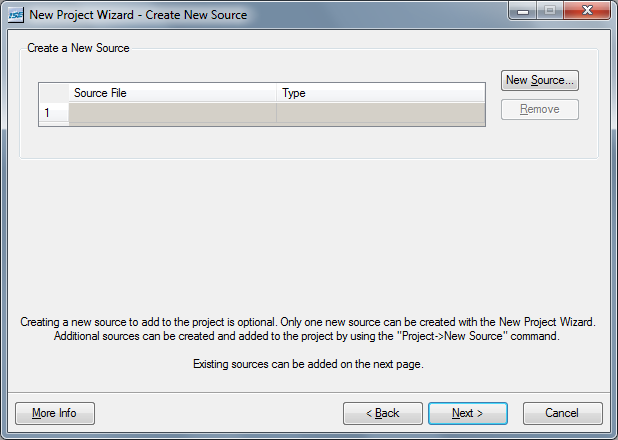

Для створення нового проекту потрібно проробити кроки, що вказані на рисунках 1 – 6.

Рис 1. Створення проекту. Рис 2. Вибір кристалу для роботи.

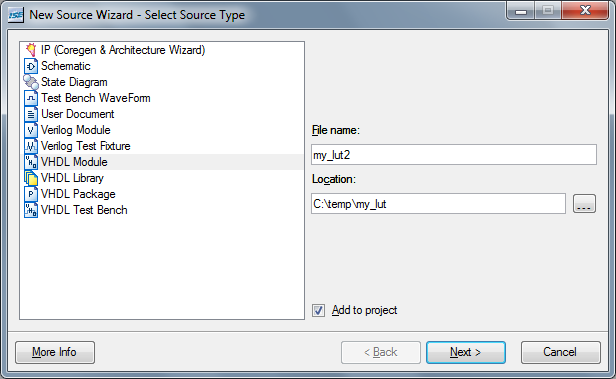

Рис 3. Обираємо джерело Рис 4. Створюємо модуль

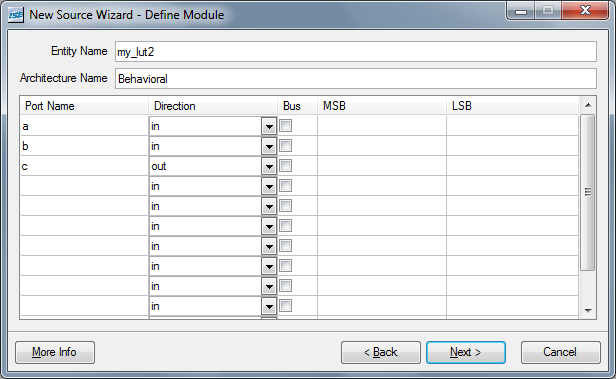

Рис 5. Описуємо модуль Рис 6. Опис створеного проектуу

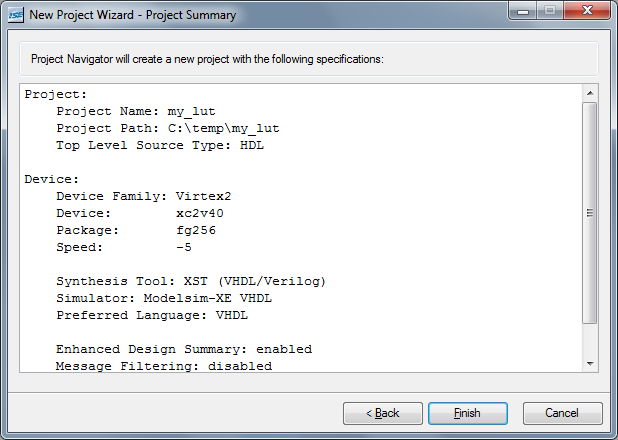

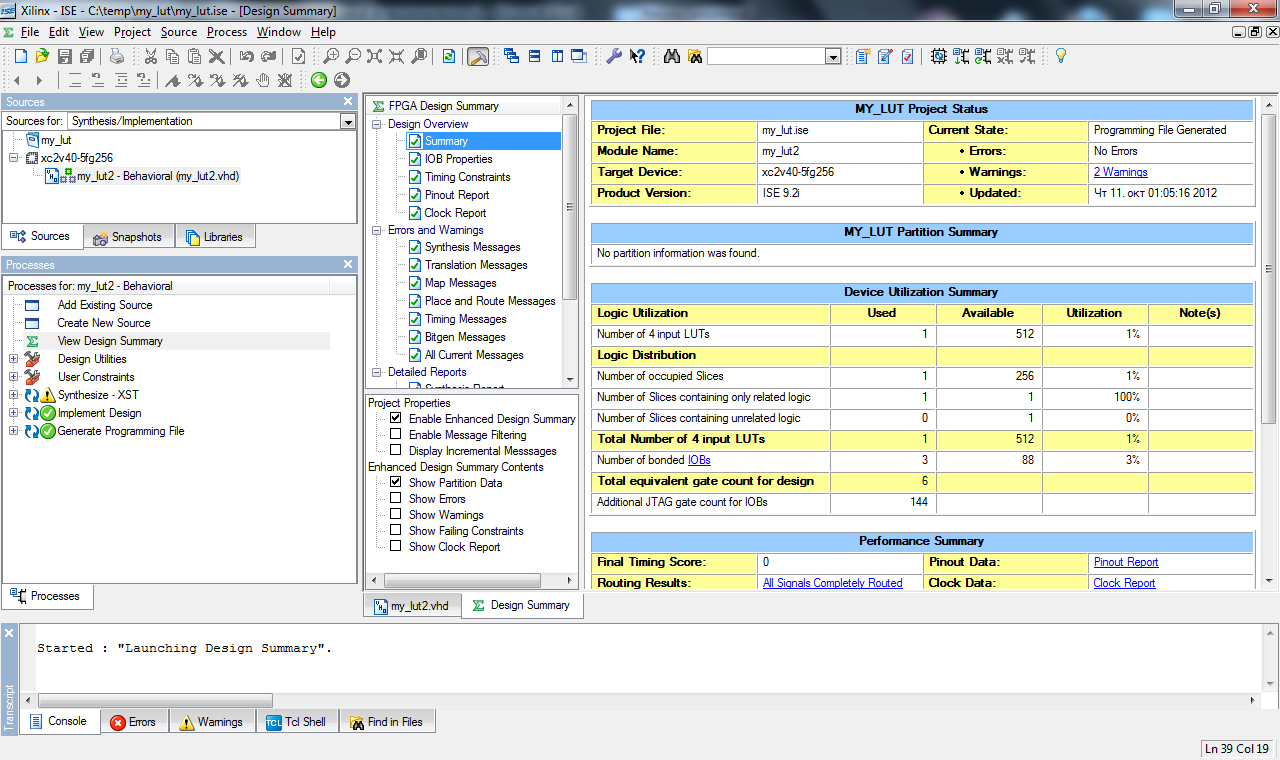

Після створення проекту, додання до нього файлу і налаштування отримаємо вікно, де буде вказана вся інформація по проекту, рис. 7:

Рис. 7. Сумарний звіт по створеному проекту.

У щойно створеному проекті автоматично генерується файл з кодом опису роботи створюваного пристрою (відповідно з налаштуваннями на рис. 5.). Після редагування даного файлу він матиме наступний вигляд до нього додано поведінку роботи пристрою:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity my_lut2 is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC);

end my_lut2;

architecture Behavioral of my_lut2 is

begin

c <= not (a and b);

end Behavioral;

Якщо усе правильно написано, нема помилок у тексті коду опису, то при натисненні на «Process -> Implement to module» відбудеться синтез моделі, про успішність результату свідчать зелені позначки (рис. 8.):

Рис. 8. Вікно проекту після виконання синтезу розробленої моделі.

Звіт про виконання міститься у файлі *.syr :

Final Results

RTL Top Level Output File Name : my_lut2.ngr

Top Level Output File Name : my_lut2

Output Format : NGC

Optimization Goal : Speed

Keep Hierarchy : NO

Design Statistics

# IOs : 3

Cell Usage :

# BELS : 1

# LUT2 : 1

# IO Buffers : 3

# IBUF : 2

# OBUF :

Device utilization summary:

Selected Device : 2v40fg256-5

Number of Slices: 1 out of 256 0%

Number of 4 input LUTs: 1 out of 512 0%

Number of IOs: 3

Number of bonded IOBs: 3 out of 88 3%

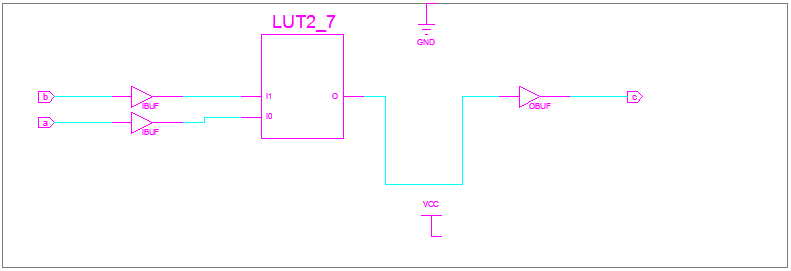

Технологічна схема проекту представлена на рис. 9. Щоб її відкрити потрібно у вікні «Processes» вибрати «Synthesize – XST» -> «View technology schematic».

Рис 9. Технологічна схема проекту.

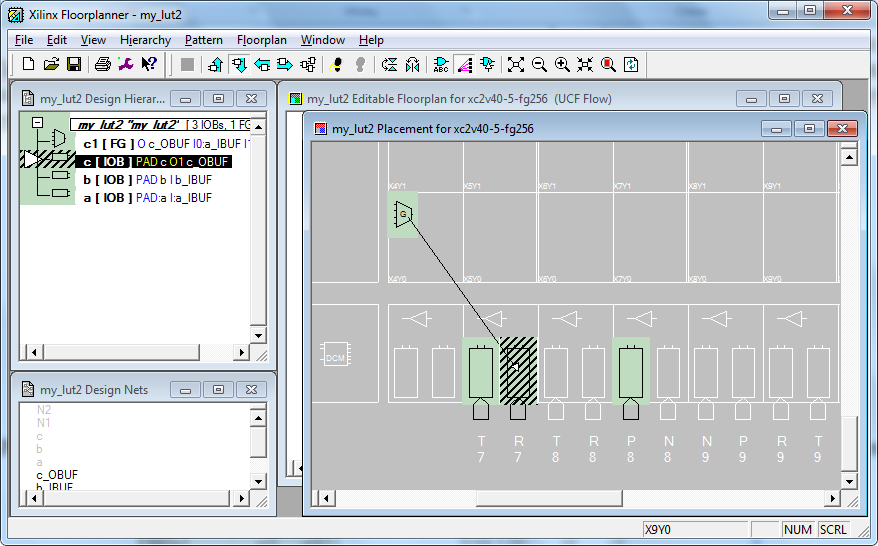

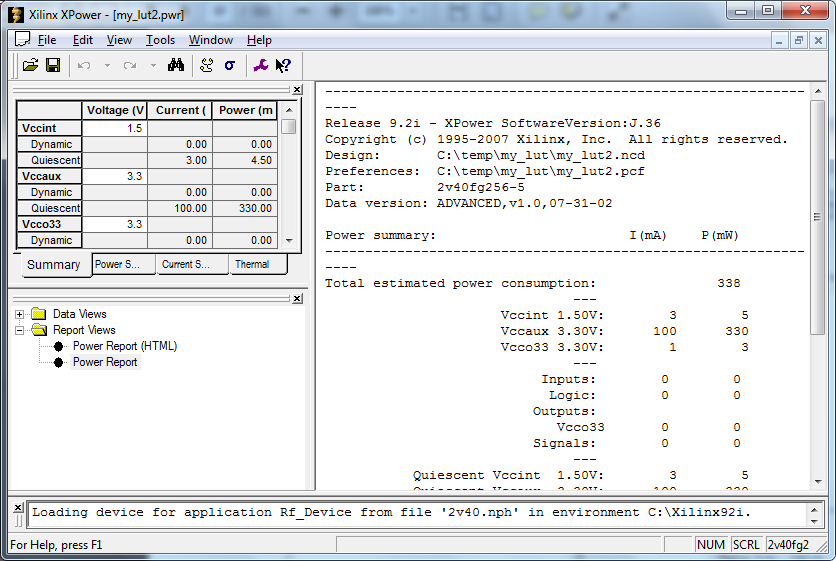

В пакет Xilinx ISE WebPack входить багато допоміжних утиліт. Серед них: утиліта Floorplanner, що подає розташування імплементації проекта на поверхні кристала ПЛІС; видно які контакти ПЛІС та під які сигнали задіяв автомат розведення (рис. 10); утиліта Xilinx Xpower про енергоспоживання проекту (рис. 11).

Рис. 10 Вікно утиліти Floorplanner, що подає розташування імплементації проекта на поверхні кристала ПЛІС.

Рис. 11 вікно утиліти Xilinx Xpower про енергоспоживання проекту my_lut2

Для тестування створеного проекту потрібно додати новий додатковий файлу проекту типу TestBench з назвою tb, чого вимагає подальше проведення Post Place&Route (часової, а не поведінкової) симуляції, що відбувається на рівні вентилів, тобто,з врахуванням затримок елементів і сполучень). Для заміни зовнішнього симулятора проекту ModelSim на ISE Simulator. Після створення буде згенеровано файл з текстом моделі його потрібно відкоректувати до слідуючого змісту:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.all;

USE ieee.numeric_std.ALL;

ENTITY tb_vhd IS

END tb_vhd;

ARCHITECTURE behavior OF tb_vhd IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT my_lut2

PORT(

a : IN std_logic;

b : IN std_logic;

c : OUT std_logic

);

END COMPONENT;

--Inputs

SIGNAL a : std_logic := '1';

SIGNAL b : std_logic := '0';

--Outputs

SIGNAL c : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: my_lut2 PORT MAP(

a => a,

b => b,

c => c

);

a <= not a after 30 ns;

b <= not b after 40 ns;

tb : PROCESS

BEGIN

-- Wait 100 ns for global reset to finish

wait for 100 ns;

-- Place stimulus here

wait; -- will wait forever

END PROCESS;

END;

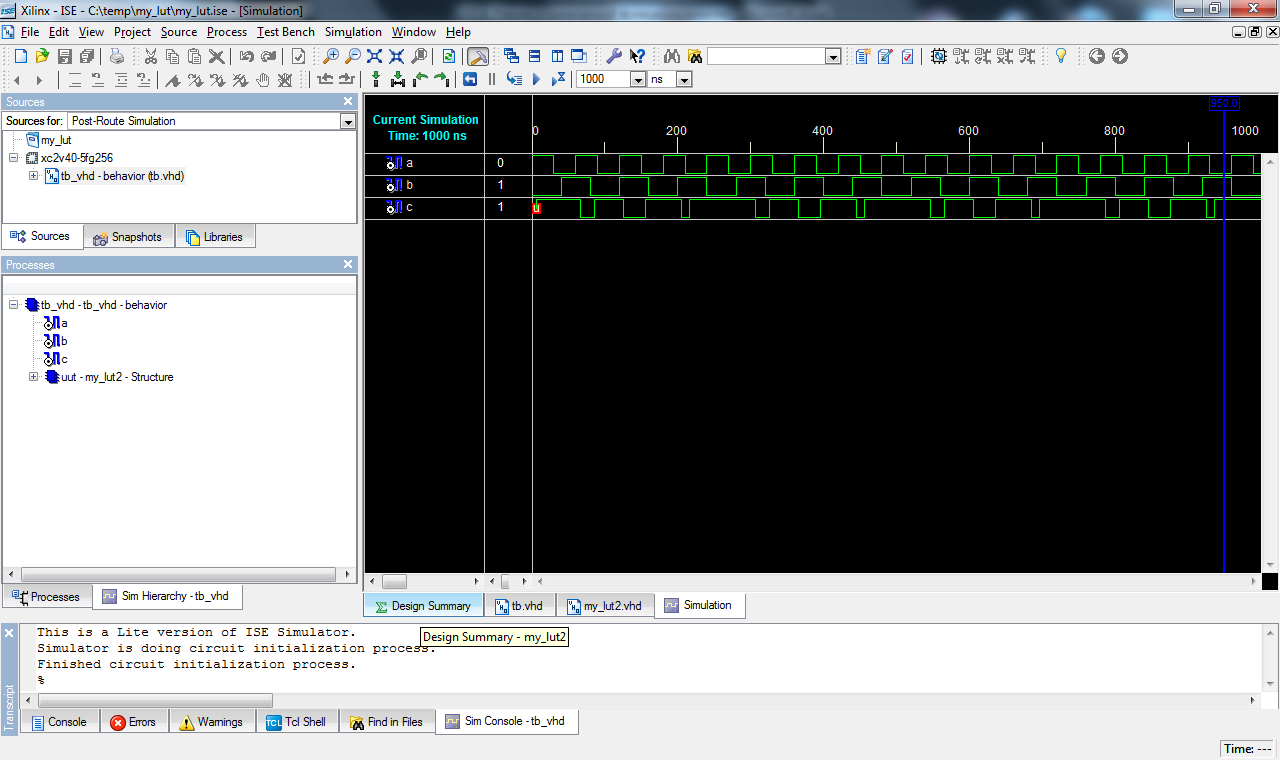

Про правильність роботи тесту можна судити по часових діаграмах після моделювання (рис 12). З діаграми видно, що початкове значення сигналу a становить «1», сигнал a змінює власний рівень кожні 30 нс, а сигнал b – кожні 40 нс.

Рис. 12. Результат моделювання.

ЛР № 2.