- •Әдістемелік құрал

- •Қазақстан Республикасы Білім және Ғылым министрлігінің 2006 жылғы жоспары бойынша басылады

- •Лабораториялық жұмыс № 1. Транзисторлы-транзисторлық сипаттамаларының және сұлбалардың жұмысын зерттеу.

- •Теориялық бөлім

- •Лабораториялық жұмысқа тапсырма және оның орындалу реті:

- •Лабораториялық жұмыс № 2. NМоп және кмоп интегралдық сұлбаларын зерттеу

- •Теориялық бөлім

- •Лабораториялық жұмыс № 3. Дешифраторлар, шифраторлар, мультиплексорлар және демультиплексорлар сұлбаларын зерттеу.

- •Шифратордың ақиқаттық кестесі

- •Лабораториялық жұмыс № 4. Алқ қосындылағыштарының сұлбаларын зерттеу.

- •Теориялық бөлім

- •Лабораториялық жұмыс № 5. Бір және екісатылы rs-, d-, t- және jk- типті триггерлердің сұлбаларын зерттеу.

- •Теориялық бөлім

- •Әдебиеттер тізімі

- •Мазмұны

- •Әдістемелік құрал

- •Жұмыстарға арналған

Лабораториялық жұмыс № 3. Дешифраторлар, шифраторлар, мультиплексорлар және демультиплексорлар сұлбаларын зерттеу.

Лабораториялық жұмысты орындау мақсаты дешифраторлар, шифраторлар, мультиплексорлар және демультиплексорлардың әртүрлі сұлбаларының құрылу және жұмыс істеу принциптерін зерттеу.

Теориялық бөлім

Комбинациялық құрылғылардың арасында практикада кеңірек қолданылатын типтік функционалдық түйіндер, олар: шифраторлар, дешифраторлар, мультиплексорлар, демультиплексорлар, компораторлар, кода түрлендіргіштер, бақылау сұлбалары және қосындылағыштар.

Шифратор деп “N-нан 1” коданы екілікке түрлендіруші комбинациялық типті функционалдық түйінді атаймыз.

0-ден 9-ға (он разрядты бірлік кодалы) дейінгі ондық сандарды екілік-ондық кодаға түрлендіруге арналған шифраторға мысал қарастырамыз. Мұндай шифратордың жұмысы ақиқаттық кестелер негізінде құрылатын келесі логикалық теңдеумен сипатталады. (кесте 3.1).

![]() ;

;

![]() ;

(3.1)

;

(3.1)

![]() ;

;

![]() ,

,

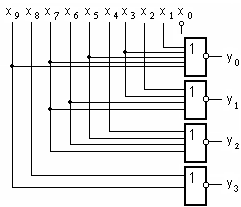

Шифратордың (3.1) логикалық теңдеуіне сәйкес шартты графикалық белгіленуі және оның сұлбасы 3.1-ші суретте келтірілген. 3.1- ші суреттен көрінетіндей шифраторда x0 кірісіне берілетін, қарастырылып жатқан типтегі сигнал қолданылмайды. Кез-келген пернені басқан кезде шифратордың сәйкес кірісіне, шығысынды ондық-екілік кодаға түрленетін логикалық бірлік (лог. 1) сигналы беріледі. Сонымен бірге лог.1 (3.1-кестені қараңыз) сигналы уақыттың әр кезі сайын қозатын тек бір ғана кіріске беріледі. Мұндай бір қозатын кірісі бар шифраторларды екілік шифраторлар деп атайды.

Кесте 3.1

Шифратордың ақиқаттық кестесі

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

Екілік шифраторлардан басқа практикада приоритетті шифраторлар да кеңінен қолданылады. Приоритетті шифраторларда активті сигналдар (лог. 1 немесе лог. 0) бір уақытта бірнеше кірістерге беріледі. Сонымен бірге олардың шығыстарында ең көп қозған кірістер нөміріне сәйкес санның екілік кодасы қалыптасады.

а) б)

Сурет 3.1. Шифратордың шартты графикалық шартты белгісі(а) және оның логикалық сұлбасы(б)

Дешифратор немесе декодер деп кірістерінде n-разрядты екілік коданы шығысында “m-нан 1” кода түріндегі комбинациялық сигналдарды түрлендіретін комбинациялық типті функционалдық түйін аталады, мұндағы n және m сәйкес дешифратордың кірістері және шығыстары.Дешифратордың әр шығыс функциялары бірмәнді түрде m мүмкін кіріс сигналдар комбинацияларының біреуіне сәйкес келеді. Басқаша айтқанда, әрбір нақты кіріс сигналдар комбинациясына сәйкес шығыс функциясы, мысалы логикалық 1-ге тең анық мән қабылдаған кезде, басқаларында функция мәні логикалық 1-ге тең болады. Егер шифратордың кірістер саны n оның шығыстар саны m-мен m = 2n қатынаста байланыста болса, онда дешифратор толық деп аталады. Егер m < 2n болса, яғни дешифратордың шығыстарында барлық мүмкін комбинациялар іске асырылмаса, онда бұндай шифратор толық емес деп аталады. Мысалы, толық емес деп 4 кірісі 10 шығысы бар, екілік коданы екілік ондыққа түрлендіретін дешифраторды атауға болады.

Дешифратордың жұмысы шифратордың (3.1) ақиқаттар кестесіне ұқсас аиқаттар кестесімен анықталады, тек онда кіріс сигналдарымен шығыс сигналдары орындарын ауыстырған.

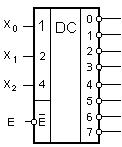

Схемотехникалық дешифраторлар логикалық элементтер (ЛЭ) ЖӘНЕ немесе ЖӘНЕ - ЕМЕС негізінде іске асырылады (реализацияланады). Соңғы жағдайда дешифраторды терістегіш щығыстары бар дешифратор деп атайды. Дешифратордың сызықты деп аталатын ең қарапайым сұлбасында әр шығыс сигналын іске асыру үшін жеке n-кірісті логикалық элемент ЖӘНЕ немесе ЖӘНЕ - ЕМЕС қодданылады. Логикалық элементтің кірістері ЖӘНЕ-ге (немесе ЖӘНЕ - ЕМЕС-ке) кіріс сигналдарының мәндерінің сәйкес комбинациялары беріледі. Сызықтық дешифратордың логикалық элементтер ЖӘНЕ – ЕМЕС-кенің сұлбасы және графикалық шартты белгісі төменде 3.2-суретте көрсетілген.

Әдетте дешифратордың микросұлбаларында стробирлау кірістері, яғни олардың жұмыс істеуіне рұқсат беретін активті логикалық сигналдар болады.

Дешифраторлар цифрлық құрылғыларда кеңінен қолданылады. Олар әртүрлі комбинациялық құрылғылар жасауда қолданылады: мультиплексорлар, демультиплексорлар, кода түрлендіргіштер және т.с.с. Еске сақтау құрылғыларында дешифраторлар көмегімен ақпаратты жазуға не оқуға ұяшықтар таңдап алынады. Енгізу/шығару жүйелерінде дешифраторлар мәліметтерді жіберетін не қабылдайтын көптеген порттардың ішінен біреуін таңдау үшін қолданылады.

а) б)

Сурет. 3.2. Теріс шығысы бар дешифратордың сұлбасы (а) және оның графикалық шартты белгісі (б)

Мультиплексор деп бірнеше кіріс арналары бойынша бір шығысқа келіп түсіп, басқарылатын ақпарат берілуі үшін арналған комбинациялық құрылғы. Ақпараттық кірістерден басқа мультиплексорда адрестік (басқарушы) және мультиплексор жұмысына рұқсат беретін стробирлау кірістері болады. Адрестік кірістердегі сигналдар ақпараттық кірістердің қайсы сол мезетте шығысқа қосулы екенін анықтайды. Әдетте ақпараттық кірістер саны m-мен адрестік кірістер саны n арасында мынадай қатынаста болады, m = 2n.

1 стробирлаушы, 2 адрестік және 4 ақпараттық кірісі бар мультиплексордың жұмысы келесі логикалық теңдеумен анықталады:

(3.2)![]()

мұндағы

Е –активті деңгейі мультиплексордың

жұмысына рұқсат беретін стробирлау

кірісіндегі сигнал. Егер жұмыс істеуге

рұқсат стробирлау

кірісі Е-ге логикалық сигнал 1 (Е=1)

берілсе, онда мультиплексордың шығыс

сигналы ақпараттық

![]() және адрестік

және адрестік

![]() (i=0, 1, 2, 3 және j = 0, 1) сигналдар мәндеріне

тәуелсіз, 0-ге айналады. Басқаша айтқанда,

стробирлаушы

сигнал

Е-нің

көмегімен таңдап алынған кірістің

шығысқа қосылуына рұқсат беруге не

бермеуге болады, яғни мультиплексордың

әрекетін бұғаттауға (блокировка)

болады.

Мультиплексордың (3.2) логикалық теңдеуіне

сәйкес келетін сұлбасы және оның

графикалық шартты белгісі 3.3-суретте

келтірілген. Мультиплексорлар MUX

(ағылшыншадан алынған, multiplexor) немесе

MS (multiplexor selector) арқылы белгіленеді.

Мультиплексорлар, негізінде әр-түрлі

комбинациялық және тізбектес сұлбалар

жасалатын әмбебап логикалық құрылғылар

болып табылады.

(i=0, 1, 2, 3 және j = 0, 1) сигналдар мәндеріне

тәуелсіз, 0-ге айналады. Басқаша айтқанда,

стробирлаушы

сигнал

Е-нің

көмегімен таңдап алынған кірістің

шығысқа қосылуына рұқсат беруге не

бермеуге болады, яғни мультиплексордың

әрекетін бұғаттауға (блокировка)

болады.

Мультиплексордың (3.2) логикалық теңдеуіне

сәйкес келетін сұлбасы және оның

графикалық шартты белгісі 3.3-суретте

келтірілген. Мультиплексорлар MUX

(ағылшыншадан алынған, multiplexor) немесе

MS (multiplexor selector) арқылы белгіленеді.

Мультиплексорлар, негізінде әр-түрлі

комбинациялық және тізбектес сұлбалар

жасалатын әмбебап логикалық құрылғылар

болып табылады.

а) б)

3.3-сурет. Мультиплексордың сұлбасы (а) және оның графикалық шартты белгісі (б)

Демультиплексор деп бір кіріс арнасы бойынша бірнеше шығыстардың біреуіне оның адрестік кірістеріндегі сигналдар мәндеріне байланысты келіп түсіп, басқарылатын мәліметтердің берілуі үшін арналған комбинациялық логикалық құрылғы. Осындай жолмен демультиплексор, мультиплексор функциясына кері функцияны орындайды және жалпы жағдайда бір ақпараттық кірісі, n адрестік кірістері және m ақпараттық шығыстары болады. Әдетте, мультиплексордағы сияқты, m = 2n. Бұл жағдайда демуьтиплексор толық, ал m < 2n жағдайында толық емес деп аталады.

2 адрестік кірісі, 4 ақпараттық шығысы, 1 ақпараттық шығысы және стробирлау кірісі бар демультиплексордың жұмысы келесі логикалық теңдеумен сипатталады:

(3.3)

(3.3)

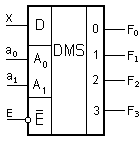

ЛЭ ЖӘНЕ – ЕМЕС –те, (3.3) теңдеуіне сәйкес тұрғызылған демультиплексордың сұлбасы және оның графикалық шартты белгісі 3.7-суретте келтірілген. Демультиплексорлар DMS және DMX арқылы белгіленеді.

Демультиплексорлар тізбекті кодты параллельді кодқа түрлендіруде кеңінен қолданылады.

а) (б)

3.4-сурет. Демультиплексордың сұлбасы (а) және оның графикалық шартты белгісі (б)

Демультиплексордың ақпаратты кірісіне стробирлаушы сигналды берсе, онда оны дешифратор режимінде қолдануға болады,.

Лабораториялық жұмысқа тапсырма және оның орындалу реті:

1. Electronics Workbench(EWB) бағдарламалық кешенінің жұмыс аймағында ЖӘНЕ мен ЖӘНЕ-ЕМЕС логикалық элементтеріндегі үш кіріс айнымалы үшін, дешифратор сұлбасын көрсетіңдер және дешифратордың шығыстарына индикациялық шамдарды қосыңыздар.

2. Дешифратор жұмысының логикасын зерттеп, оның ақиқаттық кестесін тұрғызыңыз.

3. Electronics Workbench(EWB) бағдарламалық кешені көмегімен 0 ден 9-ға (он разрядты бірлік кода ) дейінгі ондық сандарды екілік-ондық кодаға түрлендіретін шифратордың сұлбасының жұмыс істеу принципін зерттеп, ақиқаттар кестесін тұрғызыңдар және сол бойынша шифратордың жұмысын сипаттайтын логикалық теңдеу құрыңдар.

4. EWB программалық комплексі көмегімен 2 адресті және 4 ақпараттық кірісті мультиплексордың сұлбасының жұмыс логикасын зерттеңдер, ақиқаттық кетесін құрыңыз. Сол кесте бойынша шифратордың жұмысын сипаттайтын логикалық теңдеулерді құрыңыздар.

EWB бағдарламалық кешені көмегімен 2 адресті және 4 ақпараттық кірістері бар мультиплексордың сұлбасының жұмыс істеу логикасын зерттеп, оның жұмысын сипаттайтын логикалық теңдеулерін жазыңыз.

Бақылау сұрақтары:

Толық шифратордың жұмыс істеу принципін түсіндіріңіздер.

Толық дешифратордың жұмыс істеу принципін түсіндіріңіздер.

Қандай комбинациялық құрылғыларды құруда дешифратор қолданылады?

Мультиплексор мен демультиплексордың кірістері қалай аталады?