Основні режими uart 3.4.Последовательный порт микроконтроллера 8051.

Через универсальный асинхронный приемопередатчик UART (Universal Asynchronous Receiver-Transmitter) осуществляются прием и передача информации, представленной последовательным кодом (младшими битами вперед), в полном дуплексном режиме обмена. В состав приемопередатчика, называемого часто последовательным портом входят принимающий и передающий сдвигающие регистры, а также специальный буферный регистр (SBUF) приемопередатчика.

Кроме того, работой последовательного порта управляют два служебных регистра -

Регистр управления/статуса приемопередатчика SCON

Бит SMOD регистра управления мощностью PCON

Запись байта в буфер приводит к автоматической переписи байта в сдвигающий регистр передатчика и инициирует начало передачи байта. Наличие буферного регистра приемника позволяет совмещать операцию чтения ранее принятого байта с приемом очередного. Но если к моменту окончания приема байта предыдущий не был считан из SBUF, то он будет потерян.

Последовательный порт 8051 может работать в четырех различных режимах.

Режим 0. Информация и передается, и принимается через вывод входа приемника (RXi TXi). Принимаются или передается 8 бит данных. Через вывод выхода передатчика (TXD; выдаются импульсы сдвига, которые сопровождают каждый бит. Частота передачи бита информации равна 1/12 частоты кварцевого резонатора

Режим 1. В этом режиме передаются через вывод TXD или принимаются через RXD 10 бит информации: старт-бит (0), 8 бит данных и стоп-бит (1) при приеме информации в бит RB8 регистра управления/статуса приемопередатчика SCON заносятся стоп-бит Скорость приема/передачи — величина переменная и задается таймером.

Режим 2. В этом режиме через вывод TXD передаются или через RXD принимаются 11 бит информации: старт-бит, 8 бит данных, программируемый девятый бит и стоп-бит. При передаче девятый бит данных может принимать значение 0 или 1 или, например, для повышения достоверности передачи путем контроля по четности в него может быть помещено значение признака паритета из слова состояния программы (PSW.0). При приеме девятый бит данных помещается в бит RB8 SCON, а стоп-бит, в отличие от режима 1, теряется. Частота приема/передачи выбирается программой и может быть равна либо 1/32, либо 1/64 частоты резонатора в зависимости от управляющего бита SMOD.

Режим 3. совпадает с режимом 2 во всех деталях, за исключением частоты приема/передачи, которая является величиной переменной и задается таймером.

Во всех случаях передача инициализируется инструкцией, в которой данные перемещаются в SBUF. Прием инициализируется при обнаружении перепада из 1 в 0 на входе приемника. При этом в режиме 0 этот переход должен сопровождаться выполнением условий R1 = 0 и REN= 1 (см. табл. 8), а для остальных режимов - REN = 1.

Підєднання зовнішньої памяті до МК-51

Обращения к внешней памяти подразделяются на обращения к внешней памяти программ и обращения к внешней памяти данных. В первом случае для формирования сигнала, активирующего ПЗУ с программой, используется сигнал PSEN, во втором — сигналы RD и WR, активизирующие ОЗУ с данными.

Если используется 16-битовый адрес, старшие восемь бит выводятся через порт Р2 , где они сохраняются в течение всего цикла обращения к внешней памяти. Отметим, что выходные каскады порта Р2 имеют внутреннюю нагрузку, несколько отличающуюся от Р1 и РЗ , благодаря чему в SFR Р2 при выводе адресной информации вовсе не обязательно защелкивать все единицы. Добавим также, что при выводе адресной информации информация из SFR Р2, хотя и не присутствует на выводах микроЭВМ, но и не теряется, восстанавливаясь на них после окончания обращений к внешней памяти (если в процессе этих обращений SFR Р2 не был модифицирован).

Если при обращении к внешней памяти данных используется восьми битный адрес, то на выводах порта остается та же информация, которая там была до начала обращения к внешней памяти. Это позволяет организовать постраничную адресацию внешней памяти данных.

Как уже отмечалось, на выводах порта P0 младший байт адреса мультиплексируется с данными. Сигналы адреса/ данных задействуют оба полевых транзистора выходного каскада порта P0. Таким образом, в этом случае выводы P0 уже не являются выводами с открытым стоком и не требуют внешних нагрузочных элементов.

Сигнал ALE используется для фиксации младшего байта адреса во внешнем регистре-защелке. Адресная информация достоверна в момент окончания сигнала ALE.

Выводимый в цикле записи байт заносится в P0 непосредственно перед активацией сигнала WR и остается неизменным до окончания этого сигнала. В цикле чтения данные на выводах P0 для достоверного считывания должны быть установившимися к моменту окончания сигнала RD.

Во время обращения к внешней памяти CPU записывает 0FFH в SFR P0, уничтожая, таким образом, хранимую там информацию. Таким образом, использовать для записи порт P0 при работе с внешней памятью надо с известной долей осторожности.

Обращение к внешней памяти программ возможно в двух случаях:

когда сигнал ЕА активен, т.е. имеет нулевой уровень,

когда программный счетчик РС содержит число больше 0FFH.

Следовательно, при использовании микро-ЭВМ, не имеющей встроенного ПЗУ или не использующей его, на входе ЕА должен присутствовать сигнал с нулевым уровнем.

Когда CPU работает с внешней памятью программ, все линии порта Р2 используются для вывода старшего байта адреса и не могут быть использованы для обычного ввода\вывода информации. При этом, как отмечалось выше, в SFR Р2 может быть занесена любая информация — адресная информация, выводимая через Р2, не зависит от состояния его SFR.

Блок-схема роботи послідовного АЦП

Функціонування аналого-цифрового перетворення за методом послідовного підрахунку можна проілюструвати за допомогою структурної схеми на рис. 4.6.

Рисунок 4.6 – АЦП послідовного підрахунку

До складу схеми входять:

генератор тактових сигналів (G), компаратор

напруги (КН), схема І, лічильник (ЛЧ),

буферний регістр (БР), цифро-аналоговий

перетворювач (ЦАП). Схема працює наступним

чином. На вхід перетворювача подається

аналоговий сигнал

![]() ,

який підключається до одного з входів

компаратора напруги КН. На другий вхід

компаратора подається еталонна напруга

(

,

який підключається до одного з входів

компаратора напруги КН. На другий вхід

компаратора подається еталонна напруга

(![]() ),

яка формується на виході ЦАП під

управлінням колового слова на виході

ЛЧ. Компаратор формує на своєму виході

сигнал або логічної одиниці, або логічного

нуля в залежності від того, яке значення

більше. Якщо

),

яка формується на виході ЦАП під

управлінням колового слова на виході

ЛЧ. Компаратор формує на своєму виході

сигнал або логічної одиниці, або логічного

нуля в залежності від того, яке значення

більше. Якщо

![]() ,

то на виході компаратора формується

одиниця, яка дозволяє проходження

імпульсів з тактового генератора через

схему І на лічильний вхід лічильника

ЛЧ. На виході лічильника йде процес

підрахунку цих імпульсів в двійковому

коді від 2

,

то на виході компаратора формується

одиниця, яка дозволяє проходження

імпульсів з тактового генератора через

схему І на лічильний вхід лічильника

ЛЧ. На виході лічильника йде процес

підрахунку цих імпульсів в двійковому

коді від 2![]() до 2

до 2![]() .

Двійковий код з ЛЧ подається на вхід

ЦАП, на виході якого формується ступінчатий

сигнал

.

Кожна сходинка цього сигналу відповідає

за рівнем інтервалу дискретизації

.

Двійковий код з ЛЧ подається на вхід

ЦАП, на виході якого формується ступінчатий

сигнал

.

Кожна сходинка цього сигналу відповідає

за рівнем інтервалу дискретизації

![]() .

Сигнал

порівнюється

із сигналом

і

в момент, коли

стає

меншим за

,

на виході компаратора формується сигнал

логічного нуля. Схема І закривається,

лічильник зупиняє підрахунок і набраний

двійковий код переписується у вихідний

буферний регістр БР для видачі користувачу.

.

Сигнал

порівнюється

із сигналом

і

в момент, коли

стає

меншим за

,

на виході компаратора формується сигнал

логічного нуля. Схема І закривається,

лічильник зупиняє підрахунок і набраний

двійковий код переписується у вихідний

буферний регістр БР для видачі користувачу.

Блок-схема роботи паралельного АЦП

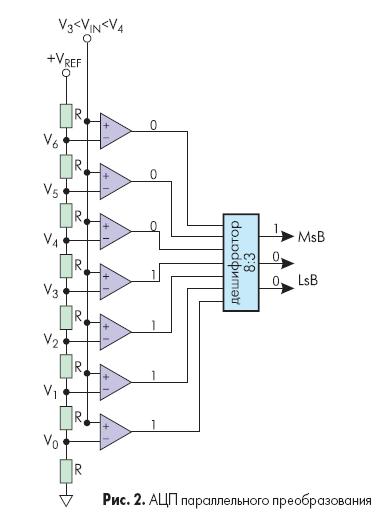

Большинство высокоскоростных осциллографов и некоторые высокочастотные измерительные приборы используют параллельные АЦП из-за их высокой скорости преобразования, которая может достигать 5Г (5*109) отсчетов/сек для стандартных устройств и 20Г отсчетов/сек для оригинальных разработок. Обычно параллельные АЦП имеют разрешение до 8 разрядов, но встречаются также 10-ти разрядные версии.

Рис. 2 показывает упрощенную блок-схему 3-х разрядного параллельного АЦП (для преобразователей с большим разрешением принцип работы сохраняется). Здесь используется массив компараторов, каждый из которых сравнивает входное напряжение с индивидуальным опорным напряжением. Такое опорное напряжение для каждого компаратора формируется на встроенном прецизионном резистивном делителе. Значения опорных напряжений начинаются со значения, равного половине младшего значащего разряда (LSB), и увеличиваются при переходе к каждому следующему компаратору с шагом, равным VREF /23. В результате для 3-х разрядного АЦП требуется 23-1 или семь компараторов. А, например, для 8-разрядного параллельного АЦП потребуется уже 255 (или (28-1)) компараторов.

С увеличением входного напряжения компараторы последовательно устанавливают свои выходы в логическую единицу вместо логического нуля, начиная с компаратора, отвечающего за младший значащий разряд. Можно представить преобразователь как ртутный термометр: с ростом температуры столбик ртути поднимается. На рис. 2 входное напряжение попадает в интервал между V3 и V4, таким образом 4 нижних компаратора имеют на выходе "1", а верхние три компаратора - "0". Дешифратор преобразует (23-1) - разрядное цифровое слово с выходов компараторов в двоичный 3-х разрядный код.

Параллельные АЦП - достаточно быстрые устройства, но они имеют свои недостатки. Из-за необходимости использовать большое количество компараторов параллельные АЦП потребляют значительную мощность, и их нецелесообразно использовать в приложениях с батарейным питанием.

Блок-схема роботи послідовного ЦАП

Очень часто ЦАП входит в состав микропроцессорных систем. В этом случае, если не требуется высокое быстродействие, цифро-аналоговое преобразование может быть очень просто осуществлено с помощью широтно-импульсной модуляции (ШИМ). Схема ЦАП с ШИМ приведена на рис. 1а.

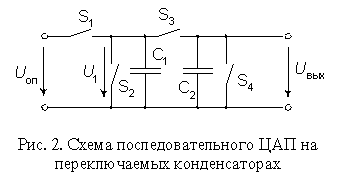

Рассмотренная выше схема ЦАП с ШИМ вначале преобразует цифровой код во временной интервал, который формируется с помощью двоичного счетчика квант за квантом, поэтому для получения N-разрядного преобразования необходимы 2N временных квантов (тактов). Схема последовательного ЦАП, приведенная на рис. 2, позволяет выполнить цифро-аналоговое преобразование за значительно меньшее число тактов.

В этой схеме емкости конденсаторов С1 и С2 равны. Перед началом цикла преобразования конденсатор С2 разряжается ключом S4. Входное двоичное слово задается в виде последовательного кода. Его преобразование осуществляется последовательно, начиная с младшего разряда d0. Каждый такт преобразования состоит из двух полутактов. В первом полутакте конденсатор С1 заряжается до опорного напряжения Uоп при d0=1 посредством замыкания ключа S1 или разряжается до нуля при d0=0 путем замыкания ключа S2. Во втором полутакте при разомкнутых ключах S1, S2 и S4 замыкается ключ S3, что вызывает деление заряда пополам между С1 и С2. В результате получаем

U1(0)=Uвых(0)=(d0/2)Uоп |

(3) |

Таким образом, представленная схема выполняет преобразование входного кода за 2N квантов, что значительно меньше, чем у ЦАП с ШИМ. Здесь требуется только два согласованных конденсатора небольшой емкости. Конфигурация аналоговой части схемы не зависит от разрядности преобразуемого кода. Однако по быстродействию последовательный ЦАП значительно уступает параллельным цифро-аналоговым преобразователям, что ограничивает область его применения.

Блок-схема роботи паралельного ЦАП

Большинство схем параллельных ЦАП основано на суммировании токов, сила каждого из которых пропорциональна весу цифрового двоичного разряда, причем должны суммироваться только токи разрядов, значения которых равны 1. Пусть, например, требуется преобразовать двоичный четырехразрядный код в аналоговый сигнал тока. У четвертого, старшего значащего разряда (СЗР) вес будет равен 23=8, у третьего разряда – 22=4, у второго – 21=2 и у младшего (МЗР) – 20=1. Если вес МЗР IМЗР=1 мА, то IСЗР=8 мА, а максимальный выходной ток преобразователя Iвых.макс=15 мА и соответствует коду 11112. Понятно, что коду 10012, например, будет соответствовать Iвых=9 мА и т.д. Следовательно, требуется построить схему, обеспечивающую генерацию и коммутацию по заданным законам точных весовых токов. Простейшая схема, реализующая указанный принцип, приведена на рис. 3.

Сопротивления резисторов выбирают так, чтобы при замкнутых ключах через них протекал ток, соответствующий весу разряда. Ключ должен быть замкнут тогда, когда соответствующий ему бит входного слова равен единице. Выходной ток определяется соотношением

При высокой разрядности ЦАП токозадающие резисторы должны быть согласованы с высокой точностью. Наиболее жесткие требования по точности предъявляются к резисторам старших разрядов, поскольку разброс токов в них не должен превышать тока младшего разряда. Поэтому разброс сопротивления в k-м разряде должен быть меньше, чем

R / R=2–k

Из этого условия следует, что разброс сопротивления резистора, например, в четвертом разряде не должен превышать 3%, а в 10-м разряде – 0,05% и т.д.

Рассмотренная схема при всей ее простоте обладает целым букетом недостатков. Во-первых, при различных входных кодах ток, потребляемый от источника опорного напряжения (ИОН), будет различным, а это повлияет на величину выходного напряжения ИОН. Во-вторых, значения сопротивлений весовых резисторов могут различаться в тысячи раз, а это делает весьма затруднительной реализацию этих резисторов в полупроводниковых ИМС. Кроме того, сопротивление резисторов старших разрядов в многоразрядных ЦАП может быть соизмеримым с сопротивлением замкнутого ключа, а это приведет к погрешности преобразования. В-третьих, в этой схеме к разомкнутым ключам прикладывается значительное напряжение, что усложняет их построение.

Эти недостатки устранены в схеме ЦАП AD7520 (отечественный аналог 572ПА1), разработанном фирмой Analog Devices в 1973 году, которая в настоящее время является по существу промышленным стандартом (по ней выполнены многие серийные модели ЦАП). Указанная схема представлена на рис. 4. В качестве ключей здесь используются МОП-транзисторы.

Архітектура інтерфейсу 1-Wire

Подключение шины 1-Wire к МК показано условно в двух вариантах: с использованием 2 отдельных выводов МК (один в качестве выхода, а другой в качестве входа), так и одного, работающего и на ввод и на вывод. Разделение этих способов показано пунктирной линией, условно обозначающей границу корпуса МК.

Основные принципы

1‑Wire‑net представляет собой информационную сеть, использующую для осуществления цифровой связи 1‑Wire‑магистраль, состоящую из шины данных (DATA) и возвратной шины (RET). Таким образом, для реализации среды обмена этой сети могут быть применены доступные кабели, содержащие неэкранированную витую пару той или иной категории, и даже обычный телефонный шнур. Такие кабели при их прокладке не требуют наличия какого‑либо специального оборудования, а ограничение максимальной протяжённость кабеля 1‑Wire‑магистрали регламентировано разработчиками на уровне 300 м.

Основой архитектуры 1‑Wire‑сетей является топология общей шины, когда каждый из абонентов подключён непосредственно к единой магистрали, без каких‑либо каскадных соединений или ветвлений. При этом в качестве базовой используется структура сети с одним ведущим или мастером и многочисленными ведомыми абонентами. Хотя существует ряд специфических приёмов организации работы 1‑Wire‑систем в режиме мультимастера.

Конфигурация любой 1‑Wire‑сети может произвольно меняться в процессе её работы, не создавая помех дальнейшей эксплуатации и работоспособности всей системы в целом, если при этих изменениях соблюдаются принципы организации 1‑Wire‑интерфейса. Эта возможность достигается благодаря присутствию в протоколе 1‑Wire‑интерфейса специальной команды поиска ведомых устройств (Поиск ПЗУ), которая позволяет быстро определить новых участников информационного обмена. Стандартная скорость отработки такой команды составляет ~75 узлов сети в секунду.

Благодаря наличию в составе любого устройства, снабженного 1‑Wire‑интерфейсом, индивидуального адреса, столь же уникального, как и номер денежной купюры (отсутствие совпадения адресов для компонентов, когда‑либо выпускаемых Maxim Integrated, гарантируется самой фирмой‑производителем), такая сеть имеет практически неограниченное адресное пространство. При этом каждый из 1‑Wire‑компонентов сразу готов к использованию в составе 1‑Wire‑сети, без каких‑либо дополнительных аппаратно‑программных модификаций.

1‑Wire‑компоненты являются самотактируемыми полупроводниковыми устройствами, в основе обмена информацией между которыми лежит управление длительностью импульсных сигналов, предаваемых по 1‑Wire‑магистрали, и их измерение. Передача сигналов для 1‑Wire‑интерфейса — асинхронная и полудуплексная, а вся информация, циркулирующая в сети, воспринимается абонентами либо как команды, либо как данные. Команды сети генерируются мастером и обеспечивают различные варианты поиска и адресации ведомых устройств, определяют активность на 1‑Wire‑магистрали даже без непосредственной адресации отдельных абонентов, управляют обменом данными в сети и т.д.

С тандартная

скорость работы 1‑Wire‑сети, изначально

нормированная на уровне 16,3 Кбит/с, была

выбрана, во‑первых, исходя из

обеспечения максимальной надёжности

передачи данных на большие расстояния,

и, во‑вторых, с учётом быстродействия

наиболее широко распространённых типов

универсальных микроконтроллеров,

которые в основном должны использоваться

при реализации ведущих устройств

1‑Wire‑сети. Эта скорость обмена

может быть снижена до любой возможной,

благодаря введению принудительной

задержки при передаче по магистрали

отдельных битов данных (т.е. растягиванию

временных слотов протокола). Однако

увеличение скорости обмена в 1‑Wire‑сети

с длиной кабеля магистрали более 1 м

выше значения 16,3 Кбит/с приводит к сбоям

и ошибкам. Если же протяженность

1‑Wire‑магистрали не превышает 0,5

м, то скорость обмена может быть

значительно увеличена за счёт перехода

на специальный режим ускоренной передачи

(Overdrive

‑ до 125 Кбит/с), который допускается

для отдельных типов 1‑Wire‑компонентов.

Как правило, такой режим обмена аппаратно

реализован для 1‑Wire‑компонентов,

имеющих большой объём встроенной памяти,

предназначенных для эксплуатации в

составе небольшой, но качественной и

не перегруженной другими устройствами

1‑Wire‑сети. Типичным примером таких

компонентов являются микросхемы

семейства iButton.

тандартная

скорость работы 1‑Wire‑сети, изначально

нормированная на уровне 16,3 Кбит/с, была

выбрана, во‑первых, исходя из

обеспечения максимальной надёжности

передачи данных на большие расстояния,

и, во‑вторых, с учётом быстродействия

наиболее широко распространённых типов

универсальных микроконтроллеров,

которые в основном должны использоваться

при реализации ведущих устройств

1‑Wire‑сети. Эта скорость обмена

может быть снижена до любой возможной,

благодаря введению принудительной

задержки при передаче по магистрали

отдельных битов данных (т.е. растягиванию

временных слотов протокола). Однако

увеличение скорости обмена в 1‑Wire‑сети

с длиной кабеля магистрали более 1 м

выше значения 16,3 Кбит/с приводит к сбоям

и ошибкам. Если же протяженность

1‑Wire‑магистрали не превышает 0,5

м, то скорость обмена может быть

значительно увеличена за счёт перехода

на специальный режим ускоренной передачи

(Overdrive

‑ до 125 Кбит/с), который допускается

для отдельных типов 1‑Wire‑компонентов.

Как правило, такой режим обмена аппаратно

реализован для 1‑Wire‑компонентов,

имеющих большой объём встроенной памяти,

предназначенных для эксплуатации в

составе небольшой, но качественной и

не перегруженной другими устройствами

1‑Wire‑сети. Типичным примером таких

компонентов являются микросхемы

семейства iButton.

Інтерфейс 1-Wire

П ри

реализации 1‑Wire‑интерфейса

используются стандартные КМОП/ТТЛ

логические уровни сигналов, а питание

большинства 1‑Wire‑компонентов

может осуществляться от внешнего

источника с рабочим напряжением в

диапазоне от 2,8 В до 6,0 В. Причём такой

источник может быть расположен либо

непосредственно возле компонента

(например, батарея в составе микросхем

iButton), либо энергия от него может поступать

по отдельной особой шине 1‑Wire‑магистрали.

Альтернативой применению внешнего

питания служит так называемый механизм

паразитного питания,

действие которого заключается в

использовании каждым из ведомых абонентов

1‑Wire‑сети электрической энергии

импульсов, передаваемых по шине данных,

аккумулируемой затем специальной

ёмкостью, встроенной в состав интерфейсного

узла некоторых 1‑Wire‑компонентов.

Кроме того, отдельные 1‑Wire‑компоненты

могут использовать особый режим питания

по шине данных, когда энергия к приёмнику

поступает непосредственно от мастера

по шине DATA магистрали, при этом обмен

информацией в 1‑Wire‑сети принудительно

прекращается.

ри

реализации 1‑Wire‑интерфейса

используются стандартные КМОП/ТТЛ

логические уровни сигналов, а питание

большинства 1‑Wire‑компонентов

может осуществляться от внешнего

источника с рабочим напряжением в

диапазоне от 2,8 В до 6,0 В. Причём такой

источник может быть расположен либо

непосредственно возле компонента

(например, батарея в составе микросхем

iButton), либо энергия от него может поступать

по отдельной особой шине 1‑Wire‑магистрали.

Альтернативой применению внешнего

питания служит так называемый механизм

паразитного питания,

действие которого заключается в

использовании каждым из ведомых абонентов

1‑Wire‑сети электрической энергии

импульсов, передаваемых по шине данных,

аккумулируемой затем специальной

ёмкостью, встроенной в состав интерфейсного

узла некоторых 1‑Wire‑компонентов.

Кроме того, отдельные 1‑Wire‑компоненты

могут использовать особый режим питания

по шине данных, когда энергия к приёмнику

поступает непосредственно от мастера

по шине DATA магистрали, при этом обмен

информацией в 1‑Wire‑сети принудительно

прекращается.

А теперь о том, как происходит обмен информацией по шине 1-Wire. Основные постулаты.

Обмен всегда ведется по инициативе одного ведущего устройства, которое в большинстве случаев является микроконтроллером (МК).

Любой обмен информацией начинается с подачи импульса сброса ("Reset Pulse" или просто RESET) в линию 1-Wire ведущим устройством.

Для интерфейса 1-Wire в общем случае предусматривается "горячее" подключение и отключение устройств.

Любое устройство, подключенное к 1-Wire после получения питания выдает в линию DQ импульс присутствия, называемый "Presence pulse" (далее я буду использовать термин PRESENCE). Этот же импульс устройство всегда выдает в линию, если обнаружит сигнал RESET.

Появление в шине 1-Wire импульса PRESENCE после выдачи RESET однозначно свидетельствует о наличии хотя бы одного подключенного устройства.

Обмен информации ведется так называемыми тайм-слотами: один тайм-слот служит для обмена одним битом информации.

Данные передаются побайтно, бит за битом, начиная с младшего бита. Достоверность переданных-принятых данных, проверка отсутствия искажений, гарантируется путем подсчета циклической контрольной суммы.

Основные постулаты определяют логический низкоуровневый протокол обмена данными.

Основні команди інтерфейсу 1-Wire

Команда |

Значение байта |

Описание |

SEARCH ROM |

0xF0 |

Поиск адресов - используется при универсальном алгоритме определения количества и адресов подключенных устройств |

READ ROM |

0x33 |

Чтение адреса устройства - используется для определения адреса единственного устройства на шине |

MATCH ROM |

0x55 |

Выбор адреса - используется для обращения к конкретному адресу устройства из многих подключенных |

SKIP ROM |

0xCC |

Игнорировать адрес - используется для обращения к единственному устройству на шине, при этом адрес устройства игнорируется (можно обращаться к неизвестному устройству) |