- •Завдання до графічно-розрахункової роботи

- •Індивідуальне завдання до ргр

- •1. Тип мікросхеми для побудови блоку пам’яті

- •2. Виділення адресного простору для блоку пам’яті

- •Розрахунок визначення кількості мікросхем пам’яті для блоку

- •4. Синтез схеми дешифратора адрес для блоку пам’яті

- •Аналіз результатів та висновки

- •Перелік умовних позначень

- •Список використаної літератури

Розрахунок визначення кількості мікросхем пам’яті для блоку

При побудові блоку пам’яті часто виникає потреба в об’єднанні між собою певним способом декількох мікросхем пам’яті. Це здійснюється у таких випадках:

1) при нарощуванні розрядності

2) при нарощуванні об’єму

3) при одночасному нарощуванні як об’єму так і розрядності.

Щоб знайти кількість мікросхем для нарощення розрядності використовую формулу:

К = n/ni, де ni – розрядність мікросхеми пам’яті

n – розрядність пам’яті, яку потрібно побудувати

К = 4/4 = 1

Щоб знайти кількість мікросхем для нарощення об’єму пам’яті використовую формулу:

L = N/Ni, де Ni – об’єм пам’яті однієї мікросхеми,

N – об’єм пам’яті, яку потрібно побудувати

L = 8/2 = 4

Отже, щоб побудувати заданий блок пам’яті, необхідно об’єднати M = К*L = 1*4 = 4 мікросхеми з організацією 2К х 4.

Отже, щоб синтезувати ПЗП об’ємом 8КБ (8К х 4) на основі мікросхеми з організацією 2К х 4, адресний простір необхідно адресувати для чотирьох банківпам’яті (нарощення об’єму), в яких є по одній мікросхемі.

4. Синтез схеми дешифратора адрес для блоку пам’яті

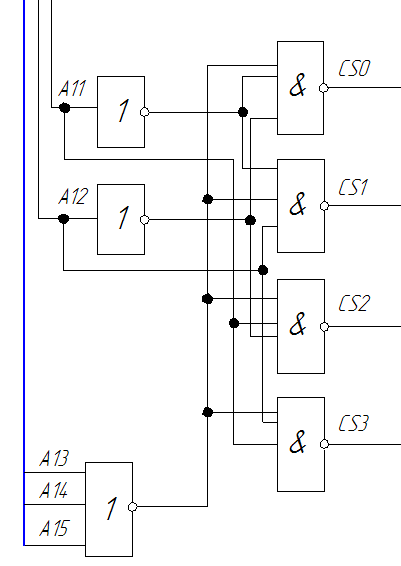

При каскадуванні мікросхем виникає потреба визначати – до якої саме з мікросхем іде звертання. Для адресного розподілу використовують адресні дешифратори, число виходів яких рівне L числу мікросхем.

Синтез схеми адресного дешифратора складається з послідовних етапів:

табличного задання початкової та кінцевої адреси для заданого блоку пам’яті;

представлення логічних виразів у ДДНФ або ДКНФ на основі таблиці;

побудова комбінаційної схеми адресного дешифратора на основі логічного виразу.

На основі таблиці 4 запишу логічний вираз у вигляді ДКНФ:

СS0=( );

);

СS1=( );

);

СS2=( );

);

СS3=( );

);

На рисунку 4.1 представлена комбінаційна схема реалізації адресного дешифратора.

Рис.

4.1 Схема реалізації адресного дешифратора

Рис.

4.1 Схема реалізації адресного дешифратора

Аналіз результатів та висновки

При виконанні даної графічно-розрахункової роботи я ознайомилась з організацією ПЗП, набула практичних навичок у реалізації блоків ПЗП за допомогою даних елементів із заданою структурою для мікропроцесора КР580ВМ80.

Я спроектувала блок ПЗП розміром 8Кб на основі мікросхеми К573РФ23 з організацією 2К х 4.

Область адресного простору, у якому даний блок буде працювати:

АП = 0000h=0000 0000 0000 0000; АК = 1FFFh=0001 1111 1111 1111.

Синтезовано дешифратор адрес, який має чотири виходи і три входи.

Приведена принципова електрична схема заданого блоку пам’яті.

Перелік умовних позначень

МПС – мікропроцесорна система

ОЗП – оперативно запам’ятовуючий пристрій

ПЗП – постійно запам’ятовуючий пристрій

ЗП – запам’ятовуючий пристрій

ВІС – велика інтегральна мікросхема

ПА – початкова адреса

КА – кінцева адреса

ДДНФ – досконала диз’юнктивна нормальна форма

ДКНФ – досконала кон’юнктивна нормальна форма