- •Глава 2 функциональные и преобразовательные элементы и устройства.

- •2.1 Логические устройства

- •2.1.1. Логические элементы на дискретных компонентах

- •2.1.2. Логические элементы в интегральном исполнении

- •2.2. Шифраторы и дешифраторы

- •2.3.Триггеры

- •2.4.Счетчики импульсов

- •2.5 Распределители импульсов

- •2.6 Операционные усилители

- •2.7. Устройства, реагирующие на уровни сигналов

2.3.Триггеры

Триггером называется функциональное устройство, имеющее два устойчивых состояния, одно из которых может быть установлено под действием входного сигнала. Одно из состояний триггера принимается за 0, другое — за 1. Каждое из этих состояний триггер способен сохранять неограниченно долго.

В зависимости от способа управления триггеры делятся на статические и динамические. Триггеры со статическим управлением переключаются при достижении входным сигналом порогового уровня. При динамическом управлении триггеры реагируют на перепад управляющего сигнала. Входы триггеров также делятся на статические и динамические.

По способу ввода информации триггеры делятся на синхронные и асинхронные. Если в асинхронных триггерах ввод информации происходит в момент изменения входного информационного сигнала, то в синхронных для ввода информации, кроме информационных сигналов, на входе нужен дополнительный командный импульс, который подается на синхронизирующий (тактирующий) вход. В интервалах между тактовыми импульсами синхронный триггер не реагирует на входные сигналы, в том числе и на помехи, что способствует его помехоустойчивости.

Входы триггеров, как и входные сигналы, делятся на информационные и управляющие. Информационные входы: RS (с раздельной установкой триггера в 0 и 1), JK (с раздельной установкой триггера в 1 и 0), T (счетный вход), D (информационный вход D- и D V-триггера) воспринимают поступающую на них информацию. Управляющие входы: V (подготовительный вход разрешения приема информации), С (исполнительный вход приема информации, вход синхронизации) служат для управления приемом информации.

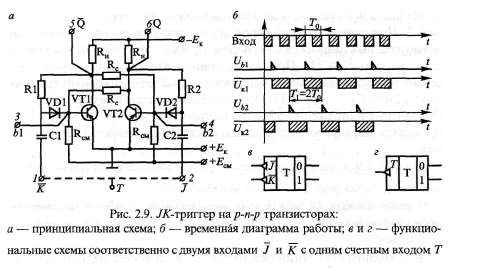

Асинхронные JK-триггеры с динамическими входами, использующими емкости в качестве элементов памяти или временной задержки (рис. 2.9) еще применяются в системах управления устройствами электроснабжения железных дорог.

Для образования входов J и К к каждому транзистору триггера (рис. 2.9, а) подключены емкостные потенциально-импульсные ячейки (к VT1 — ячейка VD1; CI; R1, к VT2 — VD2, С2, R2. Такие схемы, кроме формирования импульсов, выполняют также логическую операцию. Заряд емкостей С1 и С2 зависит от длительности сигналов на выходах Q и Q, что обеспечивает «запоминание» предыдущего состояния и необходимую блокировку входов на время переключения триггеров.

В исходном нулевом состоянии триггера транзистор VT1 закрыт,

на его выходе Q сигнал 1 (-Eк), транзистор VT2 открыт, на его выходе Q сигнал 0 (+ЕК), т.е. на выходах триггера сигнал 10. При подаче на вход J отрицательного потенциала происходит заряд конденсатора С2 (+ЕК—VT2—R2—С2—2), триггер готовится к переключению. Если теперь подать на вход J потенциал +ЕК (сигнал 0), произойдет разряд конденсатора С2 на базу транзистора VT2, который закроется. Возникший при этом ток базы транзистора VT1 [+ЕК—VT1—Rc—RK—(-Eк)] откроет транзистор VT1. На выходах Q и Q

появится сигнал 01, соответствующий состоянию 1 триггера, в котором последний будет находиться до следующего переключения. Сброс триггера в состояние 0 осуществляется путем подачи на вход К отрицательного потенциала, что приведет к заряду конденсатора С1 с последующим его разрядом на базу транзистора VT1 в момент подачи на К положительного потенциала. Транзистор VT1 закроется, VT2 — откроется, на выходах Q и Q будет сигнал 10, соответствующий состоянию 0 триггера.

Для

образования счетного входа T

объединяют входы J

и К обеих

импульсных схем. Допустим, что в начальный

момент триггер находился в состоянии

1; закрыт транзистор VT2

и открыт VT1.

На коллекторе VT1

напряжение Uк1

= +ЕК,

а

на VT2

— Uk2

=

-Ек

(рис.

2.9, б),

на

входе T

низкий потенциал -Ек,

конденсатор

С1 заряжен. При подаче на вход высокого

потенциала происходит разряд

через VD1

на базу VT1,

последний запирается, VT2

отпирается, триггер переходит в состояние

0.

через VD1

на базу VT1,

последний запирается, VT2

отпирается, триггер переходит в состояние

0.

На

рис. 2.9, б

приведена

диаграмма работы триггера со счетным

входом Т.

При

поступлении на счетный вход триггера

последовательности прямоугольных

импульсов с периодом

последний

будет переключаться с периодом

последний

будет переключаться с периодом

=

2

.

При

поступлении на вход T

отрицательного потенциала заряжается

один из конденсаторов С2 через открытый

транзистор VT2

или C1

— через VT1.

Повышение потенциала на входе до

нулевого значения напряжения базы

открытого транзистора (Uб1

или Uб2)

приводит к разряду соответствующего

конденсатора и переключению триггера.

=

2

.

При

поступлении на вход T

отрицательного потенциала заряжается

один из конденсаторов С2 через открытый

транзистор VT2

или C1

— через VT1.

Повышение потенциала на входе до

нулевого значения напряжения базы

открытого транзистора (Uб1

или Uб2)

приводит к разряду соответствующего

конденсатора и переключению триггера.

На рис. 2.9, в приведено условное изображение триггера со входами J и К а на рис. 2.9,г – со входом Т

.

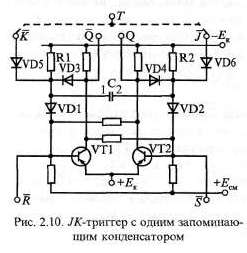

Универсальный JK-триггер на транзисторах с одним запоминающим конденсатором (рис. 2.10) используется в системе телеуправления «Лисна».

В исходном состоянии оба входа J, К должны находиться под потенциалом -Ек, т.е. иметь низкий уровень. Диоды VD5 и VD6 закрыты , напряжение на емкости С определяется потенциалами на прямом и инверсном выходах триггера Q и Q . Пусть триггер находится в состоянии логического нуля, т.е. транзистор VT1 закрыт, a VT2 открыт, на обкладке 2 конденсатора С высокий потенциал, а на обкладке 1 — низкий, поступающий через R1. Заряд конденсатора осуществляется по цепи [+ЕК—VT2—VD4—С—R1—(-Ек)]. Если на счетный вход Т, образованный путем объединения входов J и

К , теперь подать +ЕК (нулевой) потенциал, то потенциал обкладки 1 становится примерно равным нулю, а потенциал обкладки 2 повышается на величину напряжения заряженного конденсатора С, который через диод VD2 разряжается на базу транзистора VT2. Триггер переключается в состояние 1 (VT2—закрыт, VT1 — открыт), на выходах Q и Q — сигнал 01. Теперь потенциал +ЕК с коллектора VT1 поступает через диод VD3 на обкладку 1 конденсатора С. Диод VD5 при этом запирается. На обкладке 2 будет -Ек потенциал, конденсатор С при паузе (-Ек потенциал на счетном входе Т) заряжается. При очередном импульсе конденсатор разряжается через диод VD1 на базу транзистора VT1. Триггер сбрасывается в состояние 0, на выходах Q и Q триггера сигнал 10.

Входы R и S триггера используются для сброса триггера в состояние 0 (reset — сброс) или установки в состояние 1 (set — установка).

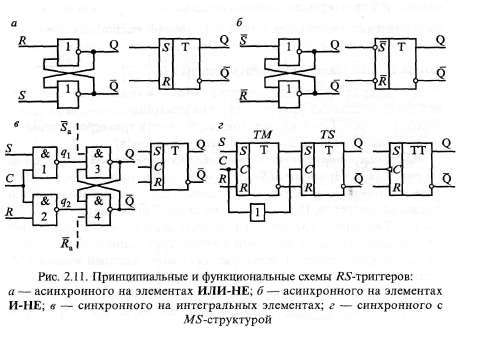

Асинхронный RS-триггер на интегральных логических элементах ИЛИ-НЕ (рис. 2.11, а), либо И-НЕ (рис. 2:11, б) не требует преобразования входной информации, поэтому устройство управления может отсутствовать. Допустим, что в исходном состоянии триггера сигналы на входах R и S отсутствуют, т.е. на оба входа подается 0 или 1, тогда на выходе триггера будет сигнал 01 или 10, что определяется только параметрами и внутренними сигналами самого триггера. Такая комбинация называется нейтральной, или режимом сохранения информации, в котором триггер может долго сохранять любое из своих устойчивых состояний. При входных комбинациях, когда переключающий сигнал поступает на один вход (сигнал 01 или 10), триггер переключается или подтверждает существующее состояние. Если переключающие сигналы подать на оба входа (11 при элементах ИЛИ-НЕ или 00 при элементах И-НЕ) в схеме может быть нарушен бистабильный режим. Ответная реакция триггера может быть непредсказуемой. Такие комбинации называются запрещенными, и они не должны допускаться в процессе работы триггера.

Синхронный

RS-триггер

на интегральных элементах получается

из асинхронного при подключении к входам

логических элементов RS-триггера

двух схем И-НЕ

и

одного синхронизирующего входа С

(рис.

2.11, в).

Логические

элементы 3 и 4 образуют ячейку памяти, а

1 и

2

— простейшую схему управления. При

отсутствии синхронизирующего сигнала

на входе С

элементы

1 и 2 закрыты, на внутренних выходах

и q2

сигнал

1, при этом триггер находится в режиме

хранения информации. Информация с

входов R

и

S

может

быть передана в триггер только при

сигнале 1 на входе С. Входы R

и

S

триггера

прямые, а входные сигналы инвертируются

элементами 1 и 2. Синхронные RS-триггеры

снабжаются вводами

и q2

сигнал

1, при этом триггер находится в режиме

хранения информации. Информация с

входов R

и

S

может

быть передана в триггер только при

сигнале 1 на входе С. Входы R

и

S

триггера

прямые, а входные сигналы инвертируются

элементами 1 и 2. Синхронные RS-триггеры

снабжаются вводами

и

и

для

асинхронного управления элементами

3 и 4, что позволяет расширить функциональные

возможности триггеров. При синхронном

управлении на входы

и

должен подаваться сигнал 1.

для

асинхронного управления элементами

3 и 4, что позволяет расширить функциональные

возможности триггеров. При синхронном

управлении на входы

и

должен подаваться сигнал 1.

В триггерах со статическим управлением возможна неоднократная смена состояний за время действия синхронизирующего (тактового) импульса. Такой недостаток отсутствует у триггеров с динамическим управлением и двухступенчатых триггеров.

RS-триггер с двухступенчатой или MS-структурой представлен на рис. 2.11, г. Принцип MS-структуры (master-slave, т.е. управляющий и управляемый, ведущий и ведомый) широко применяется при создании триггеров. При сигнале 0 на входе С информационные входы R и S ведущего TМ-триггера заперты, и он хранит информацию от предыдущего такта. Ведомый ТS-триггер, на синхронизирующем входе которого сигнал 1, повторяет состояние ведущей ячейки ТМ. Если на входе С сигнал 1, то в TTTМ-триггер заносится информация со входов R и S, ведомый триггер блокируется на время тактового импульса на входе С инвертором 1, связывающим входы С триггеровТМ и TS. По окончанию действия тактового импульса информация из первой ступени ТМ перезаписывается во вторую TS. Эти RS - триггеры широко используются в качестве ячеек памяти в оперативных запоминающих устройствах (ОЗУ).

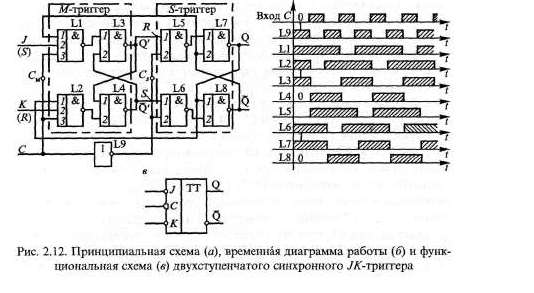

Интегральные JK-триггеры обладают универсальными функциональными возможностями. При всех значениях входного сигнала, кроме 1 на входах J и К, они действуют подобно рассмотренным выше .RS-триггерам (вход J играет роль S-выхода, а вход К — роль R- выхода). Входной сигнал, приходящий на входы J и К одновременно, не нарушает бистабильный режим. Для реализации этого свойства в JK-триггере используются сигналы обратной связи с выходов Q и Q

для блокировки одного из информационных входов в зависимости от состояния триггера в предыдущем такте.

Базовая схема такого .JK-триггера (рис. 2.12, а) выполнена на основе двух синхронных .RS-тригтеров L1—L4 (М-тригтер), L5—L8 (S-триггер). Нетрудно убедиться , что сигнал 1 на входах S (установка в1) и R (сброс в0) проходят только, если одновременно присутствует сигнал 1 и на входе С (СМ, CS). При сигнале 1 на входе См М-триггер принимает состояние, зависящее от сигналов на входах J к К. Инверторы L5 и L6 при этом закрыты сигналом 0, поступающим с инвертора L9. При сигнале 0 на входе См закрыты L1 и L2, а состояние L5, L6 и S-триггера зависит от сигналов, поступающих с М-триггера, т.е. происходит перезапись информации с М- в S-триггер.

Допустим, что в исходном положении оба триггера находятся в состоянии 0, при этом на инверсных выходах Q и Q1 будет сигнал 1 (высокий потенциал), а на прямых выходах Q и Q1 — сигнал 0 (низкий

потенциал). С выхода Q S-триггера на вход L2 поступает сигнал О, запирающий L2 независимо от сигнала на его входе К.

Теперь допустим, что на входы Jи С поступает 1, а на вход К — сигнал 0. Элемент L1 открывается и на его выходе появляется 0, М-триггер переходит в состояние 1 (сигнал 1 на выходе Q1). Элементы L5 и L6 при этом закрыты сигналом 0 с инвертора L9, .S-триггер сохраняет состояние 0. Если теперь на вход С поступает сигнал 0, то инверторы L1 и L2 закрываются, а сигнал 1 с выхода L9 поступает на L5 и L6. На входах L5 совпадают сигналы 1, что приводит к его открытию. Сигнал 0 с выхода L5 поступает на L7, S-триггер переключается в состояние 1.

Аналогично триггер работает при поступлении сигнала 1 на входы С и К, а на вход J — сигнала 0. Если на входах J и К одновременно присутствует сигнал 1, то по входу С триггер работает как счетный: при первом тактовом импульсе он переходит в состояние 0, при втором в — 1, далее процесс повторяется. Диаграмма работы JK-триггера приведена на рис. 2.12, б, его функциональная схема — на рис. 2.12, в.

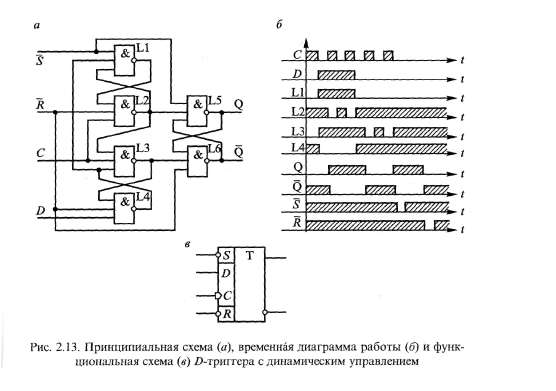

D-триггеры с динамическим управлением могут быть выполнены на базе нескольких RS-триггеров (рис. 2.13, а). Такой триггер состоит из трех RS-триггеров: основного на элементах L5 и L6; двух вспомогательных на элементах LI, L2 и L3, L4, образующих схему управления.

Переключение D-триггера происходит на переднем фронте тактового импульса, поступающего на синхронизирующий вход С. Информация на вспомогательные триггеры записывается, когда на входе С сигнал 0. При этом инверторы L2 и L3 принудительно заперты, а внутренняя связь между вспомогательными триггерами разорвана. С инверторов L2 и L3 на входы элементов L5 и L6 основного триггера поступают сигналы 1, при этом триггер сохраняет предыдущее состояние. Состояние инверторов L1 и L4 зависит от сигнала на входе D. При сигнале 0 на нем инвертор L4 закрыт, a L1 — открыт (рис. 2.13, б). При сигнале 1, наоборот, L4 — открыт, так как на его второй вход поступает сигнал 1 с инвертора L3, а инвертор L1 закрыт. При поступлении на вход С сигнала 1 оба вспомогательных триггера устанавливаются в положение, при котором L1 и L4 сохраняют свое прежнее состояние. Выходной триггер переключается в новое состояние сигналами с L2 и L3.

После переключения триггера на переднем фронте синхронизирующего импульса, поступающего на вход С, оказывается выключенным из работы вход D в результате действия связей между вспомогательными триггерами. Если после сигнала 1 на входе С схема зафиксировалась в состоянии, при котором открыт инвертор L2, то инверторы L1 и L3 закрыты независимо от состояния L4, а значит, и от сигнала на входе D. Если схема зафиксировалась, когда L3 открыт, то L4 будет закрыт при любом сигнале на входе D.

Для любой работы триггера необходимо, чтобы сигнал на вход D поступал несколько раньше, чем сигнал 1 на вход С. При асинхронном управлении состояние выходного триггера зависит от того, на какой вход подан сигнал 0. Асинхронный сигнал подается также на элементы управляющих триггеров так, чтобы подтверждалось состояние выходного триггера. Например, при сигнале 0 на входе S блокируется инвертор L1 в течение тактового импульса и на выходе инвертора L2 формируется 0, который в свою очередь блокирует инвертор L3.