- •Глава 2 функциональные и преобразовательные элементы и устройства.

- •2.1 Логические устройства

- •2.1.1. Логические элементы на дискретных компонентах

- •2.1.2. Логические элементы в интегральном исполнении

- •2.2. Шифраторы и дешифраторы

- •2.3.Триггеры

- •2.4.Счетчики импульсов

- •2.5 Распределители импульсов

- •2.6 Операционные усилители

- •2.7. Устройства, реагирующие на уровни сигналов

2.2. Шифраторы и дешифраторы

Шифраторы и дешифраторы являются преобразователями кодов. Основой для их построения являются рассмотренные в п. 2.1 логические элементы И, ИЛИ на полупроводниковых диодах и интегральные схемы И-НЕ, ИЛИ-НЕ. Шифраторы и дешифраторы могут быть выполнены на контактных элементах релейного типа.

Для

передачи информации широко используются

комбинаторные коды, основанные на

математических сочетаниях. На входе и

выходе устройств телемеханики информация

довольно часто представляется в виде

распределительного кода

(каждому сообщению соответствует

одна комбинация из множества N).

(каждому сообщению соответствует

одна комбинация из множества N).

Шифраторы

служат

для преобразования распределительного

кода

в

коды двоичный, троичный, ..., десятичный,

на одно сочетание

с

произвольными т

и п.

с

произвольными т

и п.

Шифратор

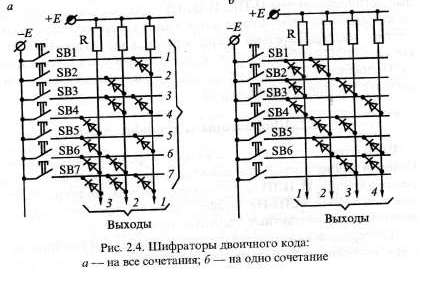

двоичного кода на все сочетания (рис.

2.4, а),

преобразующий

код

в

трехэлементный (трехразрядный) двоичный

код тп(т

= 2, п =

3), составлен из трех диодных схем ИЛИ.

Выходы

логических схем являются выходами

шифратора (1,

2, 3). Каждая

логическая схема ИЛИ

состоит

из резистора R

и четырех диодов, подключенных к

вертикальной шинке, являющейся

выходом схемы. Диоды схем подключены к

горизонтальным шинкам, являющимся

входами шифратора. При замыкании

одного из семи ключей (SB1—SB7)

на соответствующую входную шинку

подается отрицательный потенциал,

который через диоды, соединяющие

горизонтальные и вертикальные шинки

схемы, поступает на один, два или все

три выхода шифратора. Отрицательный

потенциал на выходе соответствует

1, положительный — 0. Так, при замыкании

ключа SB1сигнал

1 будет только на выходе 1,

а

на выходах 2

и

3

будет

сигнал 0 (+E).

При отсутствии информации на входе

шифратора (ни один ключ не замкнут)

на выходе будет нулевая комбинация 000,

которая не используется. Кодовые

комбинации шифратора приведены в табл.

2.1.

в

трехэлементный (трехразрядный) двоичный

код тп(т

= 2, п =

3), составлен из трех диодных схем ИЛИ.

Выходы

логических схем являются выходами

шифратора (1,

2, 3). Каждая

логическая схема ИЛИ

состоит

из резистора R

и четырех диодов, подключенных к

вертикальной шинке, являющейся

выходом схемы. Диоды схем подключены к

горизонтальным шинкам, являющимся

входами шифратора. При замыкании

одного из семи ключей (SB1—SB7)

на соответствующую входную шинку

подается отрицательный потенциал,

который через диоды, соединяющие

горизонтальные и вертикальные шинки

схемы, поступает на один, два или все

три выхода шифратора. Отрицательный

потенциал на выходе соответствует

1, положительный — 0. Так, при замыкании

ключа SB1сигнал

1 будет только на выходе 1,

а

на выходах 2

и

3

будет

сигнал 0 (+E).

При отсутствии информации на входе

шифратора (ни один ключ не замкнут)

на выходе будет нулевая комбинация 000,

которая не используется. Кодовые

комбинации шифратора приведены в табл.

2.1.

Из

табл. 2.1 видно, что шифратор кода на все

сочетания (см. рис. 2.4, а)

является

преобразователем чисел десятичной

системы (номер ключа — десятичное

число) в числа двоичной системы (комбинации

сигналов на выходах).

Из

табл. 2.1 видно, что шифратор кода на все

сочетания (см. рис. 2.4, а)

является

преобразователем чисел десятичной

системы (номер ключа — десятичное

число) в числа двоичной системы (комбинации

сигналов на выходах).

Шифратор

кода на одно сочетание, показанный на

рис. 2.4, б,

осуществляет

преобразование кода

в

код

в

код

Он

состоит из шести входных ключей (SB1—SB6)

и четырех схем ИЛИ, выходы которых (1,2,

3, 4) являются

выходами шифратора. Исходная комбинация

на выходах шифратора 0000 (+Е

на

всех выходах). При замыкании любого

ключа на двух выходах появляются сигналы

1, на двух других — 0. Например, при нажатии

ключа SB1

на выходах 1

и

2

будут

сигналы 1 и 1, на выходах 3

и

4

—

0 и 0 (кодовая комбинация 1100). Кодовые

комбинации шифратора приведены в табл.

2.2.

Он

состоит из шести входных ключей (SB1—SB6)

и четырех схем ИЛИ, выходы которых (1,2,

3, 4) являются

выходами шифратора. Исходная комбинация

на выходах шифратора 0000 (+Е

на

всех выходах). При замыкании любого

ключа на двух выходах появляются сигналы

1, на двух других — 0. Например, при нажатии

ключа SB1

на выходах 1

и

2

будут

сигналы 1 и 1, на выходах 3

и

4

—

0 и 0 (кодовая комбинация 1100). Кодовые

комбинации шифратора приведены в табл.

2.2.

Если в схемах рис. 2.4 поменять полярность источника питания и подключения диодов, то получим шифраторы инверсного кода соответственно на все и на одно сочетание.

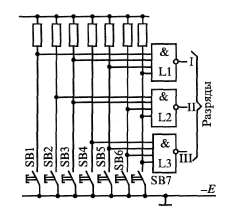

Шифратор двоичного кода на все сочетания, выполненный на микросхемах типа И-НЕ, показан на рис. 2.5. При разомкнутых контактах ключей SB1 ... SB7 на входы логических схем LI, L2, L3 поступает сигнал 1 (+Е), инверторы этих схем открыты и на выходах I, II, III будут сигналы 0 (комбинация 000). При замыкании одного из ключей сигнал 0 (-E) поступает на одну, две или все схемы, произойдет переключение инверторов (закроются инверторы схем, на которые поступил сигнал 0) и на выходах будут сигналы 1. Так, при замыкании ключа SB1 сигнал 0 поступит на вход элемента L1, инвертор которого закроется и на выходе будет сигнал 1 (комбинация 001). Комбинации сигналов на выходах при замыкании ключей полностью соответствуют табл. 2.1.

Дешифраторы служат для преобразования кода, поступающего

на

их входы, в распределительный код

.

Дешифраторы

составляют из логических схем И,

количество которых соответствует числу

выходов N

дешифратора.

Число входов соответствует числу

элементов (разрядов) комбинаций

входного кода.

.

Дешифраторы

составляют из логических схем И,

количество которых соответствует числу

выходов N

дешифратора.

Число входов соответствует числу

элементов (разрядов) комбинаций

входного кода.

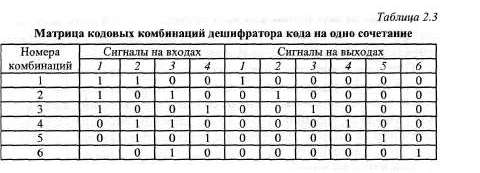

Дешифратор

двоичного кода на одно сочетание

представлен

на рис. 2.6, а.

Он

состоит из шести диодных логических

схем И,

каждая из которых имеет два входных

диода и резистор. Шинки 1,

2, Зи4 являются

входами дешифратора. К ним подключаются

диоды схем И таким образом, что совпадение

сигнала 1 (-E)

при каждой кодовой комбинации возможно

только на диодных входах одной схемы

И.

На выходе этой схемы будет также сигнал

1. При этом на всех других выходах будет

сигнал 0. Все входные и выходные комбинации

сведены в табл. 2.3. При подаче на

входы дешифратора, например, комбинации

№ 2 — 1010 сигнал 1 будет на входах 1

и

3,

а

на входах 2 и 4—

0. Совпадение сигналов 1 произойдет на

диодах схемы И2,

на выходе которой будет также сигнал

1. На выходах всех других логических

схем будет сигнал 0, так как хотя бы один

из диодных входов этих схем подключен

к шинке 2

или

4

с

высоким потенциалом, следовательно,

диод этого входа будет открыт.

представлен

на рис. 2.6, а.

Он

состоит из шести диодных логических

схем И,

каждая из которых имеет два входных

диода и резистор. Шинки 1,

2, Зи4 являются

входами дешифратора. К ним подключаются

диоды схем И таким образом, что совпадение

сигнала 1 (-E)

при каждой кодовой комбинации возможно

только на диодных входах одной схемы

И.

На выходе этой схемы будет также сигнал

1. При этом на всех других выходах будет

сигнал 0. Все входные и выходные комбинации

сведены в табл. 2.3. При подаче на

входы дешифратора, например, комбинации

№ 2 — 1010 сигнал 1 будет на входах 1

и

3,

а

на входах 2 и 4—

0. Совпадение сигналов 1 произойдет на

диодах схемы И2,

на выходе которой будет также сигнал

1. На выходах всех других логических

схем будет сигнал 0, так как хотя бы один

из диодных входов этих схем подключен

к шинке 2

или

4

с

высоким потенциалом, следовательно,

диод этого входа будет открыт.

Дешифратор двоичного кода на все сочетания тп (рис 2.6, б), где т - 2, п = 3, состоит из восьми логических схем И. Каждому разряду двоичного числа на входе дешифратора соответствуют две кодовые шинки: а0 и а1— разряд I; b0 и b1 — разряд И; с0 и cl — разряд III.

На одну из двух шинок каждого разряда подается прямой сигнал, на другую — инверсный. Каждой комбинации кода соответствует определенная диодная схема И и выход дешифратора.

При совпадении отрицательных потенциалов на всех трех входах одной из схем на ее выходе будет также отрицательный потенциал (сигнал 1). Если принять, что нулю соответствует комбинация на шинках разряда 10, а единице — 01, то кодовой комбинации 011 на кодовых шинках входов дешифратора будет соответствовать комбинация сигналов 10, 01, 01. При это сигнал 1 будет на шинках а1,b1,с1, а сигнал 0 — на шинках аО, b0, сО. Совпадение сигналов 1 произойдет на входах схемы И выхода 3, следовательно, сигнал 1 будет на выходе 3. На остальных выходах будут сигналы 0. Работа дешифратора при других комбинациях приведена в табл. 2.4.

Таблица 2.4 Матрица кодовых комбинаций дешифратора кода на все сочетания

Выход дешифратора с сигналом 1 |

Кодовая комбинация |

Выход дешифратора с сигналом 1 |

Кодовая комбинация |

||||

Сигналы на кодовых шинах |

Сигналы на кодовых шинах |

||||||

Разряд III |

Разряд II |

Разряд I |

Разряд III |

Разряд II |

Разряд I |

||

0 |

0/ 10 |

0 /10 |

0 /10 |

4 |

I/ 01 |

0 /10 |

0 /10 |

1 |

0 /10 |

0 /10 |

I/ 01 |

5 |

1 01 |

0 /10 |

1/ 01 |

2 |

0/ 10 |

1/ 01 |

0/ 10 |

6 |

I 01 |

I /01 |

0 /10 |

3 |

0 /10 |

1/ 01 |

1/ 01 |

7 |

I/ 01 |

1/ 01 |

1 /01 |

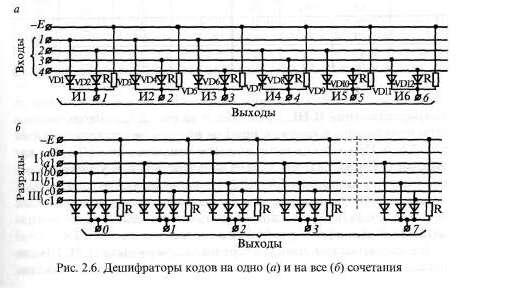

Дешифратор двоичного кода на все сочетания, выполненный на микросхемах типа И-НЕ, представлен на рис. 2.7, а. Входы микросхем подключены к кодовым шинкам по тому же правилу, что и на рис. 2.6, в. При этом на выходах логических схем L0—L7 будут инверсные сигналы, поэтому в схеме дешифратора предусмотрены дополнительно инверторы L8—L15. При совпадении отрицательных потенциалов на всех трех входах логической схемы, например L7, на ее выходе будет положительный потенциал, а на выходе L15 — отрицательный. Дешифратор работает в соответствии с табл. 2.4.

В рассмотренном дешифраторе в каждом разряде (I, II, III) для передачи прямого и инверсного сигналов используют две шинки.

В промышленных интегральных микросхемах с целью уменьшения числа выходов с одного кристалла применяют схемы с одной входной шинкой на разряд. Необходимую инверсию осуществляют непосредственно в кристалле (рис. 2.7, б) с помощью инверторов N1—N6.

С

увеличением числа разрядов двоичного

кода в каждой схеме И возрастает число

входов, а также число выходов дешифратора,

т.е. схем И.

Для уменьшения числа входов в одной

логической схеме и снижения общего

числа схем в дешифраторах с большим

числом разрядов применяют

многоступенчатые схемы. На рис. 2.8, а

показана

структурная схема двухступенчатого

дешифратора. Разряды числа или элемента

кода разбивают на две равные части при

их четном количестве или примерно

равные, если их количество нечетное.

Выходы дешифраторов первой ступени,

число которых

у первого дешифратора и N2

— у второго, являются входами дешифратора

второй ступени. Число выходов

дешифратора второй ступени N

равняется

произведению числа выходов дешифраторов

первой ступени (N=

у первого дешифратора и N2

— у второго, являются входами дешифратора

второй ступени. Число выходов

дешифратора второй ступени N

равняется

произведению числа выходов дешифраторов

первой ступени (N=

N2).

При этом восьмиэлементный двоичный код

может быть разбит на две группы: 1—4-й и

5—8-й элементы. С помощью дешифратора

каждая группа двоичного кода преобразуется

в шестнадцатеричный код.

N2).

При этом восьмиэлементный двоичный код

может быть разбит на две группы: 1—4-й и

5—8-й элементы. С помощью дешифратора

каждая группа двоичного кода преобразуется

в шестнадцатеричный код.

На

рис. 2.8, б

приведена

принципиальная схема двухступенчатого

дешифратора четырехразрядного двоичного

кода. На шинки а0, al,

b0,

b1,

с0, c1,

d0,

1\ подается

сигнал двоичного кода (на каждую пару

шинок прямой и инверсный сигнал). При

этом двоичному нулю соответствует

комбинация 10, а двоичной единице — 01.

Каждой входной комбинации двоичных

сигналов соответствует определенная

комбинация сигналов на выходах

дешифраторов первой ступени (двухразрядный

четверичный код). На выходе дешифратора

второй ступени возникает определенная

комбинация кода

(сигнал

1 на одном выходе, на остальных пятнадцати

сигнал 0).

(сигнал

1 на одном выходе, на остальных пятнадцати

сигнал 0).

Пусть на входе дешифратора задана кодовая комбинация 0101 (двоичное число пять). На выходных шинках будет комбинация прямых и инверсных сигналов 10 01 10 01. Так как счет разрядов ведется справа налево, то комбинация 01 будет на шинках дешифратора а0, а1 (разряд1), 10 — наb0,b1 (разрядП),01 — нас0,с1 (разрядIII), 10 — на d0, d1 (разряд IV). Таким образом, сигнал 1 (низкий потенциал) будет на шинках a1, b0, c1, d0, а значит, появится на выходах 1 дешифраторов первой ступени 1а и 16. На кодовых шинках дешифратора второй ступени сигнал 1 будет на шинках e1 и f1, к которым подключены диоды пятой логической схемы, на выходе которой появится сигнал 1, на остальных пятнадцати сохранится сигнал 0.

При использовании интегральных микросхем также целесообразно применять многоступенчатые схемы дешифраторов. Экономия заключается в том, что в последней ступени дешифратора используются двухвходовые элементы И-НЕ. Обычно уже двухступенчатая схема позволяет значительно сократить число корпусов микросхем.