- •1.Конъюнкция, дизъюнкция және терістеу функцияларын іске асыратын логикалық элементтер (лэ). Ақиқат кестелері, жазылу түрлері.

- •2. Шеффер штрихі, Пирс жебесі функцияларын іске асыратын логикалық элементтер (лэ). Ақиқат кестелері, жазылу түрлері.

- •3. Және, немесе, емес логикалық элементтердің схемалық жиналуы және олардың негізгі параметрлері.

- •4. Модулі 2 бойынша қосындылауыш және жартылай қосындылауыш. Шартты графикалық белгіленуі, ақиқат кестесі, кез-келген базистегі схемасы.

- •9. Комбинациялық құрылғының синтездеу мәселесін қою. Оны синтездегенде негізгі кезеңдері.

- •21. Микропроцессор, микропроцессорлық жинақ, микро-эем деген электрондық құрылғылардың анықтамаларын беріңіз. Қысқаша мп-дің даму тарихын айтып беріңіз.

- •21. Микропроцессор, микропроцессорлық жинақ, микро-эем деген электрондық құрылғылардың анықтамаларын беріңіз. Қысқаша мп-дің даму тарихын айтып беріңіз.

- •24. Программалық логика негізіндегі мп-ні басқаратын құрылғының қарапайым құрылымы. Оның жақсы жақтары және кемшіліктері.

- •23. Ақпараттық логика негізіндегі мп-ні басқаратын құрылғының қарапайым құрылымы. Оның жақсы жақтары мен кемшіліктері

- •27. 8 Разрядты біркристалды мп-нің құрылысы. Негізгі түйіндерінің атқаратын қызметі.

- •28. Біркристалды мп –нің командасының циклі. Машиналық циклдер мен тактілердің атқаратын қызметтері.

- •29.Біркристалды мп құрамына кіретін негізгі регистрлердің атқаратын қызметтері.

- •28.Біркристалды мп –нің командасының циклі. Машиналық циклдер мен тактілердің атқаратын қызметтері.

- •32.Біркристалды 8-разрядты мп-нің командалар жүйесі. Бір немесе екі операндтармен арифметикалық операциялар орындайтын командалар тобы

- •33. Біркристалды 8-разрядты мп-нің командалар жүйесі. Бір немесе екі операндтармен логикалық операциялар орындайтын командалар тобы

- •34. Біркристалды 8-разрядты мп-нің командалар жүйесі. Арнайы командалар жүйесі.

- •Деректер регистрлері. (Регистр данных)

- •38)Біркристалды 8-разрядты мп-ніңбелгілерригистріразрядтарыныңатқаратынқызметі.

Деректер регистрлері. (Регистр данных)

Деректер операциясында қатысушыларды сақталу үшін 8 разрядты жеті регистр қарастырылады. Аккумулятор деп ат-н А регистрі сыртқы құрылғылармен ақпарат алмасу үшін қолданылады, ариф-қ, лог-қ операцияларды орындау кезінде ол операнданың көзі болып табылады, және оған орындалған операцияның нәтижесі орналасады. Қалған алты B,C,D,E,H, L регистрлері жалпы тағайындалу регистрлерінің (регистр общ. назначения РОН) блогын құрайды. Бұл регистрлер жалғыз 8-разрядты регистр ретінде де қолданылады. Егер 16 разрядты екілік сандарды сақтау керек болса, олар жұп болып қосылады BC, DE, HL.

Топтама көрсеткіші (указатель стека) SPрегистрі (16-разр.). топтама(стек) деп аталатын жадының ерекше түрін адрестеуі үшін қолданылады.

Командалар санауышы(счетчик ком-сы) РС регистрі адресін сақталу үшін қолданылады.

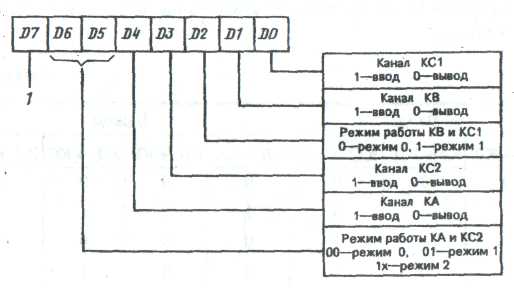

37)Параллель шеткері (перифериялық) адаптердің құрылымдық схемасы, жұмыс істеу режимдері, басқарушы сөзінің форматы.

Құрылымдық схема.

Режим 0. Бұл режимде КА,КВ,КС1 және КС2 кез келген ақпарат кірісі немесе шығысына қойылуы мүмкін.

Режим 1. Бұл режимде деректер тарату КА және КВ каналы арқылы жүреді, ал КС каналы негізінде басқару сигналын шығару және қабылдау үшін қолданады.

Режим 2. бұл режимде текКА жұмыс істей алады. Басқарушы сигналдардың бұл режимінде КС арнасының келесі разряды қолданылады

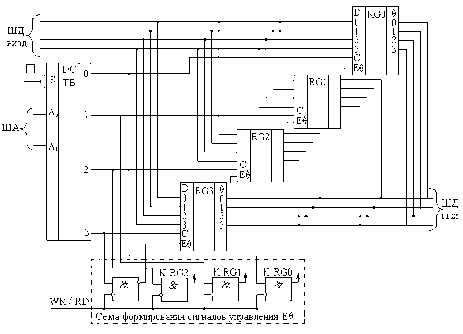

Шиналық қалыптасулар және порттар шина мәліметтері мен тікелей және уақыт арасындағы буферленген алмасуын орындайды. Бұдан да күрделі операциялар периферийлік адаптерлердің көмегімен жүзеге асады. Адаптерлердің программаланулары оларға параллель мәліметтермен алмасу жасайтын схемаларда INTEL 8255А параллель адаптерінің базалық құрылымы қолданылады.Мысалға, параллель периферийлік адаптердің 3 екі бағытталған сегіз разрядты РА,РВ,РС порттары бар ,РС порты екі төрт разрядты каналға бөлінген.А,В,С каналдарымен шина мәліметтері арасындағы ақпарат алмасуы ВД мәліметтер буфері арқылы жүзеге асады.

Оқу/жазуды басқару блогы оқу және жазу RD,WR стробтарын,түсіру сигналы RESET, адаптер таңдау сигналы CS, үлкен разрядтарды декодтау арқылы алынатын оның адресі және екі А және Ао кішкене разряд (ішкі регистрлердің адресациялары үшін) алады.Адрестелетін объектілер саны бес:үш порт А,В,С басқаратын сөз регистрі, С портының биттерін орнату/түсіру командасы BSR.

Таблица бойынша А,Ао адресі 11 тең. Ол басқаратын сөз регистрі немесе BSR сәйкес келеді.Бұл адресс бойынша оқуға болмайды, тек жазуға болады. Порттар үш режимде жұмыс істейді(0,1,2), В порты тек 0 мен 1, ол С порты А және В портына тәуелді.0 режимі – квитированиясыз бір бағытталған енгізу/шығару. Бұл режимде А және В, сонымен қатар С портының бос линиялары жұмыс істей алады. 1 режимі квитированиямен бір бағытталған енгізу/шығару.2 режимі квитированиямен екі бағытталған енгізу/шығару.

38)Біркристалды 8-разрядты мп-ніңбелгілерригистріразрядтарыныңатқаратынқызметі.

Бұл 5-разрядты регистр, кейбір операциялардың орындалуын сандармен көрсететін нақты белгілерін сақтау үшін арналған.Бұл регистрдің 5 триггері төмендегідей:

Тасымалдау триггері (триггер переноса) Тс арифметикалық операцияны орындауда үлкен разрядтан тасымалдауы кезіндегі жағдайға орнатылады, ал ығысу операциясы кезінде аккумулятордағы разрядтың жоғарлайтын құрамына сәйкес жағдайға орнатылады.

Нольдік триггер Tz, АЛҚ(ариф. Лог. Құр-ғы) операциясының немесе регистрдің құрамындағы қосылу операциясы нольге тең болғанда, «1» жағдайына сәйкес орнатылады.

Белгі триггері (триггер знака) Ts, АЛҚ операциясының нәтижесінің үлкен разрядына сәйкес немесе регистрдің құрамындағы қосылу операциясына сәйкес жағдайға орнатылады.

Жұптылық триггері(триггер четности) Тр, нәтиже разрядындағы бірліктер саны жұп болғанда, «1» жағдайға орнатылады.

Қосымша тасымалдау триггері Tv, операцияның орындалу кезінде туындайтын 4-ші разрядты тасымалдауын сақтайды.

39) Жадтайтынқұрылғылардың (ЖҚ) жіктелуіменпараметрлері. ТұрақтыжәнеоперативтіЖҚ-лар.

Қазіргі ЭВМ (соныңішіндедербес) үлкенсыйымдылықтыңматрицалықОЗУсандықдеректердіңнемесебағдарламаныңсақталуыүшінпайдаланылады. Қызмет және қосалқы бағдарламаның бөлігі (жиынтық операцияға инициализация, тұжырымның енгізуінің) өзгермейтін "мәтін" және тұрақты сақталуға түпкілікті жазылуы керек. Өзінің сақталуы үшін қорек көзінен ажыраған кезде де (қосылуы кезінде қалпына келетін) ақпарат сақталатын түпкілікті ЖҚ талап етіледі. Ағымдағы бағдарламаның және деректердің үлкен бөлігі, ереже сай, үздіксіз жаңаланады және өзінің сақталуы үшін шұғыл ЖҚ(ОЖҚ) сұралады, ақпарат жазбасының мүмкіндігін қарастырады: барлық мәлімет қорек көзінен ажыратылғаннан кейін жоғалады немесе өшіріледі. 5.1 сурет

ЖҚ-ң негізгіпараметрлері: сыйымдылық(жадыныңұяшықсаны), разрядтылықжәнеайналымныңуақытыболыптабылады.

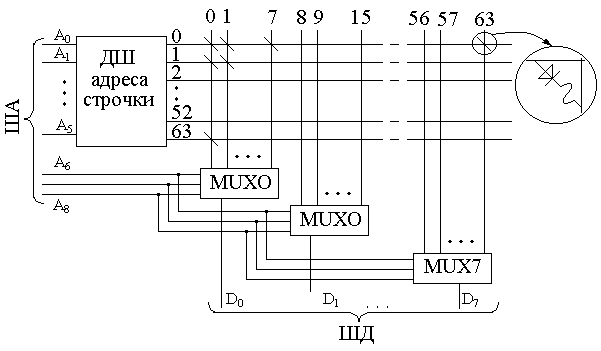

40)Тұрақтыжадтайтынқұрылғының (ТЖҚ) құрылымы, жиналуқағидасыжәнежұмысістеу.

ТЕҚ-ның құрылым ұстанымдарын және атқарушы қызметін жақсы көркемдейді, 5.2 суретте ТЕҚ-ның сыйымдылығы 29=512 байт =4096 бит болатын 8 разрядты типтік құрылымы бейнеленген.

Матрицаның түйіндерінде 64 х 64 шалаөткізгіш құрылғысы орналастырылады (диод, транзистор) плавкамен қойылуымен (PROM) немесе олсыз(ROM); әрбір бұрышта адрестік және дәрежелі шиналар арасындағы контакт шалаөткізгіштің аспабы және қойылымдардың жоюылуы арқылы бұзылуы мүмкін. ТЕҚ-ның PROM түрінде матрицаның түйіндері электрлік зарядты жақсы сақтайтын кремний нитридінің қабатымен жабылады. Айналымның уақыты БИС ЗУ-дың дайындалу технологиясына байланысты және полярлы ТЕҚ үшін 20….50 нс құрайды, ал биполярлы үшін - 200….600 нс.

41)Статикалықоперативтіжадтайтынқұрылғылардың (ОЖҚ) жиналуқағидасы. Еріктіжәнетізбектіқатынау (доступ).

5.3Сурет

Матрицалық

ОЖҚ-ның құрылуы кезіндегі негізгі

тапсырмасы : бір шинадағы деректермен

кез келген ұяшыққа ақпаратты енгізу/шығару

болып табылады. Бұл тапсырма негізінде

қарапайым түрде мултиплексирлеу

көмегімен де шешіледі-барлық регистрлардың

кірістерінің кіріс шинасына қосылуы

демультиплексор арқылы, ал шығысы-кірісіне

қажетті ұяшық жадысының номері туралы

адрестік ақпарат келіп

отыратын,мультиплексердің шығысы

арқылы жүзеге асады. 5.3-суретте бұл

тапсырманың мысал ретінде 3 стабильді

кірісі бар регистр үшін мүмкін болатын

шешімдерінің бірі көрсетілген.(

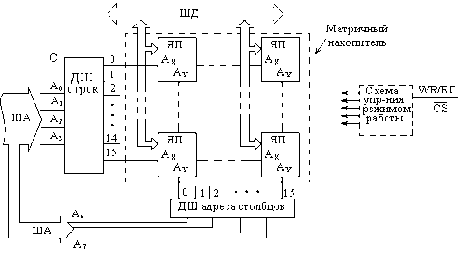

5.4Сурет

Екінші

тапсырма- бұл бір екібағытты деректер

шинасын ұйымдастыру, ол реалды МП

жүйелерінде орын алады. Бұл тапсырманы

шешу мысалын 5.4Суреттен көруге болады.Бұл

жағдайда әр ОҚЖ регистрі екібағытты

ақпараттық шинасы және екі Ах

және Ауадрестік

кірісі бар ұяшық ретінде қарастырыла

алады.

Сонда матрицалық үлкен көлемді ОҚЖ-ның

қажет ұяшыққа адерсациялау проблемасы

Ахжолынан

және Аубағанынан

құралған екі дешифратор көмегімен

шешіледі.(5.5сурет). Бұл типтегі ОҚЖ-да

регистрді шақыруда еркін тәртіп(доступ)

болуы мүмкін. Ал жүйелі тәртіптегі

ОҚЖ-да тек қана адрестердің өсу және

кему ретінде ғана болуы мүмкін.Адрестер

бөлек реверсивті санауыштармен

қалыптасқанда,бұл стектің көрсеткіші

болып табылады

5.5Сурет