Конспект лекції

МУЛЬТИПЛЕКСОРИ І ДЕМУЛЬТИПЛЕКСОРИ

Мультиплексори

Цифровий мультиплексор або селектор даних – комбінаційна логічна схема, яка являє собою керований перемикач, який приймає декілька інформаційних сигналів, вибирає один із них і передає його на вихід (рис. 1).

Рис. 1. Функціональна схема мультиплексора

Номер під’єднаного входу дорівнює числу (адресі), яке визначається комбінацією логічних значень на входах керування. Крім інформаційних входів і входів керування, схема мультиплексора містить вхід дозволу, при подачі на який активного рівня, мультиплексор переходить в пасивний стан, при якому сигнал на виході зберігає постійне значення незалежно від значення інформаційних і керуючих сигналів. Число інформаційних входів у мультиплексора, як правило, є 2, 4, 8 або 16. Якщо, наприклад, у мультиплексора 16 входів і до кожного із них під’єднано 16 джерел числових сигналів – генераторів послідовних цифрових слів, то байти із будь-якого із них можна передавати на єдиний вихід. Для вибору будь-якого із 16 каналів необхідно мати 4 входи вибору (24=16), на які подається двійкова адреса каналу. Так, для передачі даних з каналу номер 10 на входи вибору необхідно подати код 1010.

Мультиплексори застосовуються, наприклад, у мікропроцесорах для видачі на одні і ті ж виводи адреси і даних, що дає можливість істотно скоротити загальну кількість виводів мікросхеми; у мікропроцесорних системах керування мультиплексори встановлюються на віддалених об’єктах для можливості передачі інформації по одній лінії від декількох встановлених на них датчиків.

Базовий мультиплексор з двома входами даних

Розглянемо мультиплексор з двома входами даних І0 і І1 та входом вибору А. Логічне значення, подане на вхід А, визначає, який із елементів І (кон’юнкторів) буде пропускати на свій вхід дані, які через елемент АБО поступають на вихід D.

Таблиця 1

А

І0

І1

D

0

1

0

1

1

0

1

1

Користуючись булевою алгеброю можна записати наступний вираз для виходу сигналу

![]() .

(1)

.

(1)

При

А=0 вираз набуває значення

![]() – працює нульовий елемент І,

тобто сигнал

на виході D

буде ідентичний сигналу зі входу

І0.

Якщо ж А=1, то вираз набуває значення

– працює нульовий елемент І,

тобто сигнал

на виході D

буде ідентичний сигналу зі входу

І0.

Якщо ж А=1, то вираз набуває значення

![]() – працює перший елемент І,

тобто сигнал

на виході D

буде ідентичний сигналу зі входу

І1.

– працює перший елемент І,

тобто сигнал

на виході D

буде ідентичний сигналу зі входу

І1.

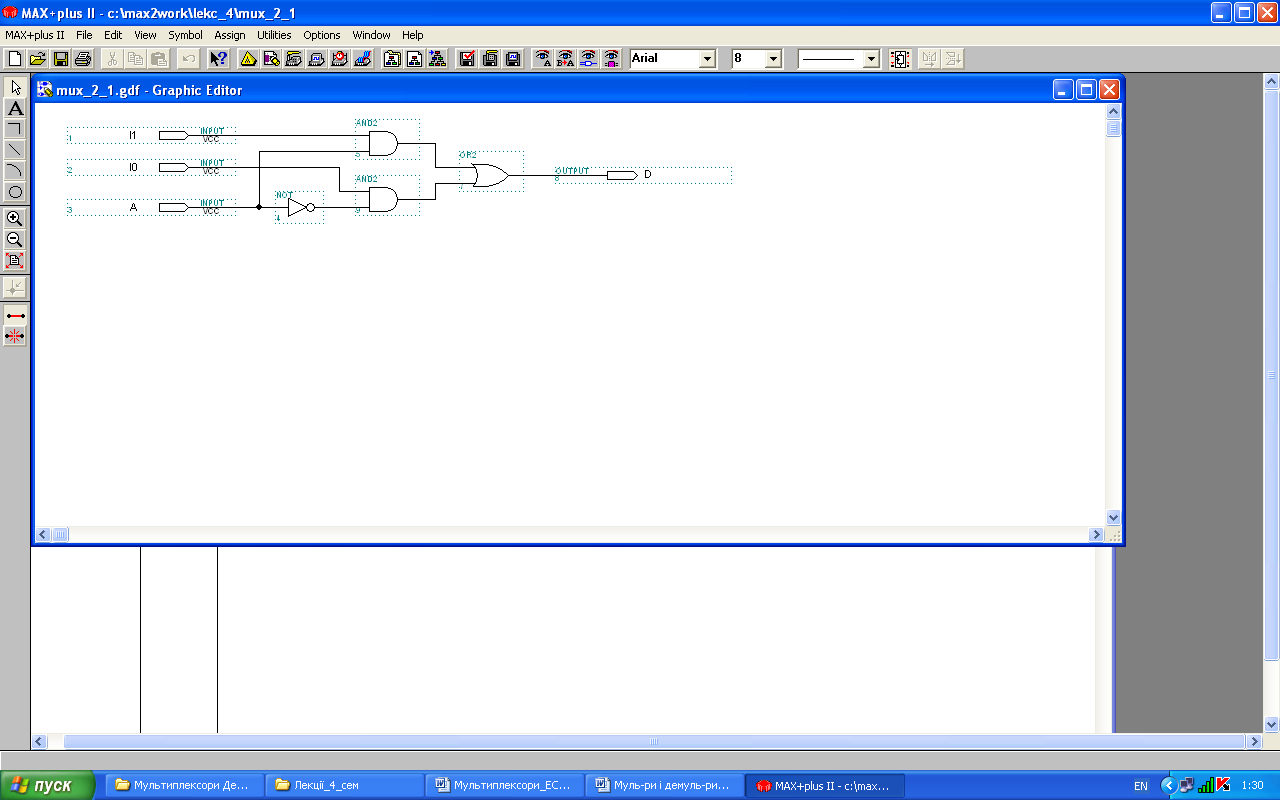

На рис. 3 наведено схему-модель двоканального мультиплексора, реалізованого в пакеті MAX+plus II.

Рис. 2. Мультиплексор з двома входами даних

Мультиплексор з чотирма входами даних

Умовне графічне позначення мультиплексорів показане на рис. 3.

а) б)

а) б)

Рис. 3. Умовне позначення мультиплексорів:

а) на функціональних схемах; б) – на принципових схемах

Логіка

роботи чотиривходового мультиплексора

наведена в табл. 2, де

![]() – адресний код;

– адресний код;

![]() – виходи внутрішнього дешифратора;

– виходи внутрішнього дешифратора;

![]() – вхідна інформація;

– вхідна інформація;

![]() – загальний інформаційний вихід.

– загальний інформаційний вихід.

Таблиця 2

А0

А1

F0

F1

F2

F3

D

0

0

1

0

0

0

F0I0

0

1

0

1

0

0

F1I1

1

0

0

0

1

0

F2I2

1

1

0

0

0

1

F3I3

На основі

табл. 2 вираз для вихідної функції

можна подати з використанням виходів

![]() внутрішнього дешифратора у вигляді

внутрішнього дешифратора у вигляді

![]() ,

(2)

,

(2)

або з мінтермами адресного коду

![]() .

(3)

.

(3)

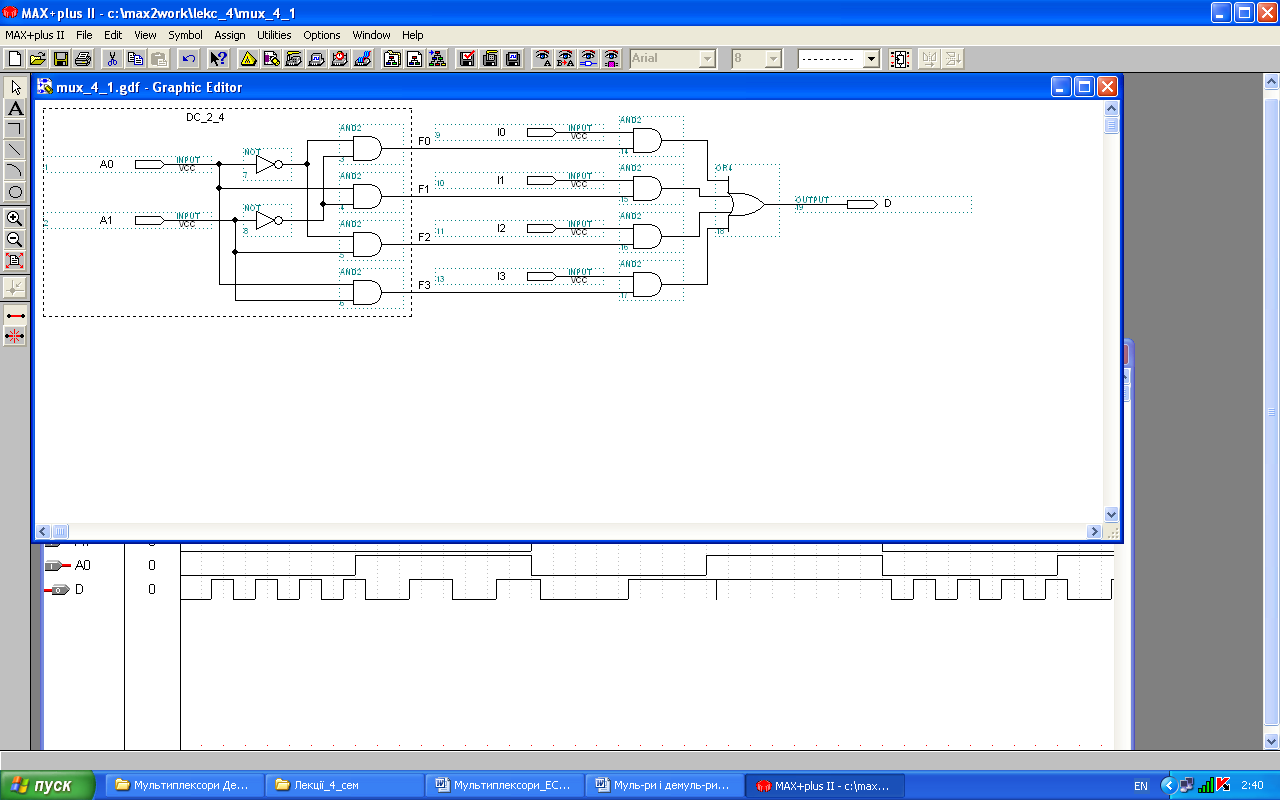

Схеми мультиплексорів, які відповідають рівнянням (2), (3) показані на рис. 4, 5.

Рис. 5

Рис. 6

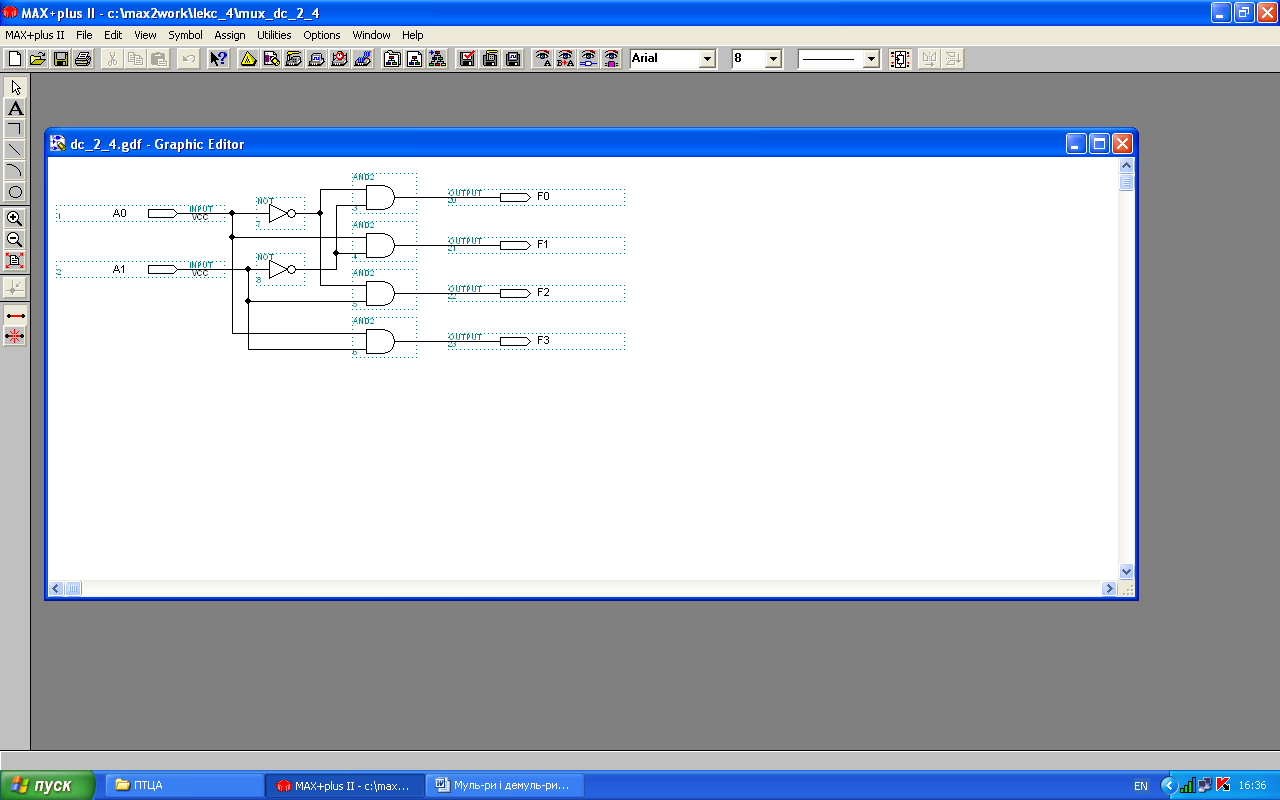

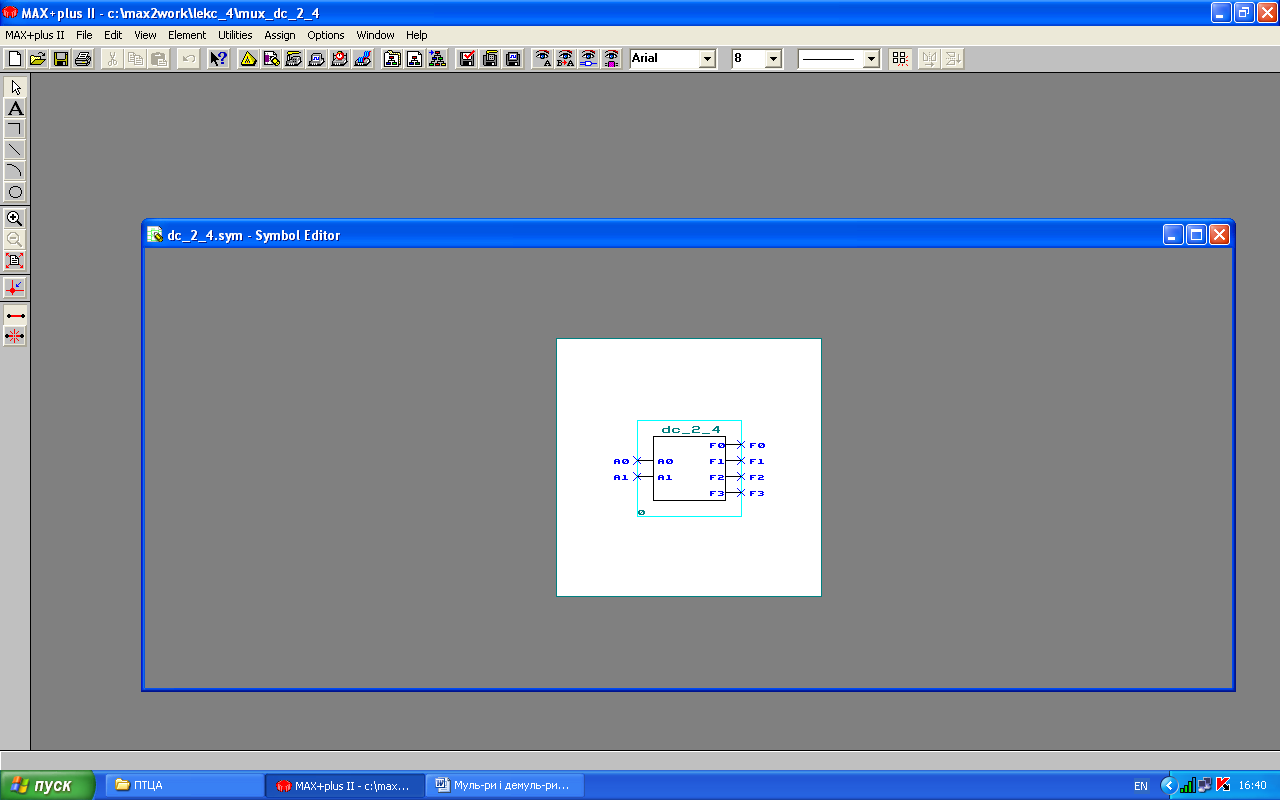

На рис. 7 наведено схему і символ внутрішнього дешифратора

Рис. 7

Побудова мультиплексорів з використання мови ahdl

Нижче

наведено текстовий файл mux_4_1_t, який

реалізовує мультиплексор

![]() з використанням внутрішнього дешифратора.

Результат моделювання даного дешифратора

наведено на рис. 8.

з використанням внутрішнього дешифратора.

Результат моделювання даного дешифратора

наведено на рис. 8.

SUBDESIGN mux_4_1_t

(

A[1..0], I[3..0]: INPUT ;

D: OUTPUT;

)

VARIABLE

F[3..0]:NODE;

BEGIN

TABLE

A[]=>F[];

B"00"=>B"0001";

B"01"=>B"0010";

B"10"=>B"0100";

B"11"=>B"1000";

END TABLE;

D=F0&I0#F1&I1#F2&I2#F3&I3;

END;

Рис. 8

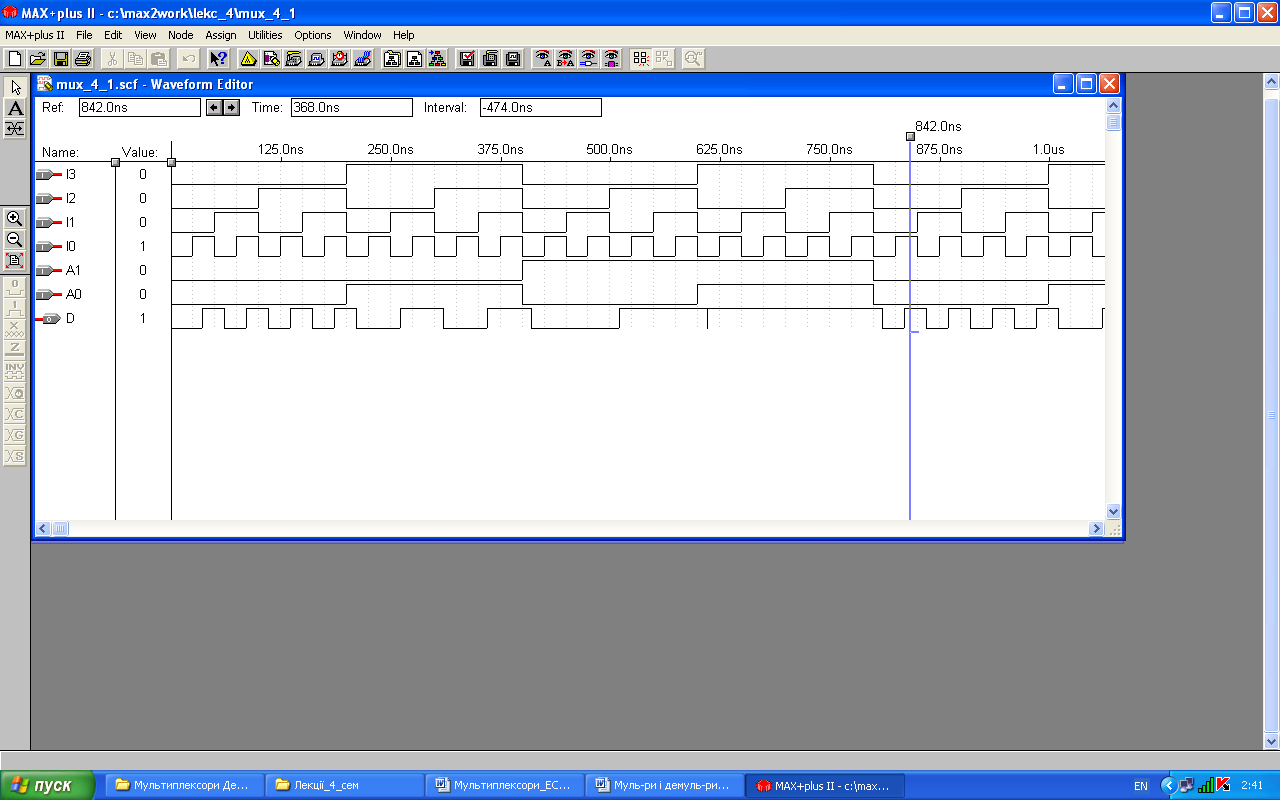

Нижче наведений текстовий файл mux_4_1_tm, який реалізовує мультиплексор з використанням адресних мінтермів. Результат моделювання даного мультиплексора наведено на рис. 9.

SUBDESIGN mux_4_1_tm

(

A[1..0], I[3..0]: INPUT ;

D: OUTPUT;

)

BEGIN

D=!A1&!A0&I0#!A1&A0&I1#A1&!A0&I2#A1&A0&I3;

END;

Рис. 9

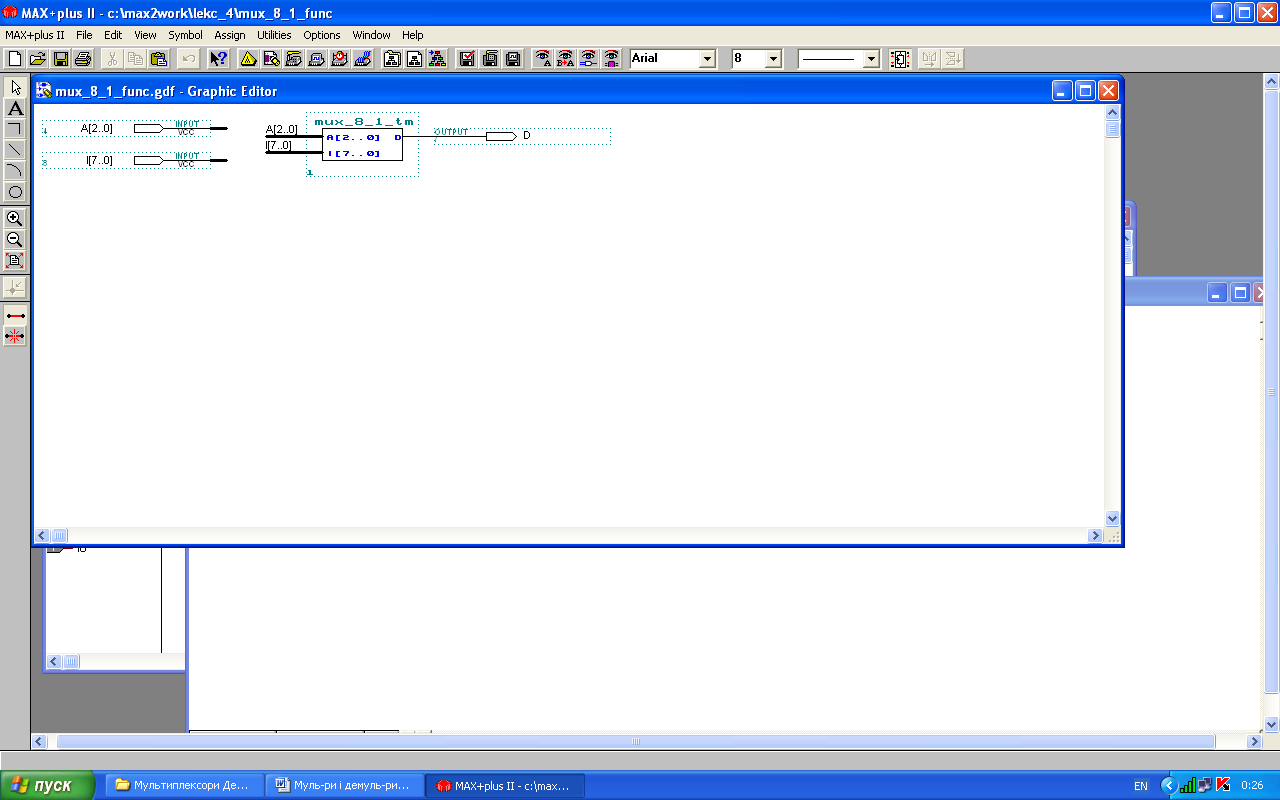

Текстовий

файл mux_8_1_tm реалізовує мультиплексор

![]() у шинному виконанні. Реалізація даного

мультиплексора з використанням символу

та результат його моделювання наведено

на рис. 10.

у шинному виконанні. Реалізація даного

мультиплексора з використанням символу

та результат його моделювання наведено

на рис. 10.

SUBDESIGN mux_8_1_tm

(

A[2..0], I[7..0]: INPUT ;

D: OUTPUT;

)

BEGIN

D=!A2&!A1&!A0&I0#!A2&!A1&A0&I1#!A2&A1&!A0&I2#!A2&A1&A0&I3#

A2&!A1&!A0&I4#A2&!A1&A0&I5#A2&A1&!A0&I6#A2&A1&A0&I7;

END;

Рис. 10

Текстовий файл mux_8_1 реалізовує мультиплексор у провідниковому виконанні. Реалізація даного мультиплексора з використанням символу та результат його моделювання наведено на рис. 11.

SUBDESIGN mux_8_1

(

A2,A1,A0, I7,I6,I5,I4,I3,I2,I1,I0: INPUT ;

D: OUTPUT;

)

BEGIN

D=!A2&!A1&!A0&I0#!A2&!A1&A0&I1#!A2&A1&!A0&I2#!A2&A1&A0&I3#

A2&!A1&!A0&I4#A2&!A1&A0&I5#A2&A1&!A0&I6#A2&A1&A0&I7;

END;

Рис. 11

Текстовий файл mux_8_1_en реалізовує мультиплексор з входом дозволу роботи En. Результат моделювання даного мультиплексора наведено на рис. 12.

При

![]() на виході мультиплексора буде формуватися

сигнал логічного нуля незалежно від

стану інших виходів.

на виході мультиплексора буде формуватися

сигнал логічного нуля незалежно від

стану інших виходів.

Якщо

![]() ,

то сигнал на виході мультиплексора

адресним кодом Adr[] і рівнем сигналу на

відповідному інформаційному вході.

,

то сигнал на виході мультиплексора

адресним кодом Adr[] і рівнем сигналу на

відповідному інформаційному вході.

SUBDESIGN mux_8_1_en

(

Inf[7..0], Adr[2..0], En: INPUT;

D: OUTPUT;

)

BEGIN

IF En THEN

CASE Adr[] IS

WHEN 0 => D=Inf[0];

WHEN 1 => D=Inf[1];

WHEN 2 => D=Inf[2];

WHEN 3 => D=Inf[3];

WHEN 4 => D=Inf[4];

WHEN 5 => D=Inf[5];

WHEN 6 => D=Inf[6];

WHEN 7 => D=Inf[7];

END CASE;

END IF;

END;

Рис. 12

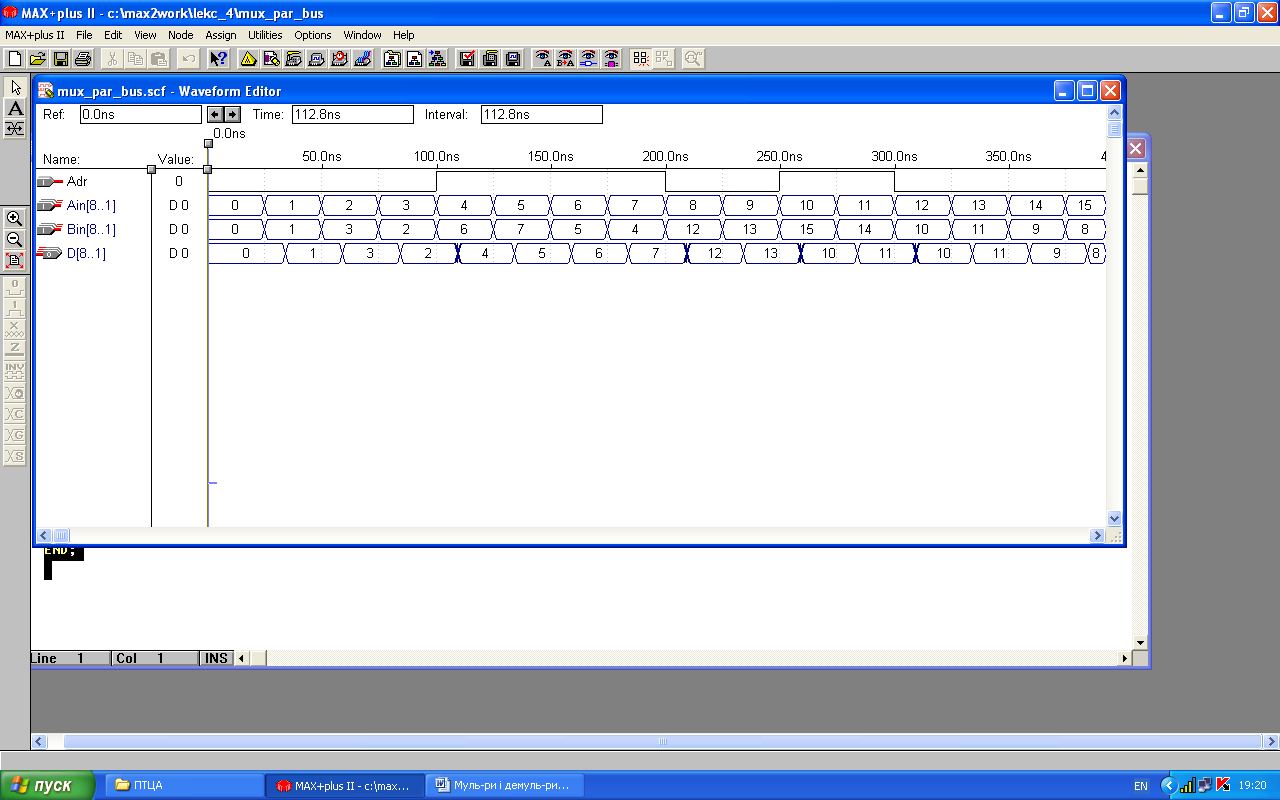

Нижче наведений файл є прикладом параметризованого опису шинного мультиплексора з одноадресним входом, до інформаційних входів якого підключені дві N-розрядні шини Ain[N..1] і Bin[N..1]. Результат моделювання даного мультиплексора наведено на рис. 13.

PARAMETERS (N=8);

ASSERT (N != 1)

REPORT "Value of parameter N = %" N

SEVERITY INFO;

ASSERT (N > 0)

REPORT "Value of parameter N must be greate then %" N

SEVERITY ERROR;

SUBDESIGN mux_par_bus

(

Ain[N..1], Bin[N..1], Adr: INPUT;

D[N..1]: OUTPUT;

)

BEGIN

IF Adr

THEN D[]=Ain[];

ELSE D[]=Bin[];

END IF;

END;

Рис. 13

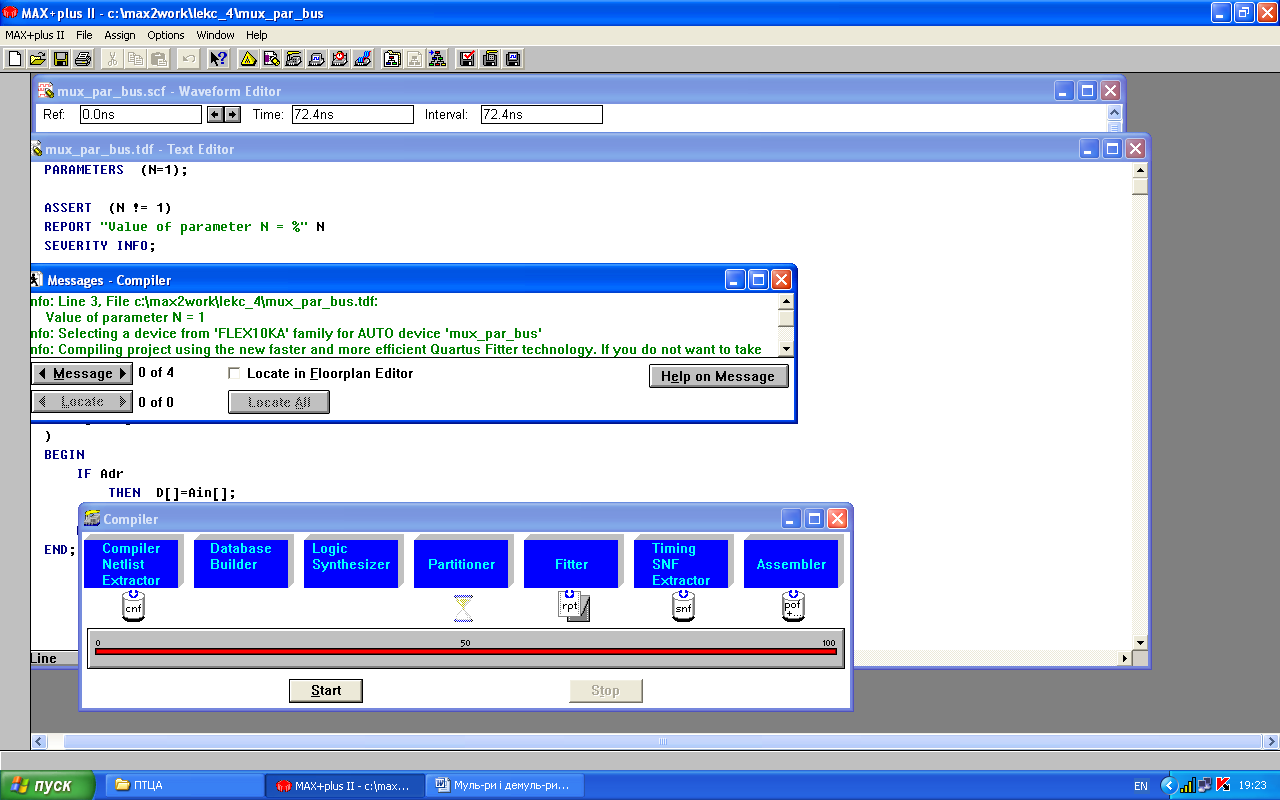

Оператор ASSERT використовується для перевірки параметра N. Так, якщо, наприклад, за допомогою команди Global Project Parameters з меню Assing параметру N присвоїти значення одиниці, то при компіляції модуля буде сформоване наступне повідомлення (рис. 14). “Рівень строгості” даного повідомлення INFO.

Рис. 14

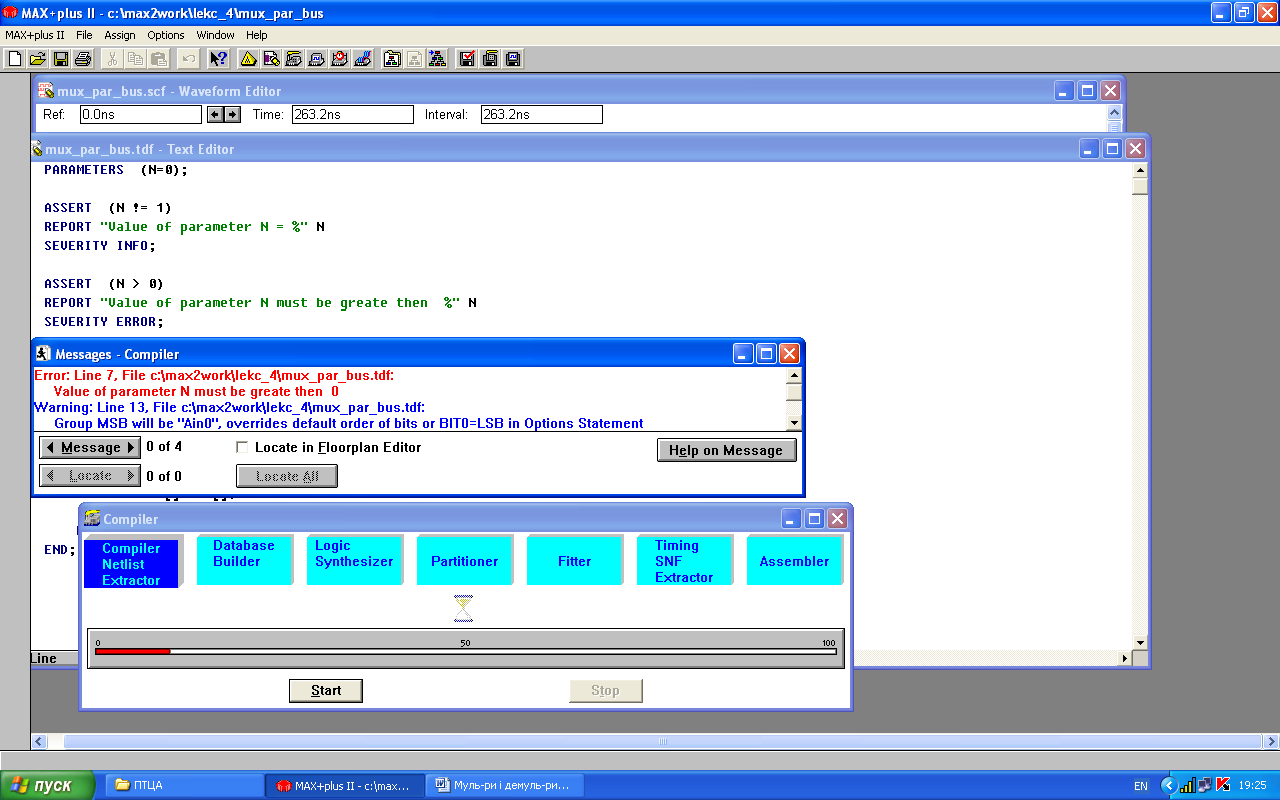

Якщо ж параметру N присвоїти нульове значення, то при компіляції модуля буде сформоване повідомлення, показане на (рис. 15). “Рівень строгості” даного повідомлення ERROR.

Рис. 15