- •1.Конъюнкция, дизъюнкция және терістеу функцияларын іске асыратын логикалық элементтер (лэ). Ақиқат кестелері, жазылу түрлері.

- •26. Микропроцессор, микропроцессорлық жинақ, микро-эем деген электрондық құрылғылардың анықтамаларын беріңіз. Қысқаша мп-дің даму тарихын айтып беріңіз.

- •2. Шеффер штрихі, Пирс жебесі функцияларын іске асыратын логикалық элементтер (лэ). Ақиқат кестелері, жазылу түрлері.

- •3. Аналогты-цифрлық түрлендіргіштер. Ацт – сұлбасының мысалын келтіріп, оның қалай жұмыс істейтінін уақыт диаграммаларымен түсіндіріңіз.

- •4. Және, немесе, емес логикалық элементтердің схемалық жиналуы және олардың негізгі параметрлері.

- •29. Программалық логика негізіндегі мп-ні басқаратын құрылғының қарапайым құрылымы. Оның жақсы жақтары және кемшіліктері.

- •5. Модулі 2 бойынша қосындылауыш және жартылай қосындылауыш. Шартты графикалық белгіленуі, ақиқат кестесі, кез-келген базистегі схемасы.

- •32) 8Разрядты біркристалды мп-нің құрылысы. Негізгі түйіндерінің атқаратын қызметі.

- •33) Біркристалды мп –нің командасының циклі. Машиналық циклдер мен тактілердің атқаратын қызметтері.

- •34) Біркристалды мп құрамына кіретін негізгі регистрлердің атқаратын қызметтері.

- •11.Екідеңгейлі сигналдарды кодтау. Екілік-ондық кодтау. 8421-деген код.

- •36. Біркристалды 8-разрядты мп-нің командалар жүйесі.Басқаруды беру командалар тобы,бағыныңқы программаларымен (подпрограмма) жұмыс істеу.

- •12. Комбинациялық құрылғының синтездеу мәселесін қою. Оны синтездегенде негізгі кезеңдері. Цифрлық құрылғы күрделігінің критериі.

- •41 Біркристалды 8-разрядты мп-де пайдаланатын командалар мен деректердің форматы.

- •42. Параллель шеткері адаптердің құрылымдық схемасы, жұмыс істеу режимдері, басқарушы сөзінің форматы.

- •44. К589 ир 12 деп белгіленетін көпрежімді буферлік регистрдің атқаратын қызметі. Бұл схеманың шартты белгіленуі, жұмыс істеу режімдері.

- •48. Жадтайтын құрылғылардың (жқ) жіктелуі мен параметрлері. Тұрақты және оперативті жқ-лар.

- •49. Тұрақты жадтайтын құрылғының (тжқ) құрылымы, жиналу қағидасы және жұмыс істеу.

- •50. Статикалық оперативті жадтайтын құрылғылардың (ожқ) жиналу қағидасы. Ерікті және тізбекті қатынау (доступ).

48. Жадтайтын құрылғылардың (жқ) жіктелуі мен параметрлері. Тұрақты және оперативті жқ-лар.

В современных ЭВМ (в том числе персональных) матричные ОЗУ большой емкости используются для хранения больших массивов числовых данных или программ. Следует иметь в виду, что часть служебных и вспомогательных программ (инициализации, ввода вывода, типовых операции) имеют неизменный “текст” и должны записываться однократно на постоянное хранение, т. е. Требуют для своего хранения постоянных ЗУ (ПЗУ), в которых информация сохраняется даже при отключенном питании (самовосстанавливается при его включении). Большая же часть текущих программ и данных, как правило, непрерывно обновляется и требует для своего хранения оперативных ЗУ (ОЗУ), предусматривающих возможность многократной записи информации: при отключении питания все содержимое ОЗУ стирается, пропадает.

Рисунок 5.1

Основными параметрами ЗУ являются: емкость (число ячеек памяти), разрядность и время обращения.

24.Терістейтін (инверсный) кірістері болатын RS-триггер. Шартты графикалық белгіленуі. Толық және қысқартылған ауыстырып қосу кестесі. ЖӘНЕ-ЕМЕС логикалық элементтерінен жиналған RS-триггердің жұмысын талдаңыз.

Триггердің бұл түрі логикалық ЖӘНЕ-ЕМЕС элементінен құрылған. Бұл жағдайда «0» дәрежесі активті сигнал ал «1» дәрежесі пассивті сигнал болады. Ақпаратты кірістер R, S белгіленеді. Кіріс S=1, R=1 сигналдары активті болады. Бұл жағдайда триггердің кестесі тура кірісті триггердің кестесіндей жұмыс істейді.

![]()

ЖӘНЕ-ЕМЕС логикалық элементімен құрылған RS триггері кезінде S= R=0-рұқсат етілмеген комбинация. S= R=1- нейтралды болады.

49. Тұрақты жадтайтын құрылғының (тжқ) құрылымы, жиналу қағидасы және жұмыс істеу.

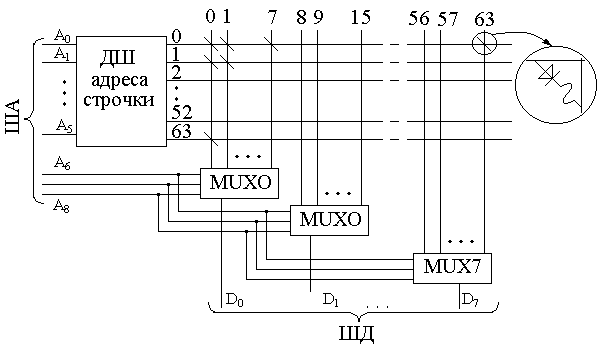

Рисунок 5.2 5.3 На рис. 5.2 изображена структура типового 8 – разрядного ПЗУ емкостью 29=512 байт =4096 бит, которая хорошо иллюстрирует принципы построения и функционирования ПЗУ.

В узлах матрицы 64 х 64 размещается полупроводниковый прибор (диод, транзистор) с плавкой вставкой(PROM) или без нее(ROM); в каждом угле контакт между адресной и разрядной шинами может быть нарушен посредством разрушения полупроводникового прибора и вставки. У ПЗУ типа PROM в узлах матрицы наносится слой нитрида кремния, который хорошо хранит электрический заряд. Время обращения зависит от технологии изготовления БИС ЗУ и для биполярных ПЗУ составляет 20….50 нс, для биполярных-200….600 нс.

50. Статикалық оперативті жадтайтын құрылғылардың (ожқ) жиналу қағидасы. Ерікті және тізбекті қатынау (доступ).

Рисунок 5.3

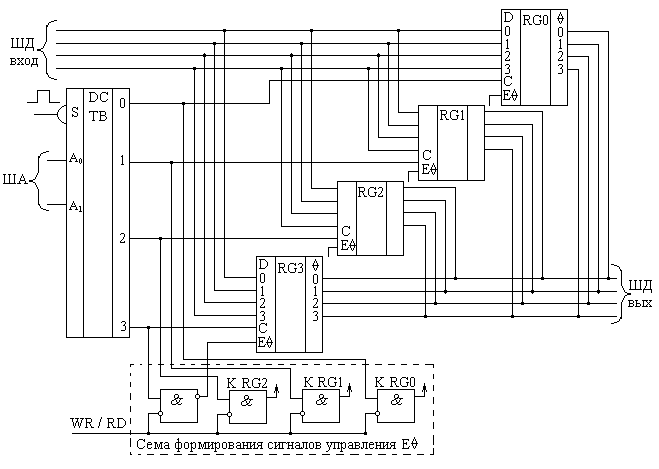

Главная задача при построении матричного ОЗУ заключается во вводе/выводе информации в любую ячейку по одной шине данных. Эта задача в принципе просто решается с помощью мультиплексирования - подключение входов всех регистров к входной шине через демультиплексоры, а выходов - к выходной через мультиплексоры, на входы которых поступает адресная информация о номере нужной ячейки памяти. На рисунке 5.3 в качестве примера показано одно из возможных решений этой задачи для регистров с тристабильными входами.

Рисунок 5.4

Вторая задача-это организация одной двунаправленной шины данных, как это имеет место в реальных МП - системах. Пример решения такой задачи дает рисунок 5.4. При подобном представлении каждый регистр ОЗУ может рассматриваться как ячейка, имеющая двунаправленную информационную шину и два адресных входа Ах и Ау. Тогда в матричном ОЗУ большой емкости проблема адресации к нужной ячейке решается с помощью двух дешифраторов номера строк Ах и столбца Ау (см. рисунок 5.5). В ОЗУ такого типа возможен произвольный порядок (доступ) обращения к регистрам. В ОЗУ же с последовательным доступом – только в порядке возрастания или убывания адресов, как, например, в стеке. Следует обратить внимание на программную реализацию стека в специально выделенной области ОЗУ, когда адреса формируются отдельным реверсивным счетчиком, называемым указателем стека.

Рисунок 5.5