- •1.Сопроцессорная организация распараллеливания обработки информации.

- •(Ниче другого не нашлось)

- •2. Конвейеризация как метод ускорения работы процессора.

- •3. Суперскалярная архитектура процессора.

- •4. Мультипроцессоры (системы с общей памятью).

- •5. Мультикомпьютеры (системы с распределенной памятью).

- •12. Numa-мультипроцессоры

- •13. Мультикомпьютеры mpp и cow (now).

- •14. Топология коммуникационных сетей мультикомпьютеров

1.Сопроцессорная организация распараллеливания обработки информации.

(Ниче другого не нашлось)

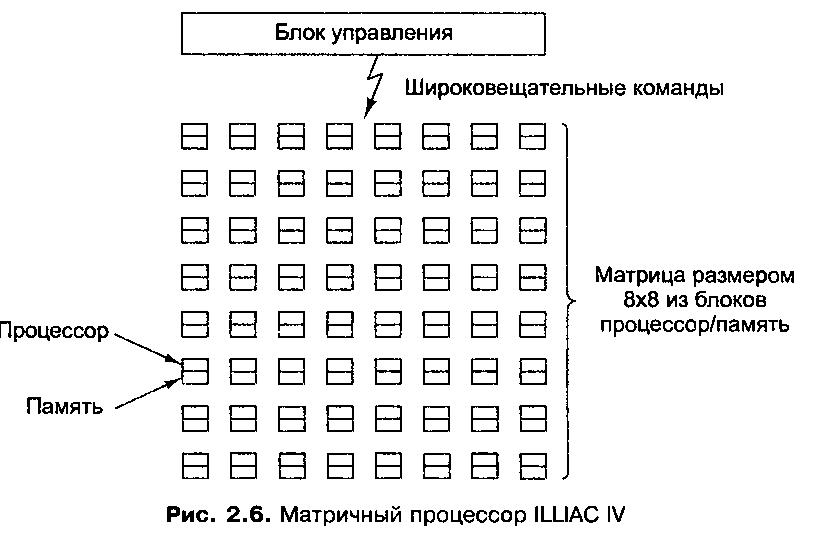

Матричный процессор (array processor) состоит из большого числа сходных процессоров, которые выполняют одну и ту же последовательность команд применительно к разным наборам данных. Первым в мире таким процессором был ILLIAC IV. Схематически он изображен на рис. Первоначально предполагалось сконструировать машину, состоящую из четырех квадрантов, каждый из которых содержал матрицу размером 8 х 8 из блоков процессор/память. Для каждого квадранта имелся один блок контроля. Он рассылал команды, которые выполнялись всеми процессорами одновременно, при этом каждый процессор использовал собственные данные из собственной памяти (загрузка данных происходила при инициализации). Это решение, значительно отличающееся от стандартной фон-неймановской машины, иногда называют архитектурой SIMD (Single Instruction-stream Multiple Data-stream — один поток команд с несколькими потоками данных).

2. Конвейеризация как метод ускорения работы процессора.

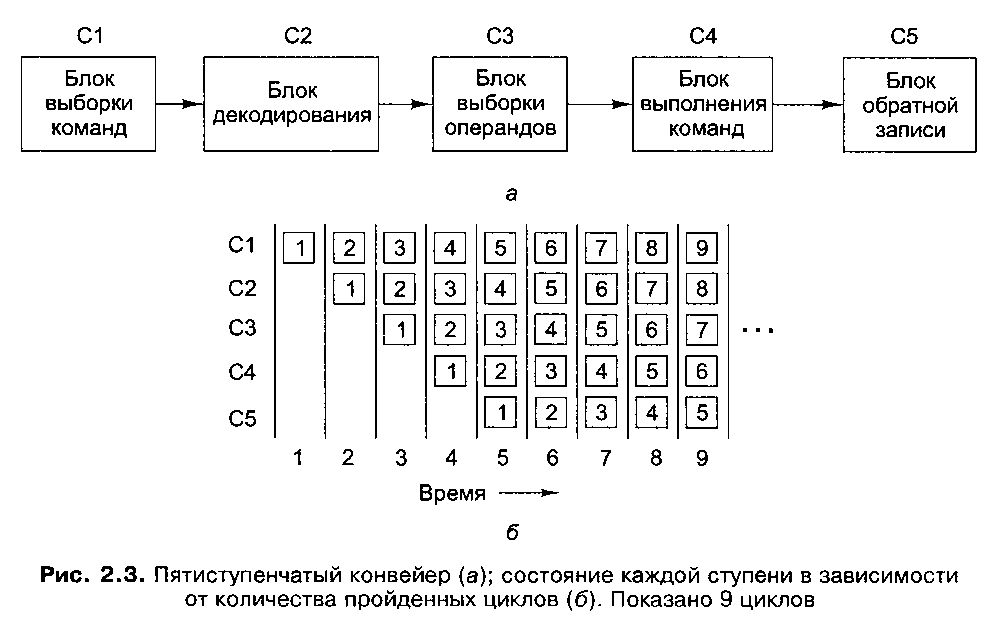

Конвейеры. Можно вызывать команды из памяти заранее и хранить в специальном наборе регистров. В действительности при выборке с упреждением команда обрабатывается за два шага: сначала происходит вызов команды, а затем — ее выполнение. При использовании конвейера команда обрабатывается уже не за два, а за большее количество шагов, каждый из которых реализуется определенным аппаратным компонентом, причем все эти компоненты могут работать параллельно. Каждая команда перед окончательным выполнением проходит несколько ступеней обработки.

Конвейеры позволяют добиться компромисса между временем запаздывания (время выполнения одной команды) и пропускной способностью процессора (количество команд, выполняемых процессором в секунду). Если время обращения составляет Т, а конвейер имеет n ступеней, время запаздывания составит nТ.

3. Суперскалярная архитектура процессора.

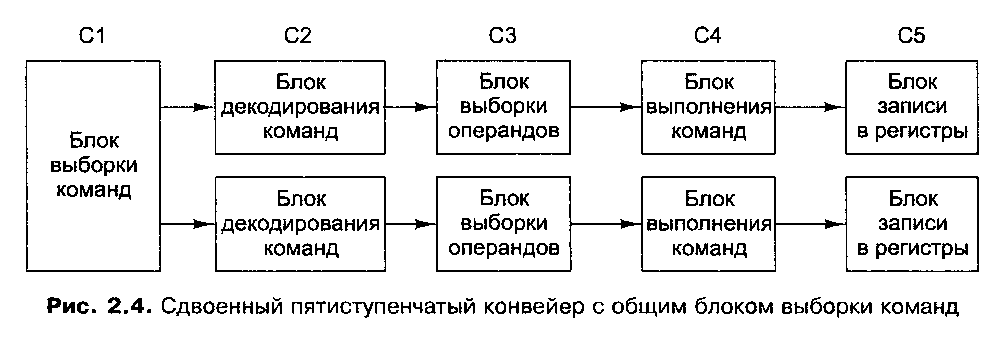

Одна из возможных схем процессора с двумя конвейерами показана на рис. 2.4. Здесь общий блок выборки команд вызывает из памяти сразу по две команды и помещает каждую из них в один из конвейеров. Каждый конвейер содержит АЛУ для параллельных операций. Чтобы выполняться параллельно, две команды не должны конфликтовать из-за ресурсов (например, регистров), и ни одна из них не должна зависеть от результата выполнения другой.

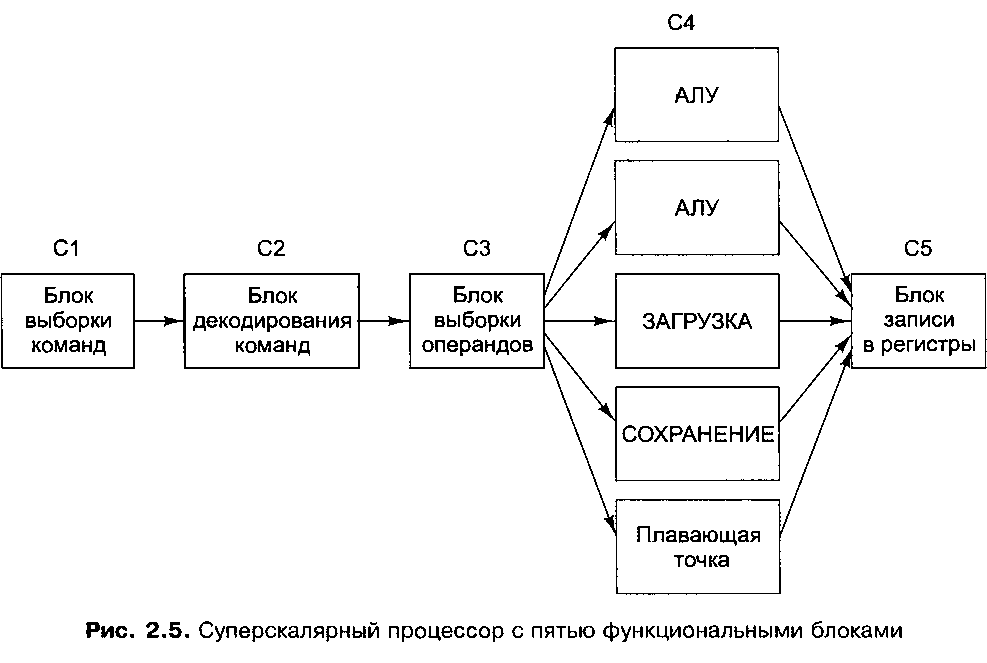

Переход к четырем конвейерам возможен, но требует громоздкого аппаратного обеспечения. Вместо этого используется другой подход. Основная идея — один конвейер с большим количеством функциональных блоков, как показано на рис. 2.5. В 1987 году для обозначения этого подхода был введен термин суперскалярная архитектура.

Теперь же суперскалярными называют процессоры, способные запускать несколько команд (зачастую от четырех до шести) за один тактовый цикл. Естественно, чтобы передавать все эти команды, в суперскалярном процессоре должно быть несколько функциональных блоков. Поскольку в процессорах этого типа, как правило, предусматривается один конвейер, его устройство обычно соответствует рис. 2.5.

На выходе ступени 3 команды появляются значительно быстрее, чем ступень 4 способна их обрабатывать.