- •III Procesor główny

- •Schemat przepływu danych w cpu

- •Najprostszy system połączeń

- •Numery, wartości I adresy kolejnych wyrazów szeregu

- •Instrukcją komplementarną do load jest instrukcja store, której nazwa w mips jest sw (store word). Służy do zapisywania danych w pamięci, a jej format jest taki sam jak instrukcji lw.

- •Potok (strumień) (ang. Flowchart) czynności, które powinna wykonać instrukcja

- •Instrukcja iteracji

- •Inna trudność związana z procedurami w mips jest powodowana przez konieczność umieszczania na stosie zarówno liczb jak I bardziej złożonych struktur danych, na przykład ciągów liczbowych.

- •Operandy mips

- •Instrukcje języka asembler

- •Schemat ilustrujący realizację zbioru instrukcji mips

- •Poprzedni schemat uzupełniony o niektóre linie I urządzenia systemu sterowania

- •1.Nieznana instrukcja lub przepełnienie

- •Składniki komputera zawierające informację o stanie komputera

- •2.Żądanie pobrania informacji z I/o

- •Czasy w pikosekundach (10-9s) trwania każdego z etapów wybranych instrukcji

III Procesor główny

Procesor główny (Central Processor Unit) jest zintegrowanym urządzeniem elektronicznym, które wykonuje instrukcje programu komputerowego, na który składają się operacje arytmetyczne, logiczne, sterowanie urządzeniami wejścia i wyjścia. Nie wszystkie współczesne komputery posiadają tego typu urządzenie, zasługujące na nazwę 'centralny'. Równorzędnych procesorów może być kilka (urządzenia wieloprocesorowe), jednostka centralna może być układem scalonym zawierającym kilka CPU (procesory wielordzeniowe).

CPU jest jednostką zawierającą w jednym chipie kilka elementów funkcjonalnych; jednostkę arytmetyczno - logiczną (Arithmetic Logic Unit), jednostkę sterującą (Control Unit) która pobiera z pamięci instrukcje rozkodowuje je i wykonuje, jeżeli to konieczne z pomocą ALU.

Rozwój technologii obwodów scalonych pozwala na coraz gęstsze upakowanie tranzystorów i budowę coraz bardziej złożonych i niezawodnych procesorów. Z kolei miniaturyzacja i standaryzacja jednostek CPU pozwala na obniżenie ceny komputerów a zatem upowszechnienie we wszystkich dziedzinach aktywności społecznej.Inną konsekwencją gęstego upakowania tranzystorów a co za tym idzie miniaturyzacją mikroprocesorów są krótsze drogi sygnałów a zatem krótsze czasy wykonywania operacji przesyłania (transmisji) informacji (np. pobrania danych z pamięci, przetworzenia i wysłania powrotem do pamięci). Krótsze czasy transmisji pozwalają na wzrost częstotliwości taktowania (rzędu GHz). Są jednak i ujemne strony miniaturyzacji, przede wszystkim trudności z odprowadzaniem ciepła generowanego w tranzystorach, upływności prądów, ujawnianie się kwantowej natury elektronów.

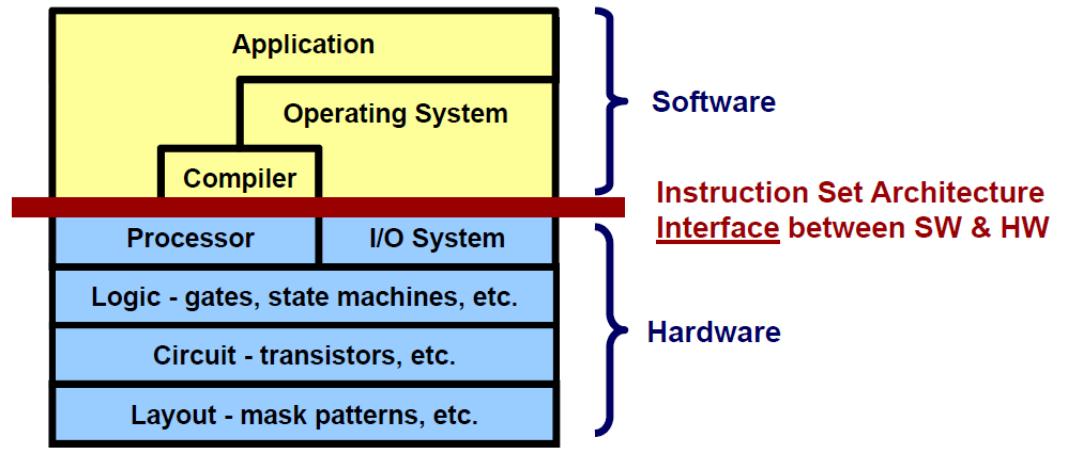

Abstrakcyjne przedstawienie struktury komputera

Organizacja procesora

Składają się na nią dwie grupy problemów:

- Organizacja urządzeń wykonawczych. Rejestry, jednostka arytmetyczno logiczna, komunikacja między nimi, zbiór instrukcji.

- Organizacja urządzeń i procesu sterowania wykonywaniem instrukcji, przepływem informacji.

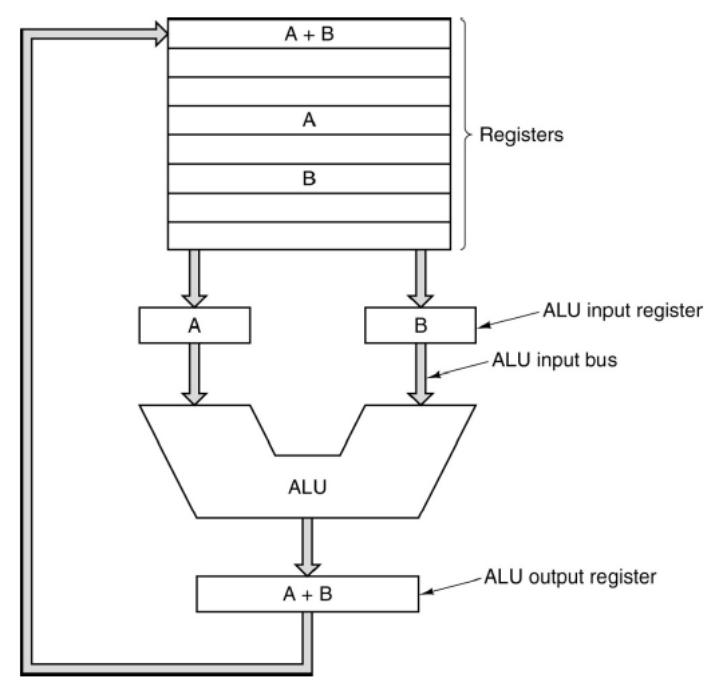

Kluczowym elementem budowy każdego procesora jest jednostka arytmetyczno logiczna.

Trzy główne składniki CPU

Jednostka ta wykonuje rozkazy arytmetyczne, rozkazy logiczne, rozkazy porównań na liczbach całkowitych. Schemat przepływu informacji w ALU pokazuje rysunek.

Termin 'datapath' oznacza zbiór jednostek funkcjonalnych wykonujących przetwarzanie danych, jednostka sterująca (Control Unit) steruje i kontroluje relacje między ‘datapath’ adanymi (pamięciami przechowującymi dane).

Elementami strukturalnymi procesora są 'datapath' oznaczające element funkcjonalny procesora operujących na danych lub przechowujący dane. W zbiorze instrukcji o nazwie (MIPS - Microprocessor without Interlocked PipelineStages) do datapath należą między innymi instrukcje, pamięci, rejestry, ALU.

Schemat przepływu danych w cpu

Operacje wykonywane przez CPU

Głównym zadaniem jest wykonywanie sekwencyjne lub bardziej złożone kolejnych instrukcji zbioru tworzącego program. Zazwyczaj odbywa się to w czterech krokach:pobranie instrukcji z rejestrów, rozkodowanie, wykonanie, wysłanie wyniku do rejestru.

- Pobranie instrukcji (reprezentowanej w pamięci przez jedną lub zbiór liczb) następuje w momencie wyznaczonym przez licznik programu (Program Counter), który przechowuje adres programu w pamięci i numery kolejnych słów programu. Po wykonaniu instrukcji licznik przesuwa bieżącą pozycję o liczbę słów wykonanej instrukcji. Jeżeli wykonanie instrukcji wymaga ściągnięcia informacji z pamięci o długim czasie dostępu, CPU musiałby bezczynnie oczekiwać na dostarczenie jej. Stosuje się więc pewne narzędzia pamięci podręczne (kieszenie, cache) i poszukuje się nowych narzędzi i sposobów organizacji pracy CPU w celu minimalizacji czasu bezczynności procesora. (parallel computing, pipeline architecture)

- Rozkodowanie instrukcji polega na podzieleniu jej na części, które mogą wykonać inne składniki CPU. Sposób interpretacji instrukcji zależy od wbudowanego w danym typie procesora zbioru instrukcji (Instruction Set Architecture). Pewna część liczb w instrukcji (tzw. opcode) informuje jakie operacje należy wykonać. Pozostałe liczby w instrukcji zazwyczaj niosą informację o szczegółach niezbędnych do wykonania instrukcji, na przykład podają rejestr lub adres w pamięci operandów (np. liczb, które należy dodać). W starszych wersjach procesorów część CPU odpowiedzialna za interpretację instrukcji była niezmienną strukturą fizyczną. Współcześnie często instrukcje są interpretowane przez odpowiedni mikroprogram wprowadzony do oddzielnego urządzenia jak pamięć główna lub pamięć flash.

- Wykonanie instrukcji odbywa się w rejestrach albo w podjednostce arytmetyczno-logicznej (ArithmeticLogic Unit).

- Rezultaty wykonania instrukcji zostają przeniesione do rejestru,mogą również zostać wysłane do pamięci cache.

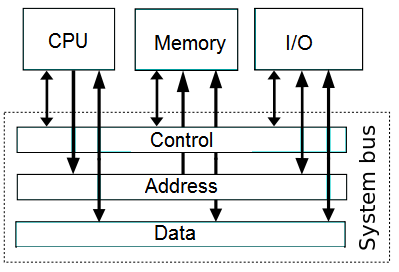

System łączności

Sprawna współpraca wszystkich urządzeń uczestniczących w wykonywaniu programu wymaga bezbłędnej wymiany informacji między nimi.Służą do tego ścieżki przewodzące prąd elektryczny. Gdyby każdą parę elementów łączyła odrębna ścieżka to łącznie zajmowałyby zbyt dużą część fizycznej objętości procesora. Dlatego system połączeń ma strukturę o nazwie magistrala (szyna, bus).