- •II. Pamięci

- •Pojedyncza I sieć jednostek pamięci (o wielu wejściach) zbudowanych na bramkach or

- •Komórka pamięci o pojemności 1 bit, po lewej sram, po prawej dram

- •Porównanie parametrów urządzeń pamięci

- •Struktura logiczna 1-bitowej komórki pamięci

- •Schemat (I symbol) fizycznej jednostki pamięci I jej łączy z zewnętrzem

- •Tablica wartości modułu sterującego pamięci

- •Przykład adresów I zawartości sześciu spośród 210 słów pamięci

- •Dekodowanie I demultipleksowanie adresów na kości dram 64k

- •Schemat logiczny pamięci rom

- •Struktura logiczna pamięci rom 25×8

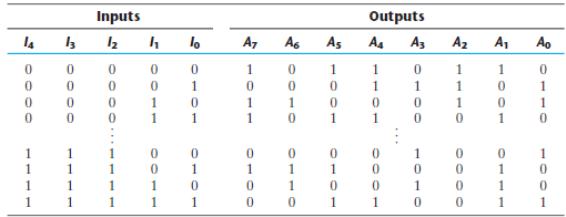

- •Tabela wartości dekodera

- •Komórka pamięci rom – (Metal Oxide Semiconductor)

- •Typowa organizacja pamięci podręcznej

- •Przykład odwzorowania bloków pamięci ram na linie pamięci podręcznej

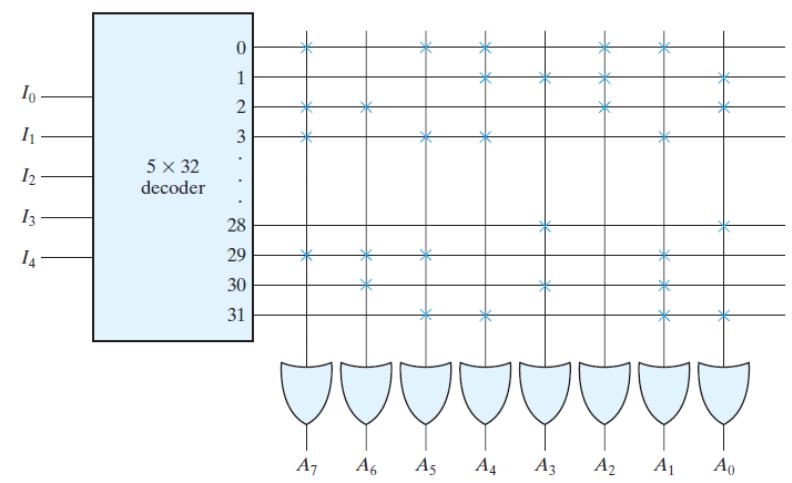

Schemat logiczny pamięci rom

Wejścia zawierają adres a wyjście wyprowadza dane znajdujące się pod wskazanym adresem. Liczba wejść k zależy od liczby słów 2k w pamięci, n oznacza długość słowa w bitach. Liczba słów przechowywanych w pamięci jest określona przez iloraz (2k /długość słowa). Natomiast do identyfikacji adresów 2k bitów trzeba k linii magistrali adresowej. ROM nie posiada wejścia wprowadzającego dane. Zintegrowane kości ROM posiadają jedno lub kilka wejść ‘enable’ pozwalających na selekcję podjednostek dużych sieci ROM

Półprzewodnikowe pamięci ROM są obecnie bardzo rozpowszechnione. Na przykład znajdują się w komputerach do przechowywania programów sterujących rozruchem do chwili przejęcia kontroli przez system operacyjny. Programowalne ROM sterują pracą rozmaitych maszyn i urządzeń; samochodami, pralkami itp. Niektóre rodzaje ROM pozwalają na łatwe usuwanie zawartości i zapisywanie innych informacji (EEPROM - usuwa i zapisuje pojedyncze bity, FLASH - usuwa i zapisuje bloki bitów, czas życia pamięci ROM to setki tysięcy operacji usuwania lub zapisu).

Logiczna struktura ROM

Dla celów dydaktycznych ograniczymy uwagę do miniaturowej kości pamięci o k = 5 i n = 8. Kość zapamiętuje zatem 32 słowa o 8 bitach każde.

Struktura logiczna pamięci rom 25×8

Pięć wejść wprowadza 32 zakodowane adresy każdej z 8 bramek OR z pośrednictwem dekodera 5*32. W ogólności kość musi posiadać dekoder k×2k. Każda bramka OR ma 32 wejścia (na rysunku są one reprezentowane pojedynczą, pionową linią) i każde wyjście z dekodera jest połączone z jednym z wejść każdej bramki. Wobec tego, że każda bramka ma 32 wejścia a bramek jest 8 to nasza kość ma 32*8 = 256 połączeń wewnętrznych. Na rysunku są one reprezentowane przez przecięcia linii poziomych i pionowych. Połączenia te są programowalne (można je traktować jako przełączniki, które mogą być otwate lub zamknięte (jak te oznaczone gwiazdkami). Programowanie polega na ustawieniu przełącznika w pozycji ‘otwarty’ (stan przełącznika ma wartość logiczną ‘0’) lub w pozycji ‘zamknięty’ (stan przełącznika ma wartość logiczną ‘1’). Przed przystąpieniem do programowania trzeba ustalić jaką informację ma zawierać ROM. Dokonuje się tego tworząc odpowiednią tablicę wartości urządzenia. Poniżej znajduje się przykład takiej tabeli dla wyżej omawianej kości ROM. Pokazanych jest kilka początkowych i kilka końcowych wierszy (spośród 32) tabeli wartości. Pięć pierwszych kolumn podaje wartości wszystkich wejść (np. pierwszy wiersz wskazuje, że wszystkie wejścia są otwarte – odpowiada mu wyjście 0 z dekodera). Następne osiem kolumn podaje wartości logiczne wyjść, czyli 8-mio bitowe słowo. Na przykład wiersz 4 mówi, że jeżeli na wejście do dekodera podana jest liczba 000112 to na wyjściu z niego pojawia się liczba 310. Z tabeli wynika, że sygnał równoważny logicznemu ‘1’ dociera tylko do bramek A7, A5, A4, A1. Do pozostałych bramek sygnał nie dociera co odpowiada logicznemu ‘0’. Wobec tego z pamięci wychodzi zbiór bitów 10110010, jest to słowo przechowywane pod adresem 00011.