- •II. Pamięci

- •Pojedyncza I sieć jednostek pamięci (o wielu wejściach) zbudowanych na bramkach or

- •Komórka pamięci o pojemności 1 bit, po lewej sram, po prawej dram

- •Porównanie parametrów urządzeń pamięci

- •Struktura logiczna 1-bitowej komórki pamięci

- •Schemat (I symbol) fizycznej jednostki pamięci I jej łączy z zewnętrzem

- •Tablica wartości modułu sterującego pamięci

- •Przykład adresów I zawartości sześciu spośród 210 słów pamięci

- •Dekodowanie I demultipleksowanie adresów na kości dram 64k

- •Schemat logiczny pamięci rom

- •Struktura logiczna pamięci rom 25×8

- •Tabela wartości dekodera

- •Komórka pamięci rom – (Metal Oxide Semiconductor)

- •Typowa organizacja pamięci podręcznej

- •Przykład odwzorowania bloków pamięci ram na linie pamięci podręcznej

Dekodowanie I demultipleksowanie adresów na kości dram 64k

Detekcja błędów i ich usuwanie

Dynamiczny charakter procesów zapisu i odczytu (zmienne napięcia w mikroobwodach elektrycznych) mogą czasem prowadzić do pomyłek. Konieczne zatem jest wprowadzenie mechanizmu wykrywającego i naprawczego. Najczęściej używany mechanizm polega na generowaniu dodatkowego bitu (bitu parzystości) do każdego słowa danych i przechowywaniu go razem z słowem w pamięci. Jeżeli po odczytywania danych bit parzystości nie jest poprawny to jest to interpretowane jako błąd zapisu lub odczytu. Jednak ta informacja nie wystarcza do korekcji błędu. Aby dokonać korekcji błędu konieczne jest wygenerowanie i dodanie kilku bitów kontrolujących parzystość do słowa danych. Jeżeli po odczytania danych bity kontrolujące parzystość nie są poprawne zostaje uruchomiony program korygujący. W pamięciach RAM najczęściej używane są programy korekcji wykorzystujące kod Hamminga.

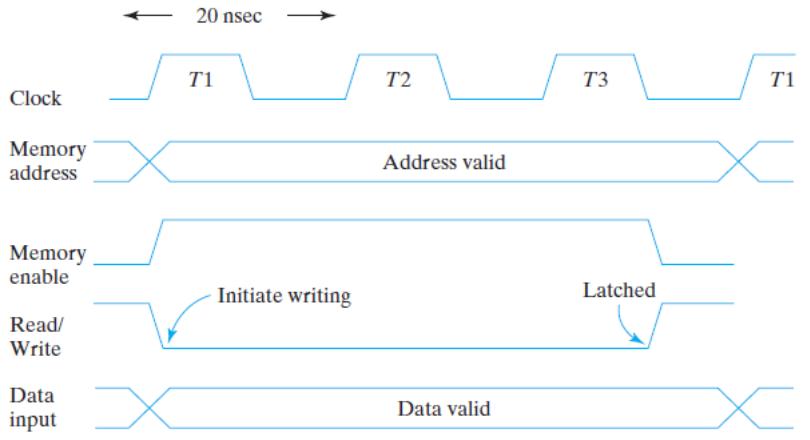

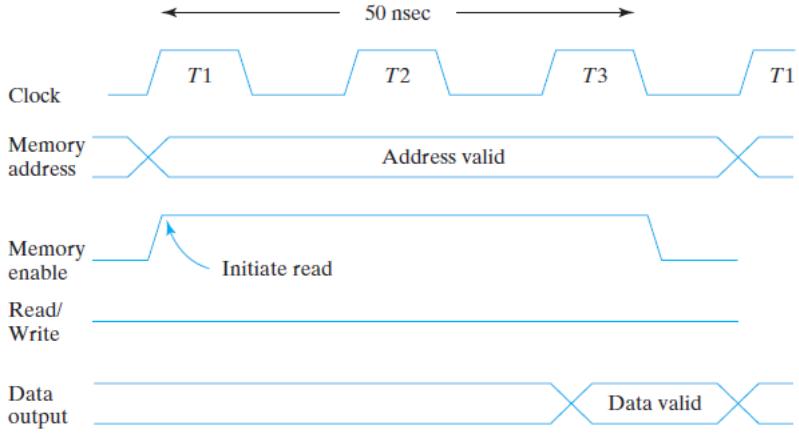

Synchronizacja (timing) operacji zapisu i czytania

Przebieg w czasie operacji wykonywanych w pamięci jest regulowany przez wewnętrzny zegar jej modułu kontrolnego. Czas dostępu jest to czas niezbędny na wybranie komórki a w niej słowa. Czas niezbędny na zapisania jednego słowa w komórce jest na ogół dłuższy niż czas dostępu. Zatem okres jednego cyklu musi być porównywalny z czasem zapisu. Dostępem do jednostki pamięci steruje urządzenie zewnętrzne (np. CPU). Częstotliwości zegarów CPU i pamięci są na ogół różne, częstotliwość zegara CPU jest zazwyczaj kilkakrotnie większa niż częstotliwość zegara pamięci. Sprawna współpraca pamięci z CPU wymaga przeznaczenia kilku pełnych okresów zegara CPU na zapis lub odczyt komórki pamięci.

Przykład

Założymy, że zegar CPU pracuje z częstotliwością 50MHz, czyli okres periodycznego sygnału generowanego przez zegar wynosi 20ns (20*10-9s). Interesuje nas w tej chwili łączność między zegarem i pamięcią, której czas dostępu i okres jednego cyklu nie przekraczają 50ns. To znaczy, że cykl zapisu jednego słowa trwa nie więcej niż 50ns, również czas odczytania jednego słowa nie przekracza 50ns.Te dwa czasy nie zawsze są takie same, wówczas do dalszej analizy trzeba wybrać dłuższy. Ponieważ okres zegara wynosi 20ns to na wykonanie przez pamięć jednej operacji trzeba poświęcić trzy okresy zegara.

Operacja zapisu

Przez okres trzech cykli (T1, T2, T3) zegara pamięć musi być dostępna - mieć zezwolenie (enable), adres komórki musi być dostępny, dane do zapisu muszą znajdować się na wejściu. Podwójne krzyżujące się linie oznaczają możliwe zmiany wartości sygnału linii kilkuścieżkowych. Sygnał aktywujący pamięć i sygnał czytania/zapisu muszą się pojawić dopiero po ustabilizowaniu się sygnału adresu, w przeciwnym razie mogłyby zostać zniszczone dane w innych komórkach pamięci.

Operacja czytania

Podobnie jest podczas operacji czytania, tym razem dane pojawiają się na wyjściu pod koniec trzeciego okresu cyklu zegara. CPU może skierować dane do jednego z rejestrów podczas opadania sygnału w trzecim cyklu zegara.

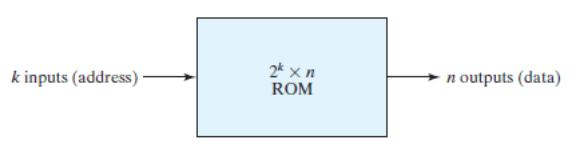

Pamięć ROM

Oprócz RAM niezbędną pamięcią każdego komputera i między innymi programowalnych układów logicznych są nieulotne pamięci ROM przechowujące informację w postaci binarnej. Raz wprowadzona do nich informacja pozostaje niezmieniona i nieusuwalna. W pewnych rodzajach pamięci informację zawartą w niej można usunąć i wprowadzić w jej miejsce inną za pomocą specjalnych zabiegów.