- •II. Pamięci

- •Pojedyncza I sieć jednostek pamięci (o wielu wejściach) zbudowanych na bramkach or

- •Komórka pamięci o pojemności 1 bit, po lewej sram, po prawej dram

- •Porównanie parametrów urządzeń pamięci

- •Struktura logiczna 1-bitowej komórki pamięci

- •Schemat (I symbol) fizycznej jednostki pamięci I jej łączy z zewnętrzem

- •Tablica wartości modułu sterującego pamięci

- •Przykład adresów I zawartości sześciu spośród 210 słów pamięci

- •Dekodowanie I demultipleksowanie adresów na kości dram 64k

- •Schemat logiczny pamięci rom

- •Struktura logiczna pamięci rom 25×8

- •Tabela wartości dekodera

- •Komórka pamięci rom – (Metal Oxide Semiconductor)

- •Typowa organizacja pamięci podręcznej

- •Przykład odwzorowania bloków pamięci ram na linie pamięci podręcznej

Przykład adresów I zawartości sześciu spośród 210 słów pamięci

Kolumny na lewo od symbolu pamięci podają adresy kolejnych słów w postaci binarnej i dziesiętnej, każde słowo ma długość 16 bitów. Słowo pamięci jest w całości zajęte nawet wtedy gdy informacja zajmuje mniej bitów niż długość słowa. Ilość bitów zajęta przez pojedynczy adres zależy od pojemności pamięci.

Multipleksowanie

Jeżeli komórki pamięci tworzą w kości strukturę dwuwymiarową to adres komórki musi być zadany dwoma liczbami; numerem wiersza i numerem komórki. W celu przesłania obydwu liczb jedną i tą samą linią adresową, dokonuje się podziału przedziału czasu przeznaczonego na transfer adresu na dwie części (multipleksowanie w czasie). W pierwszej części przesyłany jest numer wiersza komórki pamięci, a w drugiej numer kolumny.

Również sygnały read i write są przesyłane jedną linią. Wartość sygnału interpretowana jako 1 otwiera ścieżkę od przerzutnika do wyjścia umożliwiając odczytanie bitu. Wartość sygnału interpretowana jako 0 otwiera ścieżkę od wejścia do przerzutnika umożliwiając zapisanie bitu.

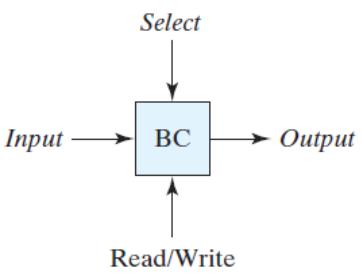

Najmniejszym elementem chipu pamięci jest komórka zdolna zapamiętać jeden bit, prowadzą do niej trzy linie wejścia i jedna linia wyjścia.

Symbol graficzny 1-bitowej komórki pamięci

Zbiór komórek odpowiednio połączonych uzupełniony o dekoder adresów tworzy użyteczną jednostkę pamięci RAM. Poniżej znajduje się schemat logiczny miniaturowej jednostki tego typu mogącej zapamiętać cztery 4-bitowe słowa. Pamięć na cztery słowa wymaga dwóch linii adresowych i dekodera 2*4.

Schemat logiczny jednostki pamięci o pojemności czterech słów cztero-bitowych

Sygnały zawierające zakodowany adres komórki są (na karcie pamięci) dekodowane przed wysłaniem ich do komórek pamięci. Dekoder jest jedną lub wieloma dwuwymiarowymi sieciami. Kwadraty oznaczone BC (binary cell) reprezentują komórki pamięci o pojemności 1 bit. Dwa wejścia spośród trzech przyjmują sygnały z dekodera wybierające jedną czwórkę bitów przechowującą jedno słowo, trzecie wejście przyjmuje wartość jednego bitu tego słowa. Wejście EN (‘enable’) steruje aktywnością pamięci, jeżeli na wejściu jest 0 to ani zapis ani odczyt nie jest możliwy, jeżeli EN = 1 wybrane zostaje jedno z czterech słów pamięci. Wówczas na wejście Read/Write przychodzi sygnał wskazujący, która z tych operacji ma być wykonana. Jeżeli jest to operacja read wtedy cztery bity wybranego słowa są wysyłane przez bramki OR do zewnętrznego terminala. Natomiast na sygnał ‘write’ dane z linii wejścia zostają przesłane do czterech jednobitowych komórek wybranego słowa. Pozostałe komórki pozostają nieczynne i ich zawartość nie ulega zmianie. Jeżeli EN = 0 żadne słowo nie zostaje wybrane, a zawartość wszystkich komórek pozostaje bez zmiany.

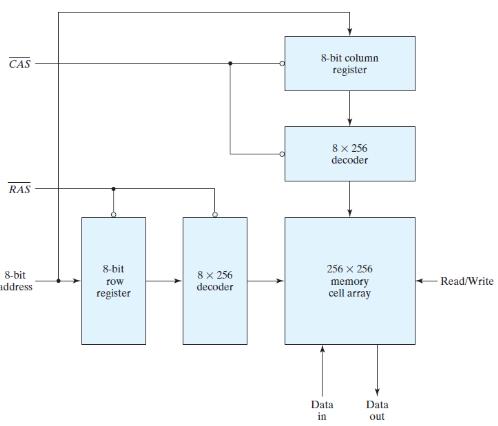

Dostępne na rynku pamięci DRAM mają pojemność setek tysięcy 64 bitowych słów. Poniższy rysunek pokazuje strukturę dekodera adresów na przykładzie pamięci 64k 8- bitowych słów. Linie adresowania są pojedyncze, sygnał przychodzący na RAS (row address strobe) uaktywnia (zmienia swój stan z 1 na 0) 8-mio bitowy rejestr wierszy, podobnie CAS (column address strobe) uaktywnia 8-mio bitowy rejestr kolumn. 16-to bitowy adres jest wprowadzany do pamięci w dwóch etapach, wpierw adres wierszy (idzie do rejestru wierszy) potem adres kolumn (trafia do rejestru kolumn). Kiedy obydwa adresy są już w rejestrach pełny adres jest dekodowany co pozwala na wykonanie operacji ‘read’ lub ‘write’ na właściwej komórce.