- •"Московский государственный университет путей сообщения» (миит)

- •Учебно-методический комплекс по дисциплине

- •Специальность/направление:_230101.65 Вычислительные машины, комплексы, системы и сети (эвм) _________________

- •"Московский государственный университет путей сообщения» (миит)

- •Рабочая учебная программа по дисциплине

- •Специальность/направление:_230101.65 Вычислительные машины, комплексы, системы и сети (эвм) _________________

- •1. Цель изучения дисциплины

- •2. Требования к уровню освоения содержания дисциплины

- •3. Объем дисциплины и виды учебной работы

- •4. Содержание дисциплины

- •4.1. Разделы дисциплины и виды занятий

- •4.2. Содержание разделов дисциплины

- •Раздел 1. Микросхемы типа ттл, эсл, кмоп

- •Раздел 2. Комбинационные устройства

- •Раздел 3. Последовательностные устройства

- •Раздел 4. Запоминающие устройства

- •Раздел 5. Функционально-логическое проектирование узлов и блоков ис и эвм

- •4.3. ЛабораторныЙ практикум

- •4.4. ПрактиЧескиЕ занЯтиЯ

- •5. Самостоятельная работа

- •6. Учебно-методическое обеспечение дисциплины

- •6.1. Рекомендуемая литература

- •Методические указания для студентов

- •1. Общие указания

- •2. Самостоятельная работа

- •2.1. Самостоятельная работа студентов по изучению программных материалов

- •2.2. Контрольная работа

- •2.2.1. Общие указания

- •2.2.2. Задание на контрольную работу Задача 1

- •Методические указания к выполнению контрольной работы.

- •Задача 2

- •Методические указания к выполнению контрольной работы

- •Методические рекомендации для преподавателей

- •1. Методический комментарий по дисциплине «Схемотехника эвм»

- •2. Учебно-методическое обеспечение дисциплины

- •2.1. Рекомендуемая литература

- •3. Методика преподавания учебной дисциплины

- •3.1. Методы обучения

- •3.2. Средства обучения

- •3.3. Методика проведения лабораторных занятий

- •3.4. Методика выполнения контрольной работы

- •3.5. Методика проведения промежуточной аттестации по дисциплине

- •3.5.2. Методика проведения зачета

- •3.5.3. Методика проведения экзамена

3.5.2. Методика проведения зачета

Зачет является этапом проверки качества усвоения студентами программного материала по лабораторным и контрольным работам и имеет целью проверить теоретические знания студентов, выявить их умения применять полученные знания при решении практических задач, а также умения самостоятельно работать с учебной и научной литературой.

К сдаче зачета студенты допускаются при условии выполнения лабораторных и контрольных работ.

Зачет проводится путем ответа обучаемых на теоретические вопросы и пояснений к решению практических задач.

При выдаче учебной группе задания на подготовку к зачету преподавателю необходимо изучить содержание вопросов, по которым будет проводиться проверка уровня знаний обучаемых, уточнить порядок решения типовых задач, критерии оценки ответов обучаемых.

При проведении консультации разъяснить порядок подготовки к зачету, порядок решения типовых задач, выносимых на зачет, уточнить список литературы, подлежащей изучению, ответить на вопросы обучаемых.

Занятие проводится в аудитории, закрепленной за учебным отделением.

После захода в аудиторию (по одному человеку) и доклада преподавателю обучаемые представляют преподавателю, принимающему зачет, свою зачетную книжку, получают от преподавателя задание.

После ознакомления с вопросами обучаемый докладывает, теоретическую часть и порядок решения практических заданий.

Ответ студента по полученным вопросам, если он не уклонился от ответа на заданный вопрос, не должен прерываться: отвечающему должна быть представлена возможность полностью изложить подготовленный ответ. В случае если студент существенно уклонился от поставленного вопроса, преподаватель вправе переключить его внимание на прямой ответ дополнительными вопросами. Если и это не приводит к желаемому результату, то целесообразно прекратить ответ на данный вопрос и предложить перейти к ответу на другие вопросы.

В тех случаях, когда ответ был недостаточно полным, преподаватель, принимающий зачет, имеет право задать уточняющие и дополнительные вопросы.

Критерии оценки ответов на вопросы:

«Зачет» - полный и точный ответ; полный ответ с не существенными неточностями в определениях;

«Незачет» - нет полного ответа на заданные вопросы; существенные неточности в определениях.

Оценка объявляется студента по окончании им ответа. Положительная оценка, «зачет», заносится в экзаменационную ведомость и зачетную книжку; оценка «незачет» проставляется только в экзаменационную ведомость.

Для сдачи зачета студенту разрешается брать один билет. В случае доклада студента, что он не может ответить на вопросы билета, ему выставляется оценка «неудовлетворительно».

3.5.3. Методика проведения экзамена

Общие положения

Экзамен по дисциплине «Схемотехника ЭВМ» проводится в качестве итогового контроля для определения степени достижения учебных целей по учебной дисциплине.

Экзамен по дисциплине имеет целью выявить и оценить теоретические знания и практические навыки студента в общей программе изучения учебной дисциплины «Схемотехника ЭВМ».

Студент допускаются к сдаче экзамена только после выполнения лабораторных работ, сдачи (защиты) им контрольных работ, предусмотренных программой и сдаче зачета по лабораторным и контрольным работам.

Вопросы, выносимы на экзамен, выдаются студентам не менее чем за два месяца до экзамена.

В период подготовки к экзамену проводятся консультации в соответствии с графиком консультаций и расписанием занятий. Во время консультаций преподаватель информирует студента о содержании экзамена и порядке его сдачи, отвечает на вопросы, доводит перечень нормативной и справочной литературы, которой может пользоваться студент при решении задач.

Порядок проведения экзамена

Экзамен принимается преподавателями, ведущими занятия в группе или читающими лекции по данной дисциплине.

Экзамен принимается по билетам в часы и аудитории, предусмотренные расписанием. Каждый билет содержит два теоретических вопроса и один практический вопрос, в котором определено задание и исходные данные для его решения.

После пояснения преподавателя о порядке сдачи экзамена студенты поочередно заходят в аудиторию, представляют преподавателю зачетные книжки, берут билет и докладывают преподавателю его номер. Общее количество студентов в аудитории не должно превышать 5 человек.

Преподаватель уточняет, нет ли неясностей по содержанию вопросов билетов, и дает разрешение на подготовку к ответу с указанием срока подготовки (30 мин.).

В ходе экзамена студенты могут использовать при решении практических задач по соответствующей теме только литературу, определенную в перечне нормативных и справочных материалов, разрешенных к использованию на экзамене.

Для выявления глубины и прочности знаний студента преподаватель, выслушав ответы на вопросы, может задать дополнительные вопросы по темам, предусмотренными учебной программой.

Общая оценка студенту объявляется сразу же после ответа на теоретические вопросы и проверки правильности решения задачи.

Критерии для определения оценок

а) Теоретический вопрос:

«Отлично» - полный и точный ответ;

«Хорошо» - полный ответ с не существенными неточностями в определениях;

«Удовлетворительно» – полный ответ, существенные неточности в определениях;

«Неудовлетворительно» – нет полного ответа на теоретический вопрос.

б) Практическое задание:

«Отлично» - задания выполнено полностью правильно;

«Хорошо» - задания выполнено полностью, оформлено неаккуратно;

«Удовлетворительно» - задания выполнено полностью, но в отчете незначительные ошибки, не влияющие на конечный результат;

«Неудовлетворительно» – задание не выполнено или допущены ошибки, существенно влияющие на результат.

в) общая оценка за экзамен:

Общая оценка за ответ |

Теоретический вопрос |

Теоретический вопрос |

Практическое задание |

«отлично» |

«отлично» |

«отлично» |

«отлично» |

«хорошо» |

«отлично», «хорошо» |

«отлично», «хорошо» |

«хорошо» |

«удовлетворит.» |

«хорошо», «удовлетворит.» |

«хорошо», «удовлетворит.» |

«удовлетворит.» |

«неудовлетвор.» |

«неудовлетвор.» |

«неудовлетвор.» |

«неудовлетвор.» |

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 1 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Основные логические операции, аксиомы и законы булевой алгебры. 2. Динамические микросхемы ОЗУ. Структурная схема и временная диаграмма работы. 3. Разработать схему двоичного суммирующего счетчика с коэффициентом пересчета N = 11 на ИС К555ИЕ7. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 2 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Микросхемы типа ЭСЛ. Электрическая схема, характеристики, основные параметры. 2. Классификация и основные типы регистров. 3 |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 3 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Микросхемы типа КМОП. Электрическая схема, характеристики, основные параметры. 2. Параллельные регистры. Электрическая схема, принцип работы, стандартные ИС.

3

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 4 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия дешифратора. |

||

2. Регистры сдвига. Электрическая схема, принцип работы, стандартные ИС.

3

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 5 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Формы представления логических операций. Способы перехода от одной формы представления к другой. Примеры. 2. Динамические микросхемы ОЗУ. Структурная схема и временная диаграмма работы. 3. Разработать схему вычитающего счетчика с коэффициентом пересчета N = 13 на ИС К555ИЕ7. |

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 6 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. СДНФ и СКНФ логических функций. |

||

2. Статические микросхемы ОЗУ. Структурная схема и временная диаграмма работы. 3. Разработать схему суммирующего счетчика с коэффициентом пересчета N = 7 на ИС К555ИЕ5. |

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 7 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Классификация и основные параметры цифровых микросхем. |

||

2. Микросхемы РППЗУ и ЭСППЗУ. Конструкция ячейки памяти, принцип работы. 3. Разработать 8-ми разрядный преобразователь последовательного кода в параллельный на ИС К555ИР16. |

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 8 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Статические и динамические параметры ЦИС. Передаточная характеристика цифровых микросхем. 2. Микросхемы ПЗУ и ППЗУ. Структурная схема, принцип работы. 3. Разработать схему вычитающего счетчика с коэффициентом пересчета N = 33 на ИС К555ИЕ7.

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 9 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия демультиплексора. 2. Классификация и основные типы счетчиков.

3 |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 10 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Микросхемы типа ТТЛ. Электрическая схема, характеристики, основные параметры. 2. Классификация и основные параметры микросхем памяти. 3. Разработать 8-ми разрядную схему контроля четности на ИС К555ЛП5.

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 11 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Комбинационные сдвигатели и ЛЭ, построенные на мультиплексорах. |

||

2. Принципы построения счетчиков с коэффициентом пересчета отличным от 2 .

3 |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 12 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Схемы построения многоразрядных дешифраторов на демультиплексорах. 2. Двухступенчатый JK триггер. Схема и принцип работы. Счетный режим работы. 3. Разработать схему суммирующего счетчика с коэффициентом пересчета N = 9 на ИС К555ИЕ5. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 13 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия шифраторов. |

||

2. Двухступенчатый RS триггер. Схема и принцип работы. |

||

3 . Минимизировать функцию f = abc + abc + abc + abc и синтезировать схему в базисе ИЛИ-НЕ. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 14 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия схем выделения старшей единицы. 2. D-триггер с динамическим управлением. Схема и принцип работы. 3. Разработать схему вычитающего счетчика с коэффициентом пересчета N = 13 на ИС К555ИЕ7. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 15 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия приоритетного шифратора. 2. Суммирующие и вычитающие счетчики. Схемы, временные диаграммы работы. |

||

3 . Разработать электрическую схему комбинационного устройства, построенного на элементах И-НЕ и реализующего функцию f = abc + abc + abc. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 16 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Электрическая схема и принцип действия логических компараторов. |

||

2. Параллельные счетчики. Схема, временные диаграммы работы. |

||

3

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 17 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Электрическая схема и принцип действия схем контроля четности и нечетности. |

||

2. Реверсивные счетчики. Схема, временные диаграммы работы. 3 . Минимизировать функцию f = abc + abc + abc + abc и синтезировать схему в базисе ИЛИ-НЕ. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 18 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Электрическая схема и принцип действия мультиплексора. |

||

2. RS триггер. Схема, принцип работы, таблица состояний. 3. Разработать схему суммирующего счетчика с коэффициентом пересчета N = 9 на ИС К555ИЕ5. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 19 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

1. Принципы построения многоразрядных сумматоров. Стандартные ИС сумматоров и АЛУ. |

||

2. Классификация и основные типы триггеров. 3. Разработать схему вычитающего счетчика с коэффициентом пересчета N = 33 на ИС К555ИЕ7. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 20 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Схемы построения многоразрядных мультиплексоров на мультиплексорах с меньшей разрядностью. 2. Синхронные одноступенчатые RS- и D-триггеры. Схема, принцип работы, таблица состояний. 3. Разработать схему суммирующего счетчика с коэффициентом пересчета N = 7 на ИС К555ИЕ5.

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 21 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Принципы построения матричных умножителей. Стандартные ИС умножителей. 2. Двухступенчатый JK триггер. Схема и принцип работы. Счетный режим работы. 3. Разработать 8-ми разрядную схему контроля четности на ИС К555ЛП5.

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 22 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Полный одноразрядный сумматор. Схема, таблица истинности, булева функция. 2. Микросхемы ПЗУ и ППЗУ. Структурная схема, принцип работы. |

||

3

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 23 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия мультиплексора. |

||

2. Суммирующие и вычитающие счетчики. Схемы, временные диаграммы работы. |

||

3 . Разработать электрическую схему комбинационного устройства, реализованного в базисе И-НЕ и выполняющего функцию f = abc + abc + abc .

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 24 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Электрическая схема и принцип действия шифраторов. |

||

2. D-триггер с динамическим управлением. Схема и принцип работы. |

||

3. Разработать схему двоичного суммирующего счетчика с коэффициентом пересчета N = 11 на ИС К555ИЕ7. |

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

ЭКЗАМЕНАЦИОННЫЙ |

УТВЕРЖДАЮ: |

РОАТ |

БИЛЕТ № 25 |

Зав. кафедры |

Кафедра ВТ |

по курсу “Схемотехника ЭВМ” |

|

2011/2012 уч.г. |

|

|

|

||

1. Полный одноразрядный сумматор. Схема, таблица истинности, булева функция. 2. Статические микросхемы ОЗУ. Структурная схема и временная диаграмма работы. 3. Разработать 8-ми разрядный преобразователь последовательного кода в параллельный на ИС К555ИР16. |

||

|

||

|

||

|

||

|

||

|

||

|

||

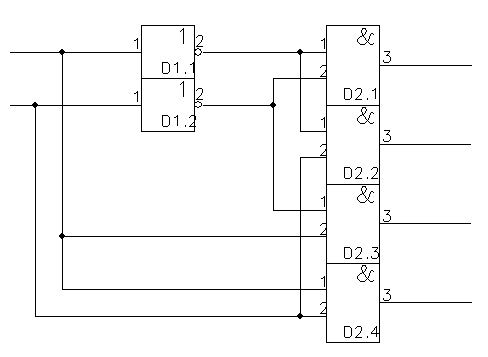

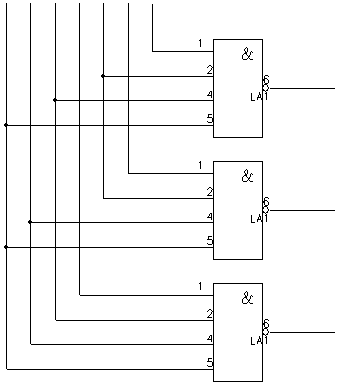

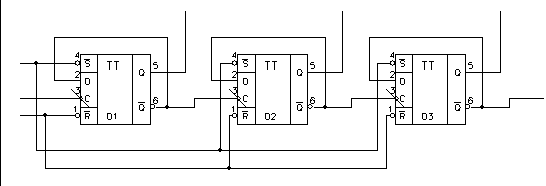

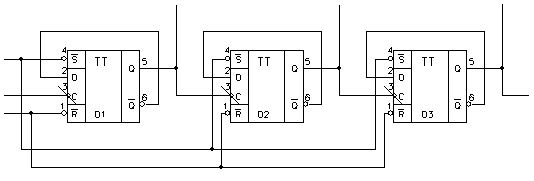

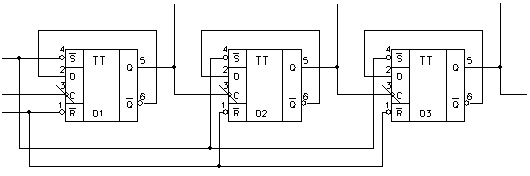

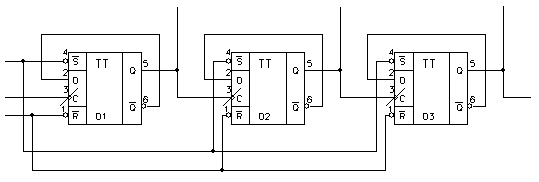

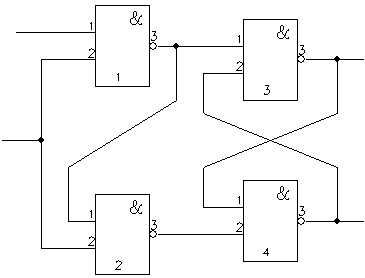

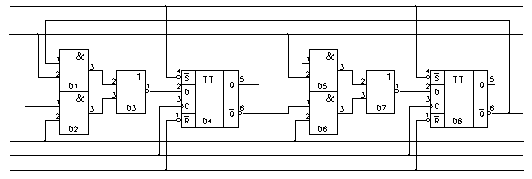

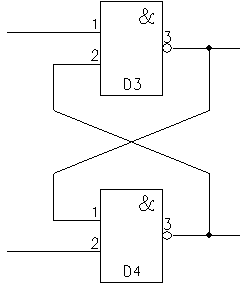

1.Как называется функциональный узел, электрическая схема которого приведена на рисунке? (Введите с клавиатуры)

2 .

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

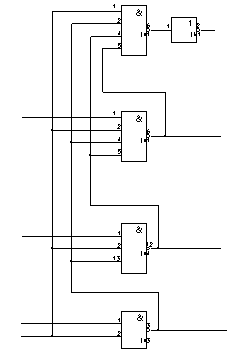

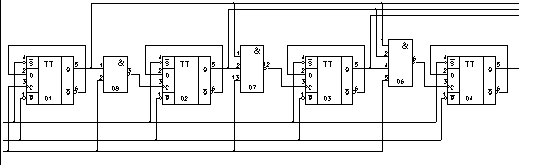

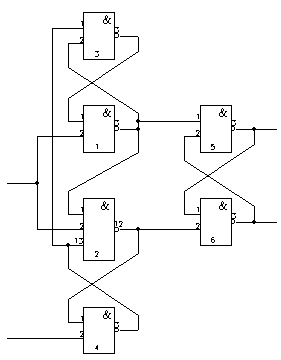

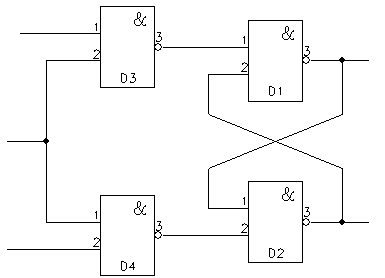

.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

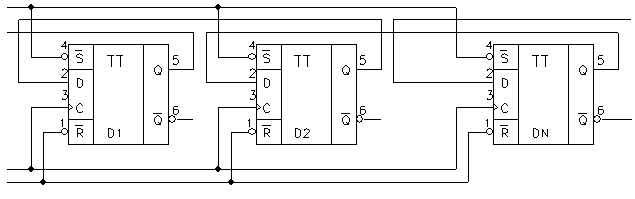

3. Как называется функциональный узел, электрическая схема которого приведена на рисунке? (Введите с клавиатуры)

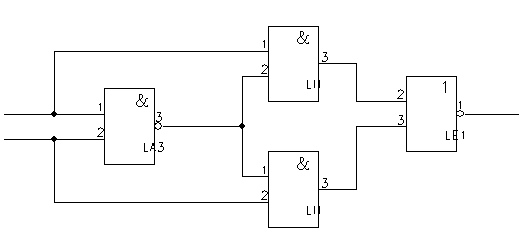

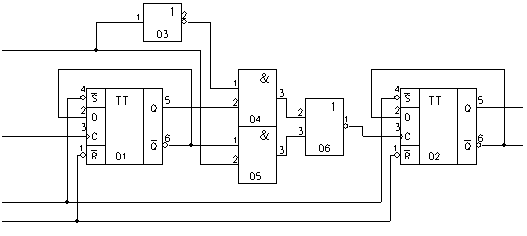

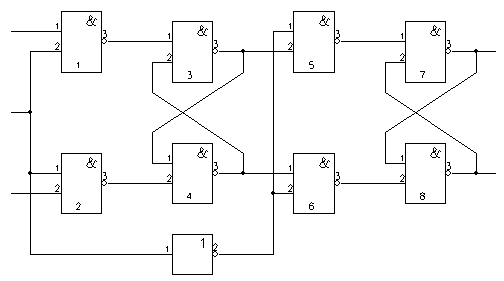

4. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

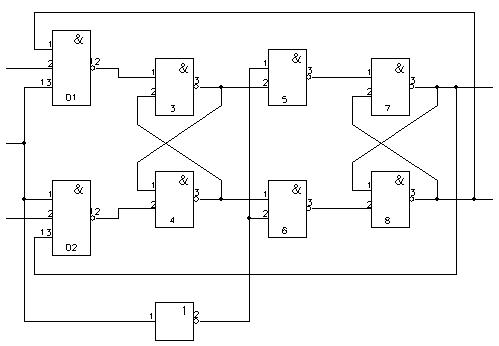

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

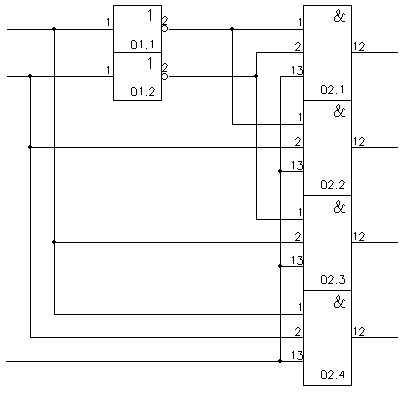

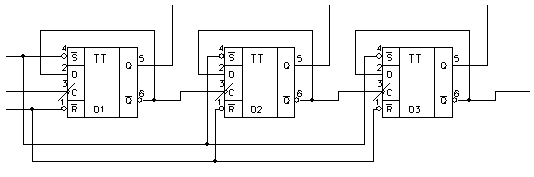

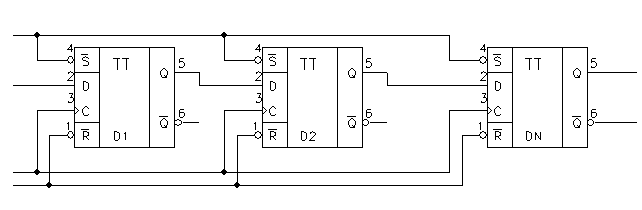

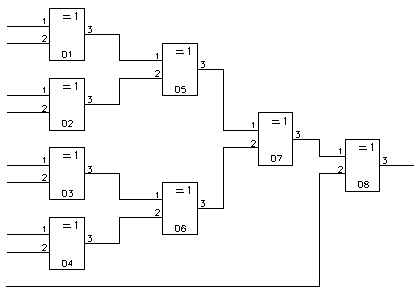

5. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

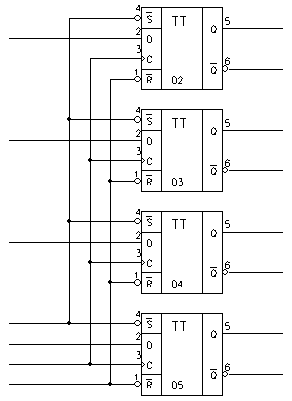

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

6 . Как называется функциональный узел, электрическая схема которого приведена на рисунке? (Введите с клавиатуры)

7. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

8. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

9. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

10. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

11. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

12. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

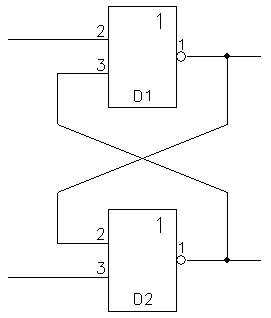

13. Как называется функциональный узел, электрическая схема которого приведена на рисунке? (Введите с клавиатуры)

1 4.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

4.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

1 5.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

5.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

1 6.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

6.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

17. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

18. Как называется функциональный узел, электрическая схема которого приведена на рисунке? (Введите с клавиатуры)

1 9.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

9.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

2 0.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

0.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

2 1.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

1.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

2 2.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

2.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

![]()

23.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

23.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

24. К ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

ак

называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

2 5.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

5.

Как называется функциональный узел,

электрическая схема которого приведена

на рисунке? (Введите с клавиатуры)

.

Минимизировать функцию f

= abc

+ abc

+ bc

и синтезировать схему на элементах

И-НЕ.

.

Минимизировать функцию f

= abc

+ abc

+ bc

и синтезировать схему на элементах

И-НЕ. .

Разработать электрическую схему

комбинационного устройства,

реализованного в базисе И-НЕ и

выполняющего функцию f

= abc + abc

+ abc .

.

Разработать электрическую схему

комбинационного устройства,

реализованного в базисе И-НЕ и

выполняющего функцию f

= abc + abc

+ abc . .

Минимизировать логлогическую функцию

f = abc +

abc + abc и

реализовать ее в базисе ИЛИ-НЕ.

.

Минимизировать логлогическую функцию

f = abc +

abc + abc и

реализовать ее в базисе ИЛИ-НЕ.

.

Разработать электрическую схему

комбинационного устройства, построенного

на элементах И-НЕ и реализующего

функцию f = abc

+ abc + abc.

.

Разработать электрическую схему

комбинационного устройства, построенного

на элементах И-НЕ и реализующего

функцию f = abc

+ abc + abc. .

Минимизировать функцию с помощью

карт Карно f = abcd

+ abcd + abcd

+ abcd + abcd

и синтезировать схему на элементах

ИЛИ-НЕ.

.

Минимизировать функцию с помощью

карт Карно f = abcd

+ abcd + abcd

+ abcd + abcd

и синтезировать схему на элементах

ИЛИ-НЕ. .

Минимизировать функцию с помощью

карт Карно f = abcd

+ abcd + abcd

+ abcd + abcd

и синтезировать схему на элементах

ИЛИ-НЕ.

.

Минимизировать функцию с помощью

карт Карно f = abcd

+ abcd + abcd

+ abcd + abcd

и синтезировать схему на элементах

ИЛИ-НЕ. .

Минимизировать логическую функцию

f = abc + abc

+ abc и реализовать ее в

базисе ИЛИ-НЕ.

.

Минимизировать логическую функцию

f = abc + abc

+ abc и реализовать ее в

базисе ИЛИ-НЕ.