Евтух Дмитрий 3 курс, 6+7

Лабораторная работа 4

Программирование стандартных портов внешних устройств ПЭВМ,

обработкой прерываний в ПЭВМ

Цель работы: познакомиться с программированием стандартных портов персонального компьютера, обработкой прерываний в ПЭВМ.

Прерывания и исключения

Прерывания и исключения нарушают нормальный ход выполнения

программы для обработки внешних событий или сообщения о

возникновении особых условий или ошибок.

Прерывания подразделяются на аппаратные (маскируемые и

немаскируемые), вызываемые электрическими сигналами на выходах

процессора, и программные, вызываемые по команде INT xx.

Программные прерывания процессором обрабатываются как

разновидность исключений.

Аппаратные прерывания подразделяются на маскируемые и

немаскируемые. Процессор может воспринимать прерывания после

выполнения каждой команды, длинные строковые команды имеют для

восприятия прерываний специальные окна.

Маскируемые прерывания вызывает сигнал на входе INTR (Interrupt

Request) при установленном флаге разрешения (IF=1). В этом случае

процессор сохраняет с стеке регистр флагов, сбрасывает флаг IF и

вырабатывает два следующих друг за другом (backtoback) цикла

подтверждения прерывания, в которых генерируются управляющие

сигналы INTA# (InterruptAcknowledge). Высокий уровень сигнала INTR

должен сохраняться по крайней мере до подтверждения прерывания.

Первый цикл подтверждения холостой, по второму импульсу внешний

контроллер прерываний передает по шине номер вектора,

обслуживающего данный тип аппаратного прерывания. Прерывание с

полученным номером вектора выполняется процессором также, как и

программное. Обработка текущего прерывания может быть в свою

очередь прервана немаскируемым прерыванием, а если обработчик

установит флаг IF, то и другим маскируемым аппаратным прерыванием.

Немаскируемые прерывания выполняются не зависимо от состояния

флага IF посигналу NMI (Non Mascable Interrupt). Высокий уровень на

этом входе вызовет прерывание с типом (вектором) 2, которое

выполняется также, как и маскируемое. Его обработка не может

прерваться под действием сигнала на входе NMI до выполнения команды

IRET.

Исключения (Exceptions) подразделяются на отказы, ловушки и

аварийные завершения.

Отказ (fault) – это исключение, которое обнаруживается и

обслуживается до выполнения инструкции, вызывающей ошибку. После

обнаружения этого исключения выполнение возвращается снова на туже

инструкцию (включая все префиксы), которая вызвала отказ. Отказы,

использующиеся в системе виртуальной памяти, позволяют, например,

подкачать с диска в оперативную память затребованную страницу или

сегмент.

Ловушка (trap) – это исключение, которое обнаруживается и

обслуживается после выполнения инструкции, его вызывающей. После

обслуживания этого исключения управление возвращается на

инструкцию, следующей за вызывающей ловушку. К классу ловушек

относятся и программные прерывания.

Аварийное завершение (abort) – это исключение, которое не

позволяет точно установить инструкцию, его вызвавшую. Оно

используется для сообщения о серьезной ошибке, такой как аппаратное

ошибка или повреждение системных таблиц.

Под исключения Intel резервирует векторы 0-31 в таблице

прерываний, однако в РС часть из них перекрывается системными

прерываниями BIOS и DOS.

Трактовка исключений и прерываний в защищенном режиме похожа

на их трактовку в реальном режиме с тем отличием, что вместо таблицы

векторов прерываний, находящейся на фиксированном месте (в начале)

памяти, таблица дескрипторов прерываний IDT может быть расположена

в произвольном месте в памяти, а ее адрес хранится в специально

предназначенном для этого регистре процессора IDTR.

Напомним, что исключения могут быть внутренние, программные и

внешние. Внутренние прерывания или исключения (exceptions) возникают

в процессоре при возникновении в нем конфликтной ситуации (например,

деления на ноль). Внешние прерывания поступают от внешних устройств.

Программные прерывания инициируются самой программой (по команде

int). В защищенном режиме в режиме многозадачности возникает

четвертая разновидность прерываний -- переключение с одной задачи на

другую.

Несмотря на разную природу прерываний, методы их обработки и в

реальном, и в защищенном режимах совпадают – происходит передача

управления на соответствующую процедуру обработки прерывания.

Общий сценарий обработки прерывания таков. В микропроцессоре

возникает исключение, или исполняемая программа генерирует

прерывание, или прерывание поступает от внешней аппаратуры на вход

прерываний микропроцессора INT. Далее все происходит одинаково.

Процессор определяет номер прерывания и дескриптор прерывания,

соответствующий этому номеру. Дескриптор прерывания содержит,

помимо всего прочего, адрес обработчика прерывания. Далее в стеке

сохраняется адрес возврата и управление передается на обработчик,

который должен заканчиваться командой IRET.

По аналогии с реальным режимом все прерывания защищенного

режима занумерованы (от 0 до 255), причем первые 32 номера закреплены

именно за исключениями (в настоящее время используется только

несколько первых номеров). Вся информация о прерываниях собрана в

таблицу IDT, элементы которой называются дескрипторами прерываний,

или шлюзами.

Дескрипторы прерываний, как и дескрипторы сегментов, имеют

длину 8 байт, но структура их различна. Точнее можно сказать, что

шлюзы являются стандартными, зарезервированными системой

дескрипторами сегментов.

Соответственно указанным типам прерываний шлюзы, входящие в

таблицу, могут быть трех типов: шлюзы задач – для переключения задач,

шлюзы прерываний – для аппаратных прерываний и исключений, и

шлюзы ловушек (trap) для программных прерываний. Тип данного шлюза

указывается двумя байтами внутри кода этого шлюза.

+В шлюзах, соответствующих программным прерываниям, указывается

уровень привилегий программы, которая может пользоваться данным

прерыванием.

Описание механизма обработки прерываний в мп i80x86:

Микропроцессор I8086 имеет достаточно универсальную систему прерываний.

Возможные источники прерываний показаны на рис. 2.

Рис.2. Источники прерываний

Главным условием правильной реакции МП на прерывание является возобновление прерванной программы так, как будто прерывания вообще не было.

Реагируя на прерывание, МП должен запомнить адрес возврата в прерванную программу. Этот адрес должен указывать на команду, которая выполнялась бы, если бы прерывания не было.Кроме того, для правильной работы прерванной программы необходимо запомнить регистр флажков.

Адрес возврата в виде регистров IP и CS, а также регистр флажков запоминаются в стеке.

При программировании процедуры обработки прерывания пользователь может запоминать в стеке и другую информацию. Необходимо помнить, что при передаче управления процедуре обработки прерывания МП сбрасывает флажки IF и TF.

Когда обслуживание прерывания завершается, запомненные значения извлекаются из стека и прерванная программа продолжает выполняться из того состояния, в котором она была прервана.

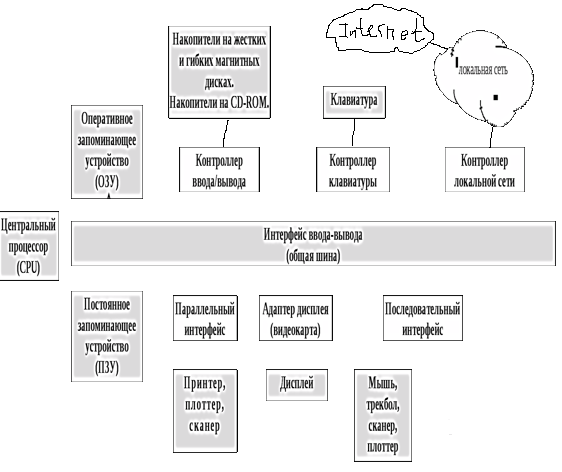

Внешние устройства ПЭВМ

Листинги разработанных программ

Листинг 11

1 ;----------------------------------------------------------------------

2 0000 data segment para public 'data'

3 0000 54 65 73 74 20 6D 65 message db "Test message output....$"

4 73 73 61 67 65 20 6F

5 75 74 70 75 74 2E 2E

6 2E 2E 24

7 0018 data ends

8

9 0000 stk segment stack

10 0000 0100*(3F) db 256 dup ('?')

11 0100 stk ends

12

13 0000 code segment para public 'code'

14 0000 main proc

15 assume cs:code,ds:data,ss:stk

16 0000 B8 0000s movax,data ax

17 0003 8E D8 movds,ax

18

19 0005 BA 0000r movdx,offset message

20 0008 B409 mov ah,09h

21 000A CD 21 int 21h

22

23 000C B8 4C00 mov ax,4c00h

24 000FCD 21 int 21h 21h

25 0011 mainendp

26 0011 codeends

27 endmain

Листинг12

1 ;-------------------------------------------------------------------

2 0000 data segment para public 'data'

3 0000 54 65 73 74 20 6D 65+ message db "Test message output....$"

4 73 73 61 67 65 20 6F+

5 75 74 70 75 74 2E 2E+

6 2E 2E 24

7 0018 data ends

8

9 0000 stk segment stack

10 0000 0100*(3F) db 256 dup ('?')

11 0100 stk ends

12

13 0000 code segment para public 'code'

14 0000 main proc

15 assume cs:code,ds:data,ss:stk

16 0000 B8 0000s movax,data

17 0003 8E D8 movds,ax ;ax ў ds

18

19 0005 B4 08 metka: mov ah,08h

20 0007 CD 21 int 21h

21 0009 B4 02 mov ah,02h

22 000B 8A D0 movdl,al

23 000D CD 21 int 21h

24

25 000F EB F4 jmpmetka

26

27 0011 B8 4C00 mov ax,4c00h

28 0014 CD 21 int 21h

29 0016 mainendp

30 0016 codeends

31 endmain

Листинг14

1 ;-------------------------------------------------------------------------

2 masm

3 0000 model small

4 0000 stack 100h

5 delay macro time

6 local ext,iter

7

8 push cx

9 movcx,time

10 ext:

11 push cx

12 mov cx,5000

13 iter:

14 loopiter

15 popcx

16 loop ext

17 pop cx

18 endm

19 0000 .data

20 0000 0A5B tonelowdw 2651

21 0002 00 cntdb 0

22 0003 ???? tempdw ?

23 0005 .code

24 0000 main:

25 0000 B8 0000s movax,@data

26 0003 8E D8 movds,ax

27 0005 33 C0 xorax,ax

28 0007 go:

29 0007 B0 B6 mov al,0B6h

30 0009 E6 43 out 43h,al

31 000B E4 61 in al,61h

32 000D 0C 03 or al,3

33 000F E6 61 out 61h,al

34 0011 B9 0823 mov cx,2083

35 0014 musicup:

36 0014 A1 0000r movax,tonelow

37 0017 E6 42 out 42h,al

38 0019 86 C4 xchgal,ah

39 001B E6 42 out 42h,al

40 001D 83 06 0000r 01 add tonelow,1

41 delay 1

42 0022 51 push cx

43 0023 B9 0001 mov cx,1

44 0026 ??0000:

45 0026 51 push cx

46 0027 B9 1388 mov cx,5000

47 002A ??0001:

48 002A E2 FE loop ??0001

49 002C 59 pop cx

50 002D E2 F7 loop ??0000

51 002F 59 pop cx

52 0030 8B 16 0000r movdx,tonelow

53 0034 89 16 0003r movtemp,dx

54 0038 E2 DA loop musicup

55 003A B9 0823 mov cx,2083

56 003D musicdown:

57 003D A1 0003r movax,temp

58 0040 E6 42 out 42h,al

59 0042 8A C4 moval,ah

60 0044 E6 42 out 42h,al

61 0046 83 2E 0003r 01 sub temp,1

62 delay 1

63 004B 51 push cx

64 004C B9 0001 mov cx,1

65 004F ??0002:

66 004F 51 push cx

67 0050 B9 1388 mov cx,5000

68 0053 ??0003:

69 0053 E2 FE loop ??0003

70 0055 59 pop cx

71 0056 E2 F7 loop ??0002

72 0058 59 pop cx

73 0059 E2E2 loop musicdown

74 005B nosound:

75 005B E4 61 in al,61h

76 005D 24 FC and al,0FCh

77 005F E6 61 out 61h,al

78 0061 BA 0A5B mov dx,2651

79 0064 89 16 0000r movtonelow,dx

80 0068 FE 06 0002r inccnt

81

82 006C 80 3E 0002r 05 cmp cnt,5 ?

83 0071 75 94 jne go

84 0073 exit:

85 0073 B8 4C00 mov ax,4c00h

86 0076 CD 21 int 21h

87 endmain

Описание динамики развития и архитектурных особенностей шести

новейших моделей микропроцессоров фирмы CYRIX - VIA

CYRIX

1992г. Cyrix Cx486SLC/DLC

Это первый процессор фирмы Cyrix, до его выхода компания занималась выпуском математических сопроцессоров. Процессор такого типа называется "гибридным", т. к. он поддерживал набор команд Intel 486™, но устанавливался на материнские платы для 386-х процессоров. Для нормальной работы требовалась поддержка со стороны биоса, т. е. его обновление, которое не всегда было возможно. Эта проблема разрешилась с выходом следующего процессора. Кодовое имя: M0.5. Тех. характеристики: 0,6 млн. транзисторов; тактовая частота: 20-66 МГц; кэш первого уровня: 1 Кб; кэш второго уровня на материнской плате (до 128 Кб); FSB: 16-33 МГц; общая разрядность: 32.

1992г. Cyrix Cx486SRx/DRx

Версия процессоров SLC/DLC, предназначенная для установки на 386-е системы без обновления биоса материнской платы. Кодовое имя: M0.5. Тех. характеристики: 0,6 млн. транзисторов; тактовая частота: 20-66 МГц; кэш первого уровня: 1 Кб; кэш второго уровня на материнской плате (до 128 Кб); FSB: 16-33 МГц; общая разрядность: 32.

1993г. Cyrix Cx486S

Аналог Intel 486™SX без математического сопроцессора. Кодовое имя: M0.6. Тех. характеристики: 0,6 млн. транзисторов; тактовая частота: 33-50 МГц; кэш первого уровня: 2 Кб; кэш второго уровня на материнской плате (до 512 Кб); FSB: 20-50 МГц; общая разрядность: 32.

1993г. Cyrix Cx486DX

Этот процессор обзавёлся математическим сопроцессором и увеличенным кэшем (8 Кб), что привело к увеличению колличества транзисторов до 1.1 млн. Кодовое имя: M0.7. Тех. характеристики: 1,1 млн. транзисторов; тактовая частота: 33-50 МГц; кэш первого уровня: 8 Кб; кэш второго уровня на материнской плате (до 512 Кб); FSB: 20-50 МГц; общая разрядность: 32.

1993г. Cyrix Cx486DX2

Cyrix Cx486DX2 имеет только одно отличие от предыдущего: увеличившаяся тактовая частота (66 МГц). Кодовое имя: M0.7. Тех. характеристики: 1,1 млн. транзисторов; тактовая частота: 40-66 МГц; кэш первого уровня: 8 Кб; кэш второго уровня на материнской плате (до 512 Кб); FSB: 20-50 МГц; общая разрядность: 32.

1993г. Cyrix Cx486DX4

Cyrix Cx486DX4 также имеет только одно отличие от предыдущего: увеличившаяся тактовая частота (100 МГц). Кодовое имя: M0.7. Тех. характеристики: 1,1 млн. транзисторов; тактовая частота: 75-100 МГц; кэш первого уровня: 8 Кб; кэш второго уровня на материнской плате (до 512 Кб); FSB: 20-50 МГц; общая разрядность: 32.

1995г. Cyrix 5x86

Этот процессор имел архитектуру пятого поколения, но устанавливался на материнские платы для 486-х процессоров. Позиционировался как конкурент IntelPentium, но, в отличии от него, являлся скалярным процессором, т. е. мог выполнять за один такт только одну инструкцию, а Pentium, как известно, суперскалярный процессор. Кодовое имя: M0.9 или M1sc. Тех. характеристики: 2 млн. транзисторов; технология производства: 0,65 мкм; тактовая частота: 100-120 МГц; кэш первого уровня: 16 Кб; кэш второго уровня на материнской плате (до 512 Кб); FSB: 33-50 МГц; разрядность внутренней шины: 64; общая разрядность: 32.