- •Автоматизированное рабочее место. Его состав, функции, аппаратное и программное обеспечение.

- •Администрирование и мониторинг Windows nt/2000.

- •Адресация в сети Internеt.

- •Алгоритм. Свойства алгоритма. Способы описания алгоритма. Примеры.

- •Аппаратно – зависимые компоненты в ос.

- •Архитектура Windows nt/2000. Ядро и вспомогательные модули ос

- •Архитектура монитора обработки транзакций (схема и описание).

- •Архитектура эвм. Обобщенная структурная схема эвм (классическая).

- •Архитектуры файл – сервер и клиент – сервер локальных сетей.

- •Базовые классы vcl. Характеристика. Примеры.

- •Блокировка в sql Server 2000. Методы управления блокированием ресурсов.

- •Блокировки в sql Server 2000 (2003). Методы управления блокированием ресурсов.

- •Блочно – модульный принцип организации программ в языке Турбо Паскаль. Локальные и глобальные переменные. Примеры.

- •Виды совместимости ос.

- •Внешние устройства пк: диалоговые, запоминающие, телекоммуникационные.

- •Выполнение арифметических операций в двоичной, шестнадцатеричной системах счисления. Примеры

- •Двоичная арифметика. Примеры.

- •Дискретная модуляция аналоговых сигналов. Импульсно – кодовая модуляция.

- •Достоинства и недостатки объектно – ориентированного программирования.

- •Достоинства и недостатки объектно – ориентированной модели данных

- •Жизненный цикл программного обеспечения.

- •Иерархическая модель данных.

- •Иерархическая модель представления данных. Ее достоинства и недостатки.

- •Иерархическая структура памяти эвм: уровни иерархии, назначение зу различных типов.

- •Информатика как наука. Основные направления научных исследований в области информатики.

- •Информационное, аппаратное и программное обеспечение кс: структура и функции.

- •Информационные технологии автоматизированного офиса.

- •Информационные технологии обработки текстовых данных.

- •Использование распределенной файловой системы при работе с бд.

- •Использование триггеров в sql Server 2000.

- •Классификация и краткая характеристика языков программирования

- •Классификация и характеристики принтеров.

- •Классификация периферийных устройств ввода-вывода.

- •Классическая архитектура ос. Ядро и вспомогательные модули ос

- •Кодирование информации. Равномерные и неравномерные коды. Двоичное кодирование.

- •Коммутация каналов в сетях: сущность, оценка, область применения

- •Коммутация пакетов в сетях.

- •Компоненты sql Server 2000 (2003).

- •Компоненты интерфейсов Windows в Delphi.

- •Технологии fddi

- •Концепция виртуальной памяти.

- •Краткая характеристика простых типов данных в языке Турбо Паскаль. Основные функции обработки простых типов данных. Примеры.

- •Линии связи и их характеристики.

- •Логическая и физическая организация файловых систем.

- •Маршрутизация пакетов в сетях: методы маршрутизации, их характеристика и области применения.

- •Методы и средства защиты информации в ккс от несанкционированного доступа.

- •Механизм использования шаблонов в Delphi.

- •Микроядерная архитектура ос.

- •Многомашинные вычислительные системы.

- •Многопроцессорные вычислительные системы.

- •Модуль. Структура модуля в языке Турбо – Паскаль. Примеры.

- •Модуль. Структура модуля в языке Турбо – Паскаль. Примеры.

- •Название и характеристика кэш – памяти

- •Назначение и компоненты хранилища данных.

- •Назначение и роль ос в работе пк. Примеры.

- •Назначение и характеристики системы прерываний. Порядок обработки прерывания.

- •Назначение классов tPersistent и tComponent. Примеры.

- •Назначение центрального процессора (цп). Магистральный принцип передачи информации в цп, его преимущества и недостатки.

- •Назначение, состав и виды ос.

- •Нормальные формы, их назначение.

- •Обеспечение безопасности в Windows nt/2000.

- •Объект. Методы объектов в языке Турбо Паскаль.

- •Операции алгебры логики. Схемы, реализующие основные логические элементы эвм. Примеры.

- •Определение степени связи между сущностями при проектировании бд.

- •Организация ввода – вывода данных в Delphi.

- •Организация параллелизма вычислений в современных процессорах

- •Организация программ в языке Турбо Паскаль. Локальные и глобальные параметры. Примеры.

- •Организация списков в языке Турбо Паскаль. Примеры.

- •Организация циклов

- •Основная характеристика языков запроса бд.

- •Основные показатели оценки качества программы

- •Основные понятия метода проектирования бд, сущность – связь. Примеры.

- •Основные понятия эффективности функционирования кс

- •Основные свойства класса tControl. Примеры

- •Основные события, возникающие от клавиатуры в Delphi. Примеры

- •Операции над строками

- •Основные средства защиты в субд.

- •Основные средства защиты, встроенные в ос.

- •Основные средства разработки бд.

- •Основные структуры алгоритмов, примеры.

- •2. Алгоритмы разветвляющейся структуры

- •3. Алгоритмы циклической структуры

- •4. Алгоритмы со структурой вложенных циклов

- •5. Подчиненные алгоритмы

- •Основные структуры алгоритмов

- •2. Алгоритмы разветвляющейся структуры

- •3. Алгоритмы циклической структуры

- •4. Алгоритмы со структурой вложенных циклов

- •5. Подчиненные алгоритмы

- •Основные типы данных в Object Pascal.

- •Основные типы моделей данных.

- •Основные фунции микропроцессора. Характеристики микропроцессора.

- •Основные характеристики и особенности локальных компьютерных сетей (лкс).

- •Основные характеристики эвм.

- •Основные этапы разработки бд.

- •1. Разработка, утверждение тз и подборка под него готовых частей

- •2. Определение необходимых таблиц и связей между ними, полей таблиц и ключевых полей в бд

- •3. Проектирование интерфейса приложения

- •4. Тестирование, создание документации, сдача проекта и расчет

- •Основные этапы создания приложений в Delphi.

- •Особенности технологий Fast Ethernet и 100 vg'- AnyLan.

- •Перевод чисел из одной системы исчисления в другую (восьмеричная, десятичная, шестнадцатеричная система исчисления). Примеры

- •Передача дискретных данных на канальном уровне: используемые протоколы, способы связи между отправителем и получателем.

- •Передача дискретных данных на физическом уровне: цифровое кодирование и аналоговая модуляция.

- •Передача дискретных данных

- •Переносимость ос на разные аппаратные платформы.

- •Периферийные устройства пк.

- •Перспективы развития кс.

- •Перспективы развития телекоммуникаций в России.

- •Планирование и диспетчеризация потоков в процессе функционирования ос.

- •Подпрограммы – функции. Примеры.

- •Показатели целевой и экономической эффективности функционирования кс

- •Поколения эвм и их краткая характеристика.

- •Понятие «информационная культура». В чем она проявляется?

- •Понятие и классификация информационных технологий.

- •Понятие индекса. Использование индексирования в бд.

- •Понятие информации. Дискретная и аналоговая информация. Носители информации.

- •Понятие информационного общества. Характерные черты информационного общества.

- •Понятие мультипрограммирования. Способы управления процессом в режиме мультипрограммирования.

- •Понятие отношения. Условия, при которых таблицу можно считать отношением.

- •Понятие процесса и потока в ос.

- •Понятие процессов. Виды процессов.

- •Понятие распределенной бд, ее достоинства и недостатки.

- •Порты ввода – вывода: параллельный и последовательный.

- •Представление команд в эвм. Основные стадии выполнения команд.

- •Преимущества и недостатки микроядерной архитектуры ос

- •Прикладные сервисы Internet: электронная почта, телеконференции, почтовые списки, передача файлов.

- •Применение эвм в научных исследованиях, медицине, образовании.

- •Принципы объектно – ориентированного программирования.

- •Принципы построения глобальных компьютерных сетей (гкс).

- •Программы – функции. Вызов функции. Примеры.

- •Проектирование рекурсивных алгоритмов в языке Турбо – Паскаль. Пример.

- •Простые типы данных в языке Турбо Паскаль. Основные функции обработки простых типов данных. Примеры.

- •Процедуры. Формальные, фактические параметры. Примеры.

- •Прямой доступ к памяти

- •Пути совершенствования и развития телекоммуникаций в России

- •Распределение памяти при выполнении программ. Строчные переменные в языке Турбо Паскаль. Примеры.

- •Режимы передачи информации: сущность, оценка, области изменения.

- •Резервное копирование. Типы резервного копирования sql Server 2000.

- •Резервное копирование. Типы резервного копирования sql Server 2000 (2003).

- •Реляционная модель данных.

- •Ресурсы вычислительной системы. Управление ресурсами.

- •Рынок информационных продуктов и услуг. Инфраструктура информационного рынка.

- •Самосинхронизирующие коды: состав, характеристика, области применения.

- •Связывание таблиц в бд. Основные виды связей. Примеры

- •Сетевая модель данных.

- •Сетевое коммуникационное оборудование лкс: состав и назначение.

- •Сетевое оборудование ккс: состав и назначение.

- •Сетевые ос.

- •Система ввода – вывода. Программирование рекурсивных алгоритмов в языке Турбо Паскаль. Примеры.

- •Система ввода вывода : структура с одним общим интерфейсом

- •Система ввода-вывода: структура с каналами ввода-вывода

- •Система команд эвм общего назначения, методы адресации, типы команд, типы и размеры операндов.

- •Системы автоматизированного поиска в Internet: состав и области применения.

- •Системы ввода – вывода: структуры с общим интерфейсом.

- •Системы счисления. Двоичная, восьмеричная, шестнадцатиричная системы счисления. Примеры представления числа в указанных системах счисления

- •Сканеры, модемы, их назначение и характеристики

- •Состав основной памяти компьютера. Конструктивное исполнение модулей памяти.

- •Составляющие элементы реляционной модели данных и формы их представления.

- •Сравнительная характеристика файловых систем fat, ntfs.

- •Средства синхронизации потоков в ос

- •Стандартные визуальные компоненты в Delphi.

- •Странично – сегментная организация памяти

- •Строковые типы данных в языке Турбо Паскаль. Основные процедуры и функции обработки строковых данных. Примеры.

- •Структура и функции программного обеспечения ккс.

- •Структура и функции программного обеспечения лкс.

- •Структура и функции системы обеспечения безопасности (соб) ккс

- •Структура и характеристика языка sql

- •Структура программы в языке Турбо Паскаль

- •Структура проекта в Delphi

- •Структура типов данных в языке Турбо Паскаль.

- •Структурированные типы данных: массивы, записи, множества в языке Турбо Паскаль. Примеры.

- •Структурная организация и взаимодействие узлов и устройств эвм

- •Текстовые файлы в языке Турбо Паскаль. Стандартные средств обработки текстовых файлов. Примеры.

- •Типизированные и нетипизированные файлы в языке Турбо Паскаль. Стандартные средства обработки файлов. Примеры.

- •Типовая структура гкс

- •Типовая структура ккс.

- •Типовая структура ккс.

- •Типовые струкуры многопроцессорных систем

- •Типы гкс и их особенности

- •Типы сетей связи и тенденции их развития

- •Требования к ос. Классификация ос.

- •Трехзвенная модель распределенной системы бд.

- •Управление доступом к передающей среде. Методы и протоколы доступа.

- •Управление проектами в Delphi.

- •Условные конструкции языка Турбо Паскаль. Примеры.

- •Форма. Управление понятиями формы в Delphi. Примеры.

- •Формы представления чисел в эвм. Коды чисел: прямой, обратный, дополнительный

- •Характеристика Microsoft sql Server 2000. Компоненты sql Server 2000.

- •Характеристика Windows 2003.

- •Характеристика Windows nt/2000.

- •Характеристика внешних запоминающих устройств (взу).

- •1. Накопители на жестких магнитных дисках

- •2. Накопители на компакт-дисках

- •4. Накопители на гибких магнитных дисках

- •Характеристика и области применения сетей Frame Relay.

- •Характеристика и области применения сетей isdn.

- •Характеристика и области применения сетей атм.

- •Характеристика и области применения сетей х.25

- •Характеристика интегрированной среды разработки программ Delphi.

- •Характеристика класса tObject. Методы класса. Примеры.

- •Характеристика клиентского программного обеспечения в Internet.

- •Характеристика накопителей на гибких и жестких магнитных дисках.

- •Накопители на жестких дисках

- •Характеристика протоколов семейства tcp/ip

- •Характеристика сетевой модели данных.

- •Характеристика спутниковых сетей связи.

- •Характеристика технологии Ethernet.

- •Характеристика языка sql. Функциональные категории языка sql.

- •Характеристика языка программирования Турбо Паскаль.

- •Характеристики основных топологий в лкс.

- •Эталонная модель взаимодействия открытых систем osi.

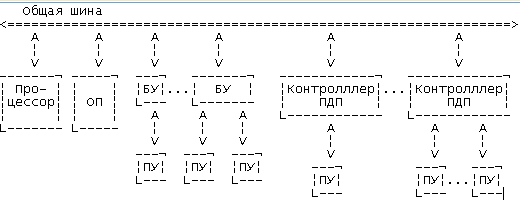

Система ввода вывода : структура с одним общим интерфейсом

Структура с одним общим интерфейсом

Структура с одним общим интерфейсом предполагает наличие общей шины, к которой подсоединяются все модули, в совокупности образующие ЭВМ: процессор, оперативная и постоянная память и периферийные устройства. В каждый данный момент через общую шину может происходить обмен данными только между одной парой присоединенных к ней модулей. Таким образом, модули ЭВМ разделяют во времени один общий интерфейс, причем процессор выступает как один из модулей системы.

Периферийные устройства подсоединяются к общей шине с помощью блоков управления периферийными устройствами (контроллеров), осуществляющих согласование форматов данных периферийных устройств с форматом, принятым для передачи по общей шине.

Если в периферийном устройстве операции ввода - вывода производятся для отдельных байт или слов, то используется программно-управляемая передача данных через процессор и под его управлением. Конструкция контроллера при этом сильно упрощается.

Для перифериийных устройств с поблочной передачей данных (ЗУ на дисках, лентах и др.) применяется прямой доступ к памяти и контроллеры ПДП.

При общем интерфейсе аппаратура управления вводом-выводом рассредоточена по отдельным модулям ЭВМ. Процессор при этом не полностью освобождается от управления операциями ввода-вывода.

Более того, на все время операции передачи данных интерфейс оказывается занятым, а связь процессора с памятью блокированной.

Интерфейс с общей шиной применяется только в малых и микро-ЭВМ, которые имеют короткое машинное слово, небольшой объем периферийного оборудования и от которых не требуется высокой производительности.

Система ввода-вывода: структура с каналами ввода-вывода

Структура системы с процессорами (каналами) ввода-вывода применяется в высокопроизводительных ЭВМ. В таких ЭВМ система ввода-вывода строится путем централизации аппаратуры управления вводом-выводом на основе применения программно-управляемых процессоров (каналов) ввода-вывода. Обмен информацией между памятью и периферийным устройством осуществляется через канал ввода-вывода

Каналы ввода-вывода полностью освобождают процессор от управления операциями ввода-вывода.

В вычислительной машине с каналами ввода-вывода форматы передаваемых данных неоднородны, поэтому необходимо использовать в ЭВМ несколько специализированных интерфейсов.

Можно выделить четыре типа интерфейсов: интерфейс основной памяти, интерфейс процессор-каналы, интерфейсы ввода-вывода, интерфейсы периферийных устройств (малые интерфейсы).

Через интерфейс основной памяти производится обмен информацией между памятью, с одной стороны, и процессором и каналами – с другой.

Интерфейс процессор-каналы предназначается для передачи информации между процессорами и каналами ввода-вывода.

Через интерфейс ввода-вывода происходит обмен информацией между каналами и блоками управления периферийных устройств.

Система команд эвм общего назначения, методы адресации, типы команд, типы и размеры операндов.

Методы адресации

В машинах с регистрами общего назначения метод (или режим) адресации объектов, с которыми манипулирует команда, может задавать константу, регистр или ячейку памяти. Для обращения к ячейке памяти процессор прежде всего должен вычислить действительный или эффективный адрес памяти, который определяется заданным в команде методом адресации.

Система команд 32-разрядных процессоров предусматривает 11 режимов адресации. При этом только в двух случаях операнды не связаны с памятью. Это операнд-содержимое регистра, которое берется из любого 8-, 16- или 32-битного регистра процессора, и непосредственный операнд (8, 16 или 32 бит), который содержится в самой команде. Остальные девять режимов так или иначе обращаются к памяти.

При обращении к памяти эффективный адрес вычисляется с использованием следующих компонентов.

• Смещение (Displacement или Disp) – 8-, 16- или 32-битное число, включенное в команду.

• База (Base) – содержимое базового регистра. Обычно используется для указания на начало некоторого массива.

• Индекс (Index) – содержимое индексного регистра. Обычно используется для выбора элемента массива.

• Масштаб (Scale) – множитель (1, 2, 4 или 8), указанный в коде инструкции. Этот элемент используется для указания размера элемента массива, доступен только при 32-битной адресации.

Эффективный адрес вычисляется по формуле:

EA=Base + Index Scale + Disp.

Использование сложных методов адресации позволяет существенно сократить количество команд в программе, но при этом значительно увеличивается сложность аппаратуры. Важным вопросом построения любой системы команд является оптимальное кодирование команд. Оно определяется количеством регистров и применяемых методов адресации, а также сложностью аппаратуры, необходимой для декодирования. Именно поэтому в современных RISC архитектурах используются достаточно простые методы адресации, позволяющие резко упростить декодирование команд. Более сложные и редко встречающиеся в реальных программах методы адресации реализуются с помощью дополнительных команд, что приводит к увеличению размера программного кода. Однако такое увеличение длины программы с лихвой окупается возможностью простого увеличения тактовой частоты RISC-процессоров.

Типы команд

Команды 32-разрядных процессоров содержат одно- или двухбайтный код инструкции, за которым могут следовать несколько байт, определяющих режим исполнения команды, и операнды. Команды могут использовать до трех операндов (или ни одного). Операнды могут находиться в памяти, регистрах процессора или непосредственно в команде. Для 32-разрядных процессоров разрядность слова (word) по умолчанию может составлять 32 бит. Это распространяется на многие инструкции, включая и строковые. В реальном режиме и режиме виртуального процессора 8086 по умолчанию используется 16-битная адресация и 16-битные операнды-слова. В защищенном режиме режим адресации и разрядность слова по умолчанию определяются дескриптором кодового сегмента. Перед любой инструкцией может быть использован префикс переключения разрядности адреса или слова.

В системе команд насчитывается несколько сотен инструкций, которые можно группировать по разным признакам. Для удобства здесь все инструкции сгруппированы по функциональной общности.

1.Инструкции пересылки данных позволяют передавать константы или переменные между регистрами и памятью, а также портами ввода/вывода в различных комбинациях, но в памяти может находиться не более одного операнда. В эту группу отнесены и инструкции преобразования форматов – расширений и перестановки байт. Операции со стеком выполняются словами с разрядностью, определяемой текущим режимом.

2.Инструкции двоичной арифметики выполняют все арифметические действия с байтами, словами и двойными словами, кодирующими знаковые или беззнаковые целые числа.

3.Инструкции десятичной арифметики являются дополнением к предыдущим. Они позволяют оперировать с неупакованными (биты 7–4 равны нулю, биты 3–0 содержат десятичную цифру 0–9) или упакованными (биты 7–4 содержат старшую, биты 3–0 – младшую десятичную цифру 0–9) двоично-десятичными числами. Арифметические операции над этими числами требуют применения инструкций коррекции форматов.

4.Инструкции логических операций выполняют все функции булевой алгебры над байтами, словами или двойными словами.

5.Сдвиги и вращения (циклические сдвиги) выполняются над регистром или операндом в памяти. При сдвигах влево и простом сдвиге вправо освобождающиеся биты заполняются нулями. При арифметическом сдвиге вправо старший бит (знак) сохраняет свое значение. При циклических сдвигах выталкиваемые биты попадают в освобождающиеся позиции.

6.Инструкции обработки бит и байт позволяют проверять и устанавливать значение указанного операнда, а также искать установленный бит. Битовые операции выполняются над 16- или 32-битными словами. Инструкция тестирования может выполняться над байтом, словом или двойным словом.

7.Передача управления осуществляется с помощью инструкций безусловных и условных переходов, вызовов процедур и прерываний (исключений). Безусловный переход (JMP) может быть как внутрисегментным (ближним или коротким), так и межсегментным (дальним). Адрес перехода может непосредственно указываться в команде, а при косвенной адресации он находится в регистре или памяти и может иметь дополнительные слагаемые. Короткий переход (short) может передавать управление только на адрес назначения, удаленный от текущего в пределах -128...+127 байт, ближний (near) – в пределах сегмента. При дальнем (far) переходе адрес назначения (непосредственный или косвенный) включает новое значение указателя инструкций и значение (или селектор) сегмента кода, обеспечивая доступ к любой точке памяти (в пределах, разрешенных защитой).

Условные переходы в 8086 и 80286 возможны только короткие (8-байтное смещение), процессоры 386+ допускают переход в пределах 16- или 32-байтного смещения, в зависимости от режима адресации.

Инструкция вызова процедуры сохраняет адрес следующей за ней инструкции в стеке и передает управление в заданную точку.

8.Строковые операции выполняются с операндами в памяти. Операции могут использоваться с префиксами условного или безусловного повтора. Строковые инструкции ввода/вывода с префиксами повтора позволяют достигать высоких скоростей обмена с портами при условии полной загрузки процессора.

9.Операции с флагами позволяют изменять значения отдельных флагов, а также сохранять их значение в стеке и восстанавливать сохраненные значения.

10.Инструкции загрузки указателей позволяют загружать дальние указатели из памяти в регистр общего назначения и соответствующий сегментный регистр.

11.К системным инструкциям относятся инструкции управления защитой – загрузки и сохранения регистров дескрипторов и регистра задачи; проверки и выравнивания привилегий; обмена с управляющими, отладочными и модельно-специфическими (включая тестовые) регистрами; управления кэшированием, захвата шины и остановки процессора. Для прикладных программ использование этих инструкций нехарактерно.

Типы и размеры операндов

Имеется два альтернативных метода определения типа операнда. В первом из них тип операнда может задаваться кодом операции в команде. Это наиболее употребительный способ задания типа операнда. Второй метод предполагает указание типа операнда с помощью тега, который хранится вместе с данными и интерпретируется аппаратурой во время выполнения операций над данными. Этот метод в настоящее время практически не применяется и все современные процессоры пользуются первым методом.

Обычно тип операнда (например, целый, вещественный с одинарной точностью или символ) определяет и его размер. Однако часто процессоры работают с целыми числами длиною 8, 16, 32 или 64 бит. Как правило, целые числа представляются в дополнительном коде. Для задания символов (1 байт = 8 бит) в машинах компании IBM используется код EBCDIC, но в машинах других производителей почти повсеместно применяется кодировка ASCII. Еще до сравнительно недавнего времени каждый производитель процессоров пользовался своим собственным представлением вещественных чисел (чисел с плавающей точкой). Однако за последние несколько лет ситуация изменилась. Большинство поставщиков процессоров в настоящее время для представления вещественных чисел с одинарной и двойной точностью придерживаются стандарта IEEE 754.

В некоторых процессорах используются двоично-кодированные десятичные числа, которые представляются в упакованном и неупакованном форматах. Упакованный формат предполагает, что для кодирования цифр 0–9 используются 4 разряда и что две десятичные цифры упаковываются в каждый байт. В неупакованном формате байт содержит одну десятичную цифру, которая обычно изображается в символьном коде ASCII.

В большинстве процессоров, кроме того, реализуются операции над цепочками (строками) бит, байт, слов и двойных слов.