- •Аналитический обзор систем охранных сигнализаций

- •Разработка структурной схемы многоканальной охранной сигнализации

- •Разработка схемы электрической принципиальной

- •3.3 Выбор элементной базы

- •3.6 Разработка электрической принципиальной схемы многоканальной охранной сигнализации

- •3.7 Алгоритм работы многоканальной охранной сигнализации

- •Производственная санитария и гигиена труда в помещении нил

- •Расчет для помещения

- •5.4 Пожарная профилактика помещения нил

- •6. Экономическое обоснование проекта

- •6.4 Определение экономической эффективности результатов нир

Разработка структурной схемы многоканальной охранной сигнализации

2.1 Обобщенная структурная схема охранных сигнализаций

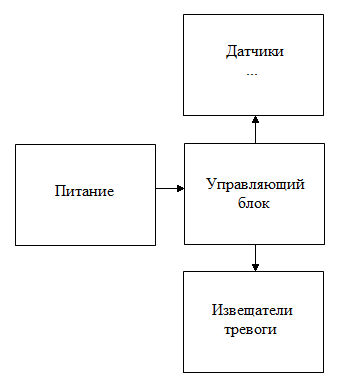

Система сигнализации предназначена для установки в квартире или любом другом помещении, нуждающемся в охране и оповещать звуковым сигналом, при срабатывании одного из датчиков, хозяина данного помещения либо охрану. Разрабатываемая система сигнализации может найти применение в любом помещении, нуждающемся в охране. Все системы сигнализации работают схожим принципом и имеют подобные блоки, независимо от ввода и вывода информации. Обобщенная схема охранных сигнализации показана на рисунке 2.1.

Рисунок 2.1 – Структурная схема охранной сигнализации

На рисунке 2.1 показано, что во всех охранных сигнализация присутствует блок питания для приведения стандартного напряжения электросети к необходимому уровню напряжений питания элементов схемы и источник бесперебойного питания.

Управляющим блоком опрашиваются датчики с различными величинами и состояниями. Полученная информация с датчиков обрабатывается и сравнивается с состоянием по умолчанию управляющим блоком. В случае различия полученного сигнала с сигналом по умолчанию управляющий блок генерирует соответствующий сигнал в извещающий блок. Раздается сигнал тревоги, либо охранно-контрольный пункт ставится в известность о нарушении периметра.

Разработка структурной схемы многоканальной охранной сигнализации

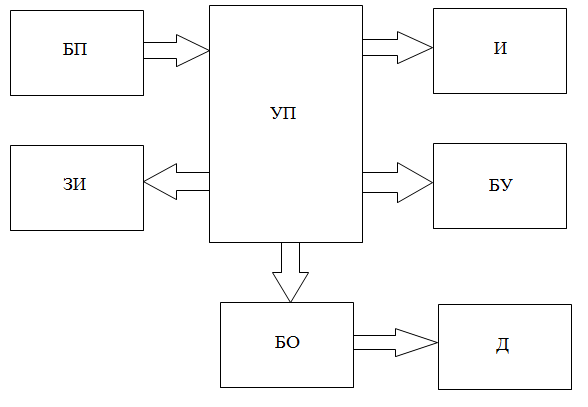

Разработка структурной схемы является начальным этапом проектирования любого электронного устройства. Структурной называется схема, которая определяет основные функциональные части изделия и связи между ними. Структурная схема лишь в общих чертах раскрывает назначение устройства и его функциональных частей, а также взаимосвязи между ними, и служит лишь для общего ознакомления с изделием. Составные части проектируемого устройства изображаются упрощенно в виде прямоугольников произвольной формы, т.е. с применением условно-графических обозначений. Внутри каждого прямоугольника, функционального узла устройства, указаны наименования, которые очень кратко описывают предназначение конкретного блока. Структурная схема многоканальной сигнализации состоит из блоков (рисунок 2.2):

- БП – стандартный блок питания с аккумуляторной батареей, обеспечивает питание сигнализации даже в аварийном режиме в случае отсутствия стационарного питания;

- ЗИ – звуковой извещатель, извещает хозяев или охрану соответствующим звуком в случае нарушения охраняемого периметра;

- УП – управляющий блок, контролирует систему сигнализации;

- БО – блок опроса, опрашивает датчики на наличие изменения сигнала;

- И – блок индикации, отображает включение, сеть и нарушение периметра;

- БУ – блок управления, включает в себя кнопки включения и сброса работы устройства;

Рисунок 2.2 – Структурная схема многоканальной охранной сигнализации

Разработка схемы электрической принципиальной

3.3 Выбор элементной базы

В настоящее время выпускается целый ряд типов МК. Все эти приборы можно условно разделить на три основных класса:

– 8-разрядные МК для встраиваемых приложений;

– 16- и 32-разрядные МК;

– цифровые сигнальные процессоры (DSP).

Наиболее распространенным представителем семейства МК являются 8-разрядные приборы, широко используемые в промышленности, бытовой и компьютерной технике. Они прошли в своем развитии путь от простейших приборов с относительно слаборазвитой периферией до современных многофункциональных контроллеров, обеспечивающих реализацию сложных алгоритмов управления в реальном масштабе времени. Причиной жизнеспособности 8-разрядных МК является использование их для управления реальными объектами, где применяются, в основном, алгоритмы с преобладанием логических операций, скорость обработки которых практически не зависит от разрядности процессора.

Росту популярности 8-разрядных МК способствует постоянное расширение номенклатуры изделий, выпускаемых такими известными фирмами, как Motorola, Microchip, Intel, Zilog, Atmel и многими другими. Современные 8-разрядные МК обладают, как правило, рядом отличительных признаков. Перечислим основные из них:

– модульная организация, при которой на базе одного ядра проектируется ряд (линейка) МК, различающихся объемом и типом памяти программ, объемом памяти данных, набором периферийных модулей, частотой синхронизации;

– использование закрытой архитектуры МК, которая характеризуется отсутствием линий магистралей адреса и данных на выводах корпуса МК. Таким образом, МК представляет собой законченную систему обработки данных, наращивание возможностей которой с использованием параллельных магистралей адреса и данных не предполагается;

– использование типовых функциональных периферийных модулей (таймеры, счетчики, контроллеры последовательных интерфейсов, аналого-цифровые преобразователи и др.), имеющих незначительные отличия в алгоритмах работы в МК различных производителей;

– расширение числа режимов работы периферийных модулей, которые задаются в процессе инициализации регистров специальных функций МК.

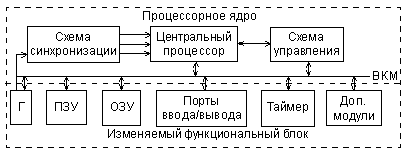

При модульном принципе построения все МК одного семейства содержат ядро, одинаковое для всех МК данного семейства, и изменяемый функциональный блок, который отличает МК разных моделей. Структура модульного МК приведена на рисунке 3.1.

Ядро включает в себя:

– АЛУ;

– внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления;

– схему синхронизации МК;

– схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса) и т.д.

Изменяемый функциональный блок включает в себя модули памяти различного типа и объема, порты ввода/вывода, модули тактовых генераторов, таймеры. В относительно простых МК модуль обработки прерываний входит в состав ядра. В более сложных МК он представляет собой отдельный модуль с развитыми возможностями. В состав изменяемого функционального блока могут входить и такие дополнительные модули как компараторы напряжения, аналого-цифровые преобразователи и другие. Каждый модуль проектируется для работы в составе МК с учетом протокола внутренней контроллерной магистрали. Данный подход позволяет создавать разнообразные по структуре МК в пределах одного семейства.

Рисунок 3.1 – Модульная организация МК

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

– набор регистров для хранения промежуточных данных;

– система команд процессора;

– способы адресации операндов в пространстве памяти;

– организация процессов выборки и исполнения команды.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализует один из двух принципов построения процессоров:

– контроллеры с CISC-архитектурой, реализующие так называемую полную систему команд (Complicated Instruction Set Computer);

– контроллеры с RISC-архитектурой, реализующие сокращенную систему команд (Reduced Instruction Set Computer).

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК процессор с CISC-архитектурой может иметь однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. При этом система команд, как правило, неортогональна, то есть не все команды могут использовать любой из способов адресации применительно к любому из регистров процессора. Выборка команды на исполнение осуществляется побайтно в течение нескольких циклов работы МК. Время выполнения команды может составлять от 1 до 12 циклов. К МК с CISC-архитектурой относятся МК фирмы Intel с ядром MCS-51, которые поддерживаются в настоящее время целым рядом производителей, МК семейств НС05, НС08 и НС11 фирмы Motorola и ряд других.

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК серии PIC16 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

Во-первых, оценка производительности МК по времени выполнения команд различных систем (RISC и CISC) не совсем корректна. Обычно производительность МП и МК принято оценивать числом операций пересылки «регистр-регистр», которые могут быть выполнены в течение одной секунды. В МК с CISC-архитектурой время выполнения операции «регистр-регистр» составляет от 1 до 3 циклов, что, казалось бы, уступает производительности МК с RISC-архитектурой. Однако стремление к сокращению формата команд при сохранении ортогональности системы команд RISC-контроллера приводит к вынужденному ограничению числа доступных в одной команде регистров. Так, например, системой команд МК PIC16 предусмотрена возможность пересылки результата операции только в один из двух регистров — регистр-источник операнда f или рабочий регистр W. Таким образом, операция пересылки содержимого одного из доступных регистров в другой (не источник операнда и не рабочий) потребует использования двух команд. Такая необходимость часто возникает при пересылке содержимого одного из регистров общего назначения (РОН) в один из портов МК. В то же время, в системе команд большинства CISC-контроллеров присутствуют команды пересылки содержимого РОН в один из портов ввода/вывода. То есть более сложная система команд иногда позволяет реализовать более эффективный способ выполнения операции.

Во-вторых, оценка производительности МК по скорости пересылки «регистр-регистр» не учитывает особенностей конкретного реализуемого алгоритма управления. Так, при разработке быстродействующих устройств автоматизированного управления основное внимание следует уделять времени выполнения операций умножения и деления при реализации уравнений различных передаточных функций. А при реализации пульта дистанционного управления бытовой техникой следует оценивать время выполнения логических функций, которые используются при опросе клавиатуры и генерации последовательной кодовой посылки управления. Поэтому в критических ситуациях, требующих высокого быстродействия, следует оценивать производительность на множестве тех операций, которые преимущественно используются в алгоритме управления и имеют ограничения по времени выполнения.

В-третьих, необходимо еще учитывать, что указанные в справочных данных на МК частоты синхронизации обычно соответствуют частоте подключаемого кварцевого резонатора, в то время как длительность цикла МК определяется частотой обмена по ВКМ. Соотношение этих частот индивидуально для каждого МК и должно быть принято в расчет при сравнении производительности различных моделей контроллеров.

С точки зрения организации процессов выборки и исполнения команды в современных 8-разрядных МК применяется одна из двух уже упоминавшихся архитектур МПС: фон-неймановская (принстонская) или гарвардская.

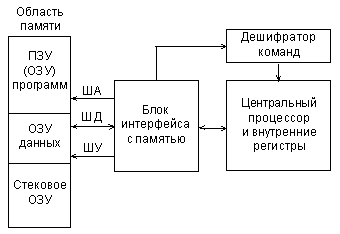

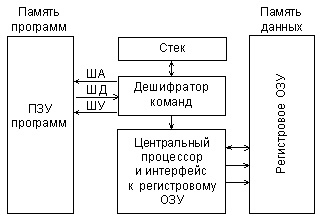

Основной особенностью фон-неймановской архитектуры является использование общей памяти для хранения программ и данных, как показано на рисунке 3.2.

Рисунок 3.2 – Структура МПС с фон-неймановской архитектурой

Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МПС с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтому фон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных, как показано на рисунке 3.3.

Рисунок 3.3 – Структура МПС с гарвардской архитектурой

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению[10][11].

3.4 Описание микроконтроллера ATmega8

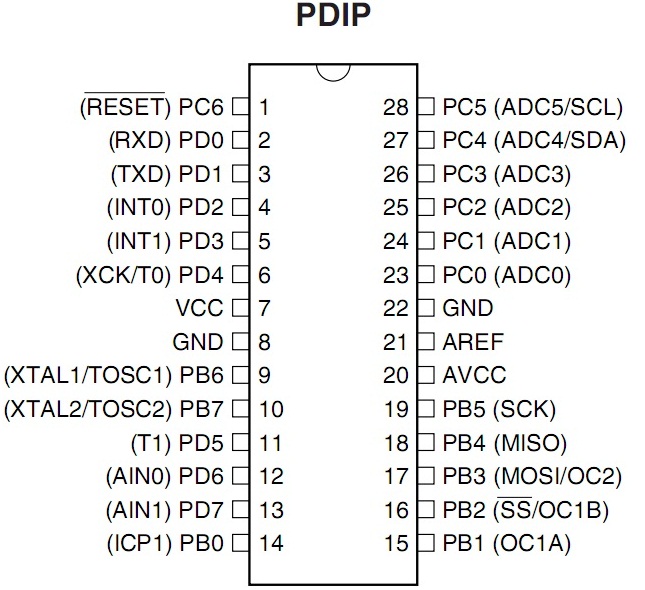

Обоснование выбора микроконтроллера заключается в максимальной подгонки микросхемы под многоканальную охранную систему сигнализации, а это подходящий объем памяти, его архитектура, быстродействие, количество команд, выполнение большого количества инструкций за один машинный цикл, требования по питанию. Следовательно выбор микроконтроллера из другой серии даст нам лишь переизбыток в выделенной памяти, в количестве регистров, счетчиков, а это увеличение цены. ATmega8 это маломощный CMOS 8-битный микропроцессор основанный на AVR RISC архитектуре. За счет выполнения большинства инструкций за один машинный цикл ATmega8 достигает производительности 1 млн. операций в секунду/МГц, что позволяет проектировщикам систем оптимизировать соотношение энергопотребления и быстродействия. Цоколевка ATmega8 изображена на рисунке 3.4.

Рисунок 3.4 – Цоколевка ATmega8

Таблица 3.1 – Назначение выводов ATmega8

Название |

№ вывода |

Функция |

Описание |

PC6(Reset) |

1 |

Цифровой вход |

Системный сброс |

PD0(RXD) |

2 |

Цифровой вход |

Вход данных USART |

PD1(TXD) |

3 |

Цифровой вход |

Выход данных USART |

PD2(INT0) |

4 |

Цифровой вход |

Запрос на прерывание |

PD3(INT1) |

5 |

Цифровой вход |

Запрос на прерывание |

PD4(XCK/T0) |

6 |

Цифровой вход |

Вход внешнего таймера |

VCC |

7 |

Питание |

Цифровое питание |

GND |

8 |

Питание |

Цифровая земля |

PB6(XTAL1) |

9 |

Цифровой вход |

Вход синхронизации |

PB7(XTAL2) |

10 |

Цифровой вход |

Вход синхронизации |

PD5(T1) |

11 |

Цифровой вход |

Вход таймера счетчика 1 |

PD6(AIN0) |

12 |

Аналоговый вход |

Положительный вход 0 |

PD7(AIN1) |

13 |

Аналоговый вход |

Отрицательный вход 1 |

PB0(ICP1) |

14 |

Цифровой вход |

Вход таймера счетчика |

PB1(OC1A) |

15 |

Цифровой вход |

Вход компаратора А |

PB2(SS/OC1B) |

16 |

Цифровой вход |

Вход компаратора В |

PB3(MOSI) |

17 |

Цифровой вход |

Вход загрузки данных |

PB4(MISO) |

18 |

Цифровой вход |

Выход чтения памяти |

PB5(SCK) |

19 |

Цифровой вход |

Вход тактовых импульсов |

Продолжение таблицы 3.1 - Назначение выводов ATmega8 |

|||

AVCC |

20 |

Питание |

Питание ЦАП |

AREF |

21 |

Питание |

Опорное напряжение ЦАП |

GND |

22 |

Питание |

Аналоговая земля |

PC0(ADC0) |

23 |

Аналоговый вход |

Вход АЦП |

PC1(ADC1) |

24 |

Аналоговый вход |

Вход АЦП |

PC2(ADC2) |

25 |

Аналоговый вход |

Вход АЦП |

PC3(ADC3) |

26 |

Аналоговый вход |

Вход АЦП |

PC4(SDA) |

27 |

Цифровой вход |

Вход данных |

PC5(SCL) |

28 |

Цифровой вход |

Вход синхронизации |

Отличительные особенности:

– 130 мощных инструкций, большинство из которых выполняются за один машинный цикл;

– 32 × 8-разр. регистров общего назначения + регистры управления встроенной периферией;

– полностью статическая работа;

– производительность до 16 миллионов команд в секунду при тактовой частоте 16 МГц;

– встроенное умножающее устройство выполняет умножение за 2 машинных цикла;

Энергонезависимая память программ и данных:

– износостойкость 8 кбайт внутрисистемно перепрограммируемой флэш-памяти: 1000 циклов запись/стирание;

– 512-байтовый EEPROM;

– 1-килобайтовый внутренний SRAM;

– запись/стирание циклов: 10000 Flash/100000 EEPROM;

– хранение данных: 20 лет в 85°C/100 лет в 25°C;

– программируемая защита кода ;

Периферийные особенности:

– два 8-разр. таймера-счетчика с раздельными предделителями и режимами сравнения;

– один 16-битовый таймер-счетчик с отдельными предделителем, режимами сравнения и режимами захвата;

– ЦАП с 6 каналами в корпусе PDIP, с программируемым разрешением 10 разрядов;

– программируемый последовательный USART;

– ведущий/подчиненный последовательный интерфейс SPI ;

– программируемый сторожевой таймер со встроенным генератором

– встроенный аналоговый компаратор;

Специальные возможности микроконтроллера:

– сброс при подаче питания и программируемая схема сброса при снижении напряжения питания;

– встроенный калиброванный RC-генератор;

– внешние и внутренние источники прерываний;

– пять режимов снижения энергопотребления: холостой ход (ldle), уменьшение шумов АЦП, экономичный (Power-save), выключение (Power-down), дежурный (Standby);

Ввод - вывод и корпуса:

– 23 программируемые линии ввода – вывода;

– PDIP с 28 лидерством, TQFP с 32 лидерством, и QFN/MLF с 32 подушками;

Рабочие напряжения:

– 4.5V - 5.5V (ATmega8);

Градация по быстродейтсвию:

– 0 - 8 МГц (ATmega8L);

– 0 - 16 МГц (ATmega8);

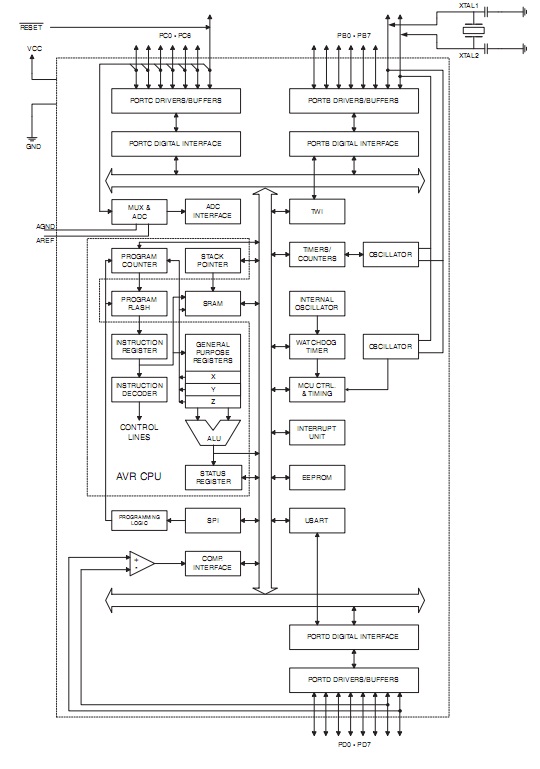

Рисунок 3.5 – Функциональная схема контроллера ATmega8

Ядро AVR сочетает богатый набор инструкций с 32 универсальными рабочими регистрами. Все 32 регистра непосредственно подключены к арифметико-логическому устройству (АЛУ), который позволяет указать два различных регистра в одной инструкции и выполнить ее за один цикл. Данная архитектура обладает большей эффективностью кода за счет достижения производительности в 10 раз выше по сравнению с обычными CISC-микроконтроллерами.

ATmega8 содержит следующие элементы: 8 кбайт внутрисистемно программируемой флэш-памяти с поддержкой чтения во время записи, 512 байт ЭСППЗУ, 1 кбайт статического ОЗУ, 23 линии универсального ввода-вывода, 32 универсальных рабочих регистра, счетчик реального времени (RTC), три гибких таймера-счетчика с режимами сравнения.

Микроконтроллер производится по технологии высокоплотной энергонезависимой памяти компании Atmel. Встроенная внутрисистемно программируемая флэш-память позволяет перепрограммировать память программ непосредственно внутри системы через последовательный интерфейс SPI с помощью простого программатора или с помощью автономной программы в загрузочном секторе. Загрузочная программа может использовать любой интерфейс для загрузки прикладной программы во флэш-память. Программа в загрузочном секторе продолжает работу в процессе обновления прикладной секции флэш-памяти, тем самым поддерживая двухоперационность: чтение во время записи. За счет сочетания 8-разр. RISC ЦПУ с внутрисистемно самопрограммируемой флэш-памятью в одной микросхеме

ATmega8 поддерживается полным набором программных и аппаратных средств для проектирования, в т.ч.: Си-компиляторы, макроассемблеры, программные отладчики/симуляторы, внутрисистемные эмуляторы и оценочные наборы[12].

3.5 Описание шины

Шина I2C широко используется в бытовой электронике, передаче данных и промышленной электронике. Разработанная фирмой Philips простая двунаправленная 2-проводная шина для эффективного управления и взаимодействия различных блоков телевизоров, она стала применяться для связи между собой однокристальных микроконтроллеров, ЖКИ-индикаторов, портов ввода-вывода, микросхем памяти (особенно энергонезависимой), аналого-цифровых и цифро- аналоговых преобразователях, цепях цифровой настройки, DTMF кодеров и декодеров, часов реального времени и т.д.

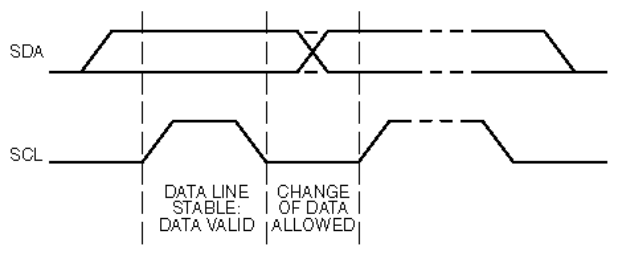

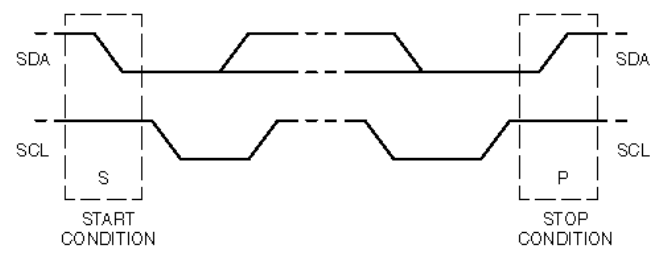

Передача бита. Из-за разнообразия различных технологий (CMOS, NMOS, биполярные приборы) которые могут быть использованы с шиной , уровни логического “0” и “1” не установлены и зависят от величины питающего напряжения VDD. Для передачи одного бита данных используется один импульс сигнала синхронизации, при этом уровень на линии SDA должен быть неизменным в течение высокого уровня на линии SCL, и может изменяться только при низком уровне на SCL (Рисунок 3.6). Исключениями служат два особых состояния - START и STOP.

Рисунок 3.6 – Передача бита

START и STOP. Существуют два особых состояния шины - start и stop, которые служат для индикации начала и конца передачи и соответственно перехода шины в неактивное состояние. Следует отметить, что до тех пор, пока не установлено состояние start, сигналы на линиях SDA и SCL могут быть совершенно произвольными (Рисунок 3.7). Это позволяет, в частности, использовать одну линию SDA и несколько линий SLC (например, при нехватке, адресов на одной шине).

Состояние START - переход от “1” к “0” на линии SDA при “1” на

линии SCL.

Состояние STOP - переход от “0” к “1” на линии SDA при “1” на

линии SCL.

Эти два состояния всегда генерируются мастером. Детектирование состояний start и stop в специализированных элементах обычно производится аппаратно. При полностью программной реализации шины в микроконтроллерах без аппаратной -части необходимо как минимум 2 раза проверять состояние линии SDA.

Рисунок 3.7 – Состояния START и STOP

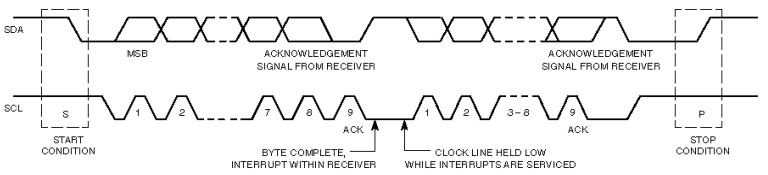

Передача данных. Все передачи производятся 8-разрядными байтами. Число байтов, которые могут быть переданы за одну передачу не ограничено. Каждый байт должен сопровождаться битом подтверждения (ACK). Данные передаются начиная со старшего бита (MSB),(Рисунок 3.8). Если приемник не может получать другой полный байт данных, он не выдает сигнал ACK, который используется передатчиком для синхронизации или сигнализации о неисправности приемника (или его отсутствии).

Рисунок 3.8 – Передача данных по шине

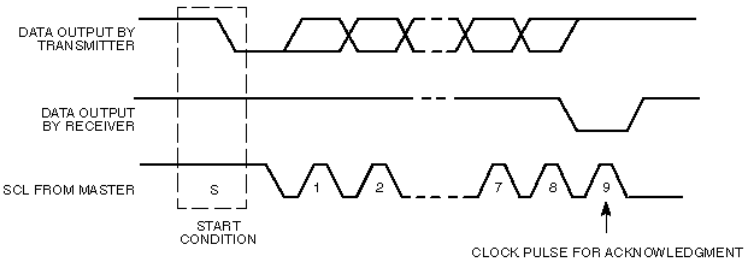

Для подтверждения передачи байта передатчик устанавливает линию SDA в “1” в течение синхронизирующего импульса. Приемник при этом должен выставить “0” на SDA (рисунок 3.9). Естественно при этом должны бить выдержаны определенные временные соотношения. Обычно, приемник, который был адресован, должен генерировать сигнал ACK после того, как каждый байт был получен, за исключением того, когда сообщение начинается с адресом CBUS. Когда подчиненный приемник не подтверждает подчиненный адрес (например, устройство не готово, потому что это выполняет некоторую внутреннюю функцию), линия SDA данных должна быть оставлена в “1”. Мастер затем может выдать состояние STOP, чтобы прервать передачу. Если подчиненный приемник подтверждает подчиненный адрес, но, некоторое время позднее не может получать больше байты данных, мастер должен приостановить передачу. При приеме последнего байта в серии, вместо сигнала ACK мастер может выставить состояние STOP, при этом подчиненный передатчик должен освободить линию данных.

Рисунок 3.9 – Подтверждение передачи

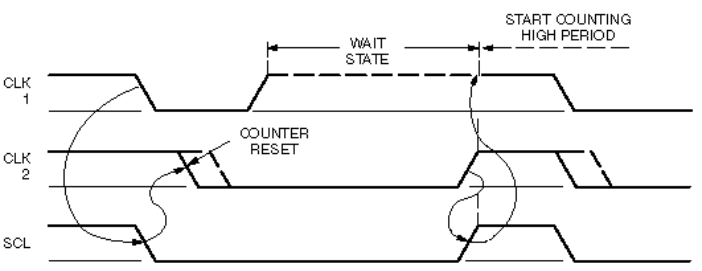

Синхронизация. Каждое мастер-устройство генерирует собственные сигналы синхронизации на линии SCL. Данные на линии SDA действительны только течение ВЫСОКОГО уровня SCL. Синхронизация осуществляется благодаря “монтажному-И” на линии SCL. Это означает, что состояние “0” на линии SCL будет длиться до тех пор, пока все мастер-устройства не освободят линию синхронизации (рисунок 3.10). Линия SCL будет, следовательно, задержана в уровне “0” элементом с самым длинным уровнем “0”. Элементы с более коротким уровнем “0” при этом входят в состояние ожидания.

Рисунок 3.10 – Синхронизация в течение процедуры арбитажа

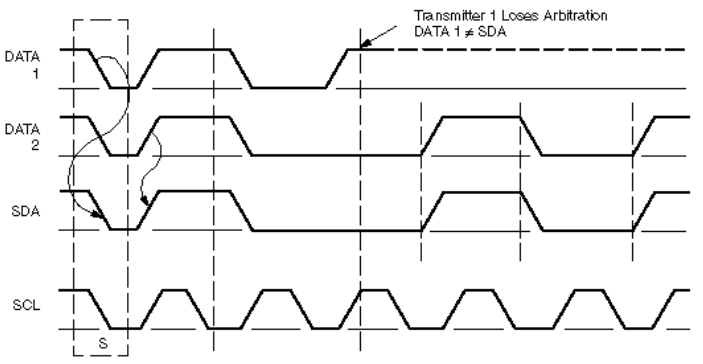

Арбитраж. Мастер может начинать передачу только, если шина свободна. Два или больше мастера могут генерировать состояние START практически одновременно, поэтому необходим арбитраж между ними, для того чтобы выяснить, кто же их них все-таки был первым. Для этого используется линия SDA - благодаря тому, что она, как и SCL выполнена по схеме “монтажное-И” (Рисунок 3.11 показывает процедуру арбитража для двух мастеров)[13].

Рисунок 3.11 – Процедура арбитажа двух мастеров