- •Мова опису апаратури ahdl

- •1. Опис комбінаційних схем

- •1.1. Шифратор

- •1.2. Дешифратор

- •1.3. Мультиплексор

- •1.4. Демультиплексор

- •1.5. Перетворювач коду

- •1.6. Компаратор

- •1.7. Суматор

- •1.8. Шинні приймачі-передавачі

- •1.9. Схеми монтажного «і» і «або»

- •2.1. Регістри

- •2.1.1. Паралельний регістр

- •2.1.2. Регістр зсуву

- •2.1.3. Регістр зсуву з паралельним завантаженням даних

- •2.1.4. Універсальний регістр

- •2.1.5. Циклічний регістр зсуву

- •Часть 2. Практическое использование языка ahdl. М. 2005.- 34 с.

- •1. Опис комбінаційних схем……………………………… 3

- •1.1. Шифратор ………………………………………………………………. 3

1.9. Схеми монтажного «і» і «або»

Нижче наведений приклад текстового опису схеми монтажного (wire AND) і монтажного «АБО» (wire OR).

SUBDESIGN WIRE_

(

a, b, c : INPUT;

SELECT_a, SELECT_b, SELECT_c : INPUT;

WIRE_OR, WIRE_AND : OUTPUT;

)

BEGIN

DEFAULTS

WIRE_AND = VCC;

END DEFAULTS;

IF SELECT_a THEN

WIRE_OR = a;

WIRE_AND = a;

END IF;

IF SELECT_b THEN

WIRE_OR = b;

WIRE_AND = b;

END IF;

IF SELECT_c THEN

WIRE_OR = c;

WIRE_AND = c;

END IF;

END;

Монтажні схеми «І» і «АБО» реалізуються в тому випадку, коли змінній (лінії зв'язку), або виходу проекту привласнюється кілька значень одночасно.

В даному текстовому описі виходам WIRE_0R і WIRE_AND при SELECT_A = VCC, SELECT_B = VCC, SELECT_C = VCC одночасно присвоюються три значення: а, b, с.

Тип монтажної схеми («І», «АБО»), що реалізується задається базовим логічним рівнем відповідної змінної або виводу. Вивід WIRE_OR неявно довизначений логічним нулем (GND). Тому буде реалізована схема монтажного «АБО». Вивід WIRE_AND за допомогою оператора DEFAULT явно довизначений логічною одиницею (VCC) і, отже, буде реалізована схема монтажного «І».

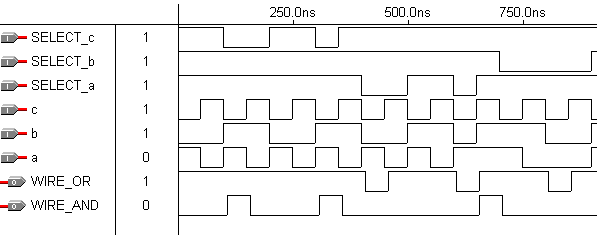

Результати моделювання модуля WIRE_ наведено на рис. 23.

Рис. 23.

Нижче представлені рівняння, синтезовані компілятором при реалізації модуля WIRE_ на НВІС сімейства МАХ7000 (логічні рівняння взяті з розділу EQUATIONS файлу звіту):

a : INPUT;

b : INPUT;

c : INPUT;

SELECT_a : INPUT;

SELECT_b : INPUT;

SELECT_c : INPUT;

-- Node name is 'WIRE_AND'

-- Equation name is 'WIRE_AND', location is LC115, type is output.

WIRE_AND = LCELL( _EQ001 $ VCC);

_EQ001 = !a & SELECT_a

# !b & SELECT_b

# !c & SELECT_c;

-- Node name is 'WIRE_OR'

-- Equation name is 'WIRE_OR', location is LC117, type is output.

WIRE_OR = LCELL( _EQ002 $ GND);

_EQ002 = a & SELECT_a

# b & SELECT_b

# c & SELECT_c;

З наведеного тексту випливає, що компілятор пакета MAX+plus II реалізує схеми монтажного «І» і «АБО» як звичайні багатовходові схеми «І» і «АБО», тобто - на логічних елементах (макроосередках) НВІС ПЛ..

2.

ОПИС ТРИГЕРНИХ

СХЕМ

2.

ОПИС ТРИГЕРНИХ

СХЕМ

Тригерна (послідовнісна) схема - схема з елементом пам'яті (тригером), синхронізованим фронтом (синхронний тригер) або рівнем тактового сигналу (тригер-засувка).

2.1. Регістри

Регістр - пристрій, що забезпечує прийом, зберігання, передачу й перетворення форми подання (паралельних, послідовна) даних.

За способом прийому й передачі даних розрізняють:

Паралельний регістр - регістр із паралельними завантаженням і виходом даних.

Регістр зсуву - регістр із послідовними завантаженням і виходом даних.

Регістр зсуву, з паралельним завантаженням даних.

Регістр зсуву, з паралельним виходом даних.

2.1.1. Паралельний регістр

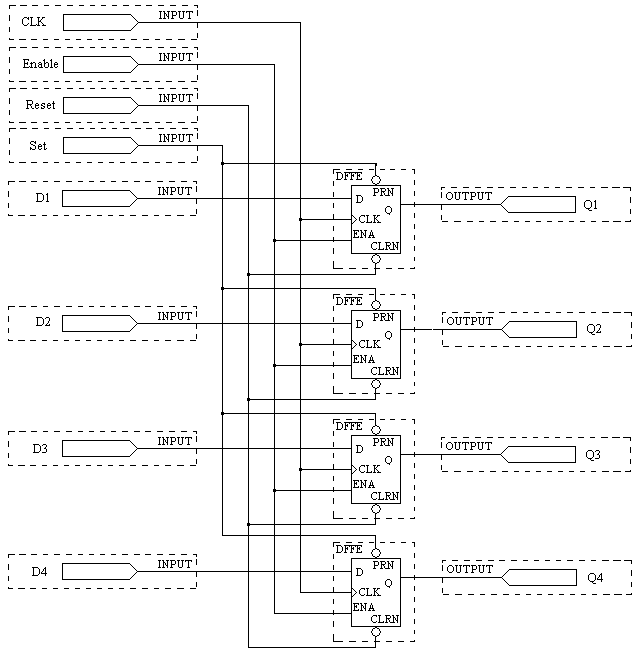

На рис. 24 представлена структурна схема чотирозрядного паралельного регістра.

Рис. 24.

Виводи регістра:

CLK - вхід тактового сигналу;

Enable - вхід дозволу завантаження даних;

Set - вхід асинхронної установки регістра;

Reset - вхід асинхронного скидання регістра;

D[4..1] - чотирирозрядний вхід даних;

Q[4..1] - чотирирозрядний вихід даних.

Текстовий опис регістра:

SUBDESIGN RG_4

(

D[3..0], CLK, ENABLE : INPUT = GND;

RESET, SET : INPUT = VCC;

Q[3..0] : OUTPUT;

)

VARIABLE

FF[3..0] : DFFE;

BEGIN

FF[].(CLK, CLRN, PRN, ENA) = (CLK, RESET, SET, ENABLE);

FF[].D = D[];

Q[] = FF[].Q;

END;

У наведеному описі до примітива (DFFE) звертаються як до змінної: оголошені чотири змінні FF[3..0], кожна з яких позначає DFFE тригер із входом дозволу роботи.

Базове значення вхідного сигналу, призначене для входів D CLK, Enable - логічний нуль, а для входів Reset, Set - логічна одиниця. Тому при використанні модуля RG_4 як компоненти кожного з його входів може бути залишений непідключеним, і на нього автоматично буде подане відповідне базове значення.

Відзначимо, що входи асинхронної установки (Set) і скидання (Reset) мають більш високий пріоритет у порівнянні із входом дозволу роботи (Enable). Так, якщо на вході Reset є присутнім сигнал логічного нуля, то кожний розряд регістра буде асинхронно скинутий у нуль незалежно від значення сигналу на вході Enable.

Розглянемо ще один можливий варіант опису розглянутого паралельного регістра. У цьому випадку для задання алгоритму роботи пристрою використаний оператор FOR i IN 0 TO 3 GENERATE

SUBDESIGN RG_4_1

(

D[3..0], CLK, ENABLE : INPUT = GND;

RESET, SET : INPUT = VCC;

Q[3..0] : OUTPUT;

)

BEGIN

FOR i IN 0 TO 3 GENERATE

Q[i] = DFFE(.CLK=CLK, .D=D[i], .ENA=ENABLE, .CLRN=RESET, .PRN=SET);

END GENERATE;

END;

Цей опис повністю ідентичний вищенаведеному.

Нижче наведено параметризований опис WIDTH-розрядного паралельного регістра із входами: асинхронної установки (Set), асинхронного скидання (Reset), дозволу завантаження даних (Enable).

PARAMETERS (WIDTH = 7);

ASSERT (WIDTH >0)

REPORT "Value of WIDTH parameter must be greater then % "WIDTH

SEVERITY ERROR;

SUBDESIGN RG_WIDTH

(

D[WIDTH..0] : INPUT = GND;

SET, RESET, ENABLE : INPUT = VCC;

CLK : INPUT;

Q[WIDTH..0] : OUTPUT;

)

VARIABLE

FF[WIDTH..0] : DFFE;

BEGIN

ASSERT USED(CLK)

REPORT "Input CKL must be used"

SEVERITY EROR;

FF[].(CLK, CLRN, PRN) = (CLK, RESET, SET);

FF[].D = D[];

Q[] = FF[].Q;

FF[].ENA = ENABLE;

END;

При використанні даного модуля як компонента (тобто при створенні модуля більш високого рівня в ієрархії описів) деякі коди (або цілеспрямовано, або в результаті помилки) можуть бути залишені непідключеними.

Оскільки для входу CLK не задане базове значення вхідного сигналу, компілятор у випадку, якщо цей вхід залишиться непідключеним, сформує повідомлення про помилку:

Error: Input pinstub/port 'clk' is unconnected and has no default value

Якщо ж для входу CLK буде задане базове значення вхідного сигналу (наприклад — GND), то для контролю підключення даного входу можна використати оператор ASSERT і вбудовану в пакет функцію - USED (як показано у вищенаведеній програмі).

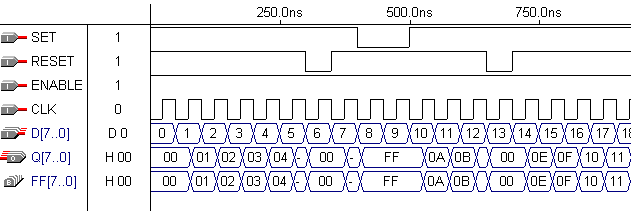

Результати моделювання описаного регістра при WIDTH=7 і використання всіх його входів наведено на рис. 25.

Рис. 25.

Розглянемо ще один варіант опису параметризованого паралельного регістра, що використовує оператор FOR i IN 0 TO WIDTH GENERATE

PARAMETERS (WIDTH = 7);

ASSERT (WIDTH >0)

REPORT "Value of WIDTH parameter must be greater then % "WIDTH

SEVERITY ERROR;

SUBDESIGN RG_WIDTH_1

(

D[WIDTH..0] : INPUT = GND;

SET, RESET, ENABLE : INPUT = VCC;

CLK : INPUT;

Q[WIDTH..0] : OUTPUT;

)

BEGIN

ASSERT USED(CLK)

REPORT "Input CKL must be used"

SEVERITY EROR;

FOR i IN 0 TO WIDTH GENERATE

Q[i] = DFFE (.CLK=CLK, .D=D[i], .ENA=ENABLE, .CLRN= RESET, .PRN=SET);

END GENERATE;

END;

Це опис аналогічний вищенаведеному.

Нижче наведено параметризований опис WIDTH-розрядного паралельного регістра із входами: синхронної установки (Sset), синхронного скидання (SReset) і дозволу роботи (Enable).

PARAMETERS (WIDTH = 7);

ASSERT (WIDTH >0)

REPORT "Value of WIDTH parameter must be greater then % "WIDTH

SEVERITY ERROR;

SUBDESIGN RG_WIDTH_SINHRO

(

D[WIDTH..0] : INPUT = GND;

SSET, SRESET, ENABLE : INPUT = VCC;

CLK : INPUT;

Q[WIDTH..0] : OUTPUT;

)

VARIABLE

FF[WIDTH..0] : DFFE;

BEGIN

ASSERT USED(CLK)

REPORT "Input CKL must be used"

SEVERITY EROR;

FF[].CLK = CLK;

FF[].ENA = ENABLE;

CASE (SSET, SRESET) IS

WHEN B"11" => FF[].D = D[];

WHEN B"01" => FF[].D = VCC;

WHEN B"10" => FF[].D = GND;

END CASE;

Q[] = FF[].Q;

END;

У наведеному описі активними логічними рівнями для синхронних входів скидання SRESET і установка SSET є сигнал логічного нуля.

Якщо на вхід Enable подати сигнал логічного нуля, то регістр буде здійснювати зберігання даних. Якщо ж - сигнал логічної одиниці, то логіка роботи регістра буде визначатися даними на входах SSet і SReset.

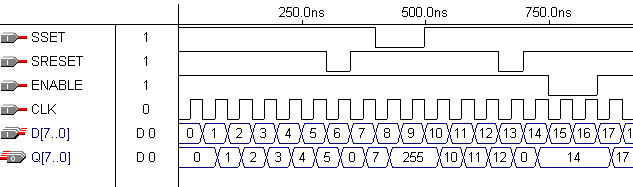

Результати моделювання регістра при WIDTH=7 наведено на рис. 26.

Рис. 26.

Відзначимо, що завантаження даних у регістр, його скидання й установка здійснюються синхронно по фронту тактового сигналу.