- •Мова опису апаратури ahdl

- •1. Опис комбінаційних схем

- •1.1. Шифратор

- •1.2. Дешифратор

- •1.3. Мультиплексор

- •1.4. Демультиплексор

- •1.5. Перетворювач коду

- •1.6. Компаратор

- •1.7. Суматор

- •1.8. Шинні приймачі-передавачі

- •1.9. Схеми монтажного «і» і «або»

- •2.1. Регістри

- •2.1.1. Паралельний регістр

- •2.1.2. Регістр зсуву

- •2.1.3. Регістр зсуву з паралельним завантаженням даних

- •2.1.4. Універсальний регістр

- •2.1.5. Циклічний регістр зсуву

- •Часть 2. Практическое использование языка ahdl. М. 2005.- 34 с.

- •1. Опис комбінаційних схем……………………………… 3

- •1.1. Шифратор ………………………………………………………………. 3

1.4. Демультиплексор

Демультиплексор - комбінаційний пристрій, що забезпечує комутацію вхідного сигналу на один із N виходів відповідно до отриманого коду адреси.

Число виходів демультиплексора зазвичай дорівнює 2n, де n — число розрядів двійкового коду адреси.

Нижче наведений приклад опису демультиплексора, що має однорозрядний інформаційний вхід IN, трирозрядний адресний вхід ADR[2..0], вхід дозволу роботи (вибору кристала) CS і восьмирозрядний вихід Q[7..0].

SUBDESIGN DMX

(

IN, ADR[2..0], CS : INPUT;

Q[7..0] : OUTPUT;

)

BEGIN

IF CS THEN

CASE ADR[] IS

WHEN 0 => Q[0] = IN;

WHEN 1 => Q[1] = IN;

WHEN 2 => Q[2] = IN;

WHEN 3 => Q[3] = IN;

WHEN 4 => Q[4] = IN;

WHEN 5 => Q[5] = IN;

WHEN 6 => Q[6] = IN;

WHEN 7 => Q[7] = IN;

END CASE;

END IF;

END;

У кожному рядку оператора CASE (тобто на кожному наборі аргументів) явно задане значення тільки одного виходу модуля. Оскільки оператор DEFAULTS не був використаний, то на інших виводах при даному наборі аргументів буде присутній сигнал логічного нуля.

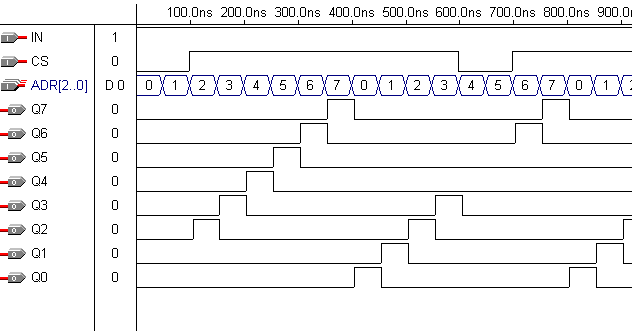

На рис. 9. наведено результати моделювання описаного вище демультиплексора.

Рис. 9.

Розглянемо параметризований опис демультиплексора, що має WIDTH+1-розрядний інформаційний вхід (IN[WIDTH..0]), трирозрядний вхід адреси (ADR[2..0]), вхід дозволу роботи (CS) і вісім WIDTH-розрядних виходів (Q[7..0][WIDTH..0]).

PARAMETERS (WIDTH = 7);

ASSERT (WIDTH != 1)

REPORT "Value of parameters WIDTH = %" WIDTH

SEVERITY INFO;

ASSERT (WIDTH > 0)

REPORT "Value of parameter WIDTH must be greater then %" WIDTH

SEVERITY ERROR;

SUBDESIGN LPM_DMX

(

IN[WIDTH..0], ADR[2..0], CS : INPUT;

Q[7..0][WIDTH..0] : OUTPUT;

)

BEGIN

IF CS THEN

CASE ADR[] IS

WHEN 0 => Q[0][WIDTH..0] = IN[WIDTH..0];

WHEN 1 => Q[1][WIDTH..0] = IN[WIDTH..0];

WHEN 2 => Q[2][WIDTH..0] = IN[WIDTH..0];

WHEN 3 => Q[3][WIDTH..0] = IN[WIDTH..0];

WHEN 4 => Q[4][WIDTH..0] = IN[WIDTH..0];

WHEN 5 => Q[5][WIDTH..0] = IN[WIDTH..0];

WHEN 6 => Q[6][WIDTH..0] = IN[WIDTH..0];

WHEN 7 => Q[7][WIDTH..0] = IN[WIDTH..0];

END CASE;

END IF;

END;

У наведеному описі використана двовимірна група ОUT[7..O][WIDTH..0], у якій параметризований один діапазон зміни індексів (розрядність шини, що комутується).

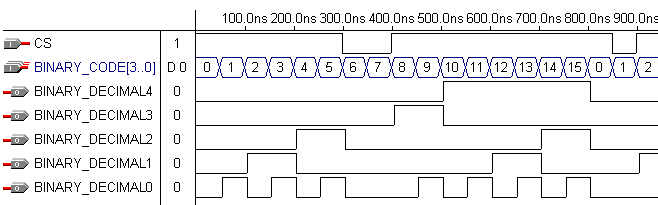

Результати моделювання параметризованого демультиплексора при WIDTH=7 наведено на рис. 10.

Рис. 10.

1.5. Перетворювач коду

Перетворювач коду - комбінаційний пристрій, призначений для зміни коду подання інформації.

Розглянемо варіант опис перетворювача чотирирозрядного двійкового коду в п’ятирозрядний двійково-десятковий:

SUBDESIGN BIN_DEC

(

CS, BINARY_CODE[3..0] : INPUT;

BINARY_DECIMAL[4..0] : OUTPUT;

)

BEGIN

IF CS == VCC THEN

IF BINARY_CODE[] <= 9 THEN

BINARY_DECIMAL[] = (0, BINARY_CODE[]);

ELSE

BINARY_DECIMAL[] = (1, BINARY_CODE[]-10);

END IF;

ELSE

BINARY_DECIMAL[] = B"00000";

END IF;

END;

У наведеному прикладі для опису алгоритму роботи перетворювача коду використаний оператор IF THEN. Цей самий алгоритм роботи пристрою можна описати й іншим способом, наприклад, з використанням оператора TABLE.

SUBDESIGN BIN_DEC

(

CS, BINARY_CODE[3..0] : INPUT;

BINARY_DECIMAL[4..0] : OUTPUT;

)

BEGIN

TABLE

BINARY_CODE[] => BINARY_DECIMAL[];

B”0000” => B”00000”;

B”0001” => B”00001”;

B”0010” => B”00010”;

B”0011” => B”00011”;

B”0100” => B”00100”;

B”0101” => B”00101”;

B”0110” => B”00110”;

B”0111” => B”00111”;

B”1000” => B”01000”;

B”1001” => B”01001”;

B”1010” => B”10000”;

B”1011” => B”10001”;

B”1100” => B”10010”;

B”1101” => B”10011”;

B”1110” => B”10100”;

B”1111” => B”10101”;

END TABLE;

END;

Обидві програми абсолютно ідентичні й при моделюванні дають однаковий результат. Їхня відмінність тільки в довжині використовуваного опису.

Рис. 11.

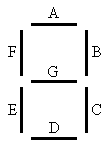

У пристроях індикації часто використаються перетворювачі двійкового й двійково-десяткового кодів у семисегментний код. На рис. 12 зображений семисегментний індикатор з позначеннями сегментів.

Рис. 12.

Нижче наведений приклад текстового опису перетворювача двійково-десяткового коду в семисегментний код.

SUBDESIGN DEC_SEGM

(

BINARY_DECIMAL[3..0], ENABLE : INPUT;

A, B, C, D, E, G, F : OUTPUT;

)

BEGIN

IF ENABLE

THEN

TABLE

BINARY_DECIMAL[] => A, B, C, D, E, F, G;

B"0000" => 1,1,1,1,1,1,0;

B"0001" => 0,1,1,0,0,0,0;

B"0010" => 1,1,0,1,1,0,1;

B"0011" => 1,1,1,1,0,0,1;

B"0100" => 0,1,1,0,0,1,1;

B"0101" => 1,0,1,1,0,1,1;

B"0110" => 1,0,1,1,1,1,1;

B"0111" => 1,1,1,0,0,0,0;

B"1000" => 1,1,1,1,1,1,1;

B"1001" => 1,1,1,1,0,1,1;

END TABLE;

END IF;

END;

Наведений перетворювач кодів має вхід дозволу роботи - (Enable). При Enable=0 (робота заборонена) значення логічних функцій А, В, С, D, E, F, G не були явно задані. Тому їм буде присвоєне значення логічного нуля.

Результати моделювання перетворювача наведено на рис. 13.

Рис. 13.