Лабы / Лабы по схемотехнике / ЛР №4 (Фомичёв)

.docМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

ОРЛОВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра: «Проектирование и технология электронных и вычислительных систем»

Отчет по лабораторной работе №4

по дисциплине «Схемотехника»

Тема: «Исследование триггеров»

Руководитель:

Рабочий А.А.

Студент группы 31-В:

Фомичёв А.С.

Орел, 2007 г.

1. Цель работы: ознакомление с работой триггеров.

2. Виды и принципы работы триггеров:

Триггерами называют устройства, имеющие два устойчивых состояния, у которых переход из одного состояния в другое происходит вследствие регенеративного процесса.

Под регенеративным процессом обычно понимают переходный процесс в электрической цепи, охваченной положительной ОС с петлевым усилением Ку > 1 в широком диапазоне частот, который характеризуется резкими изменениями токов и падений напряжений на элементах цепи.

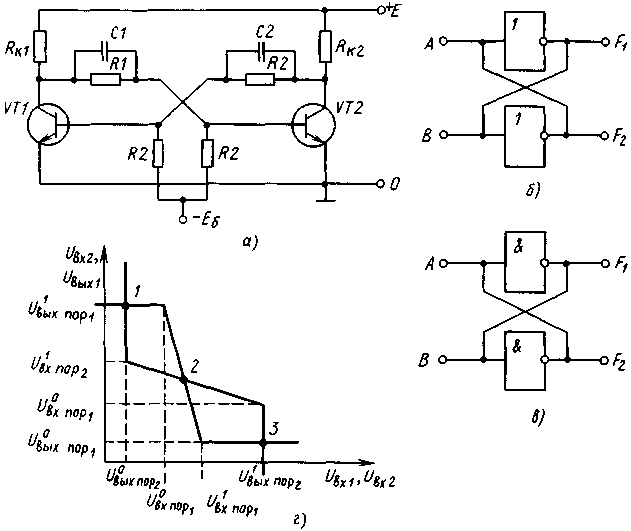

Рассмотрим принцип работы симметричного триггера на транзисторах п-р-п-типа, схема которого приведена на рис. 1, а. Триггер представляет собой два усилителя на транзисторах VT1 и VT2. Выход каждого усилителя соединен с входом другого. Обратная связь, получаемая в результате такого соединения усилителей, является положительной.

В принципе в приведенной схеме возможно состояние электрического равновесия, при котором оба транзистора VT1 и VT2 открыты и находятся в активной области. В этом случае токи iK 1 и iK 2 равны между собой и падения напряжений на элементах схемы не изменяются в течение времени. Однако такое состояние является неустойчивым и любые флуктуации тока или напряжения приведут к лавинообразному процессу нарастания тока одного и убывания тока другого транзисторов.

Рис. 1. Схема симметричного триггера (а) и представление его в виде двух логических элементов (б, в); переключательные характеристики логических элементов триггера (г)

Если параметры схемы выбраны так, что когда один из транзисторов закрыт, другой открыт и насыщен, то такой триггер называют насыщенным. Если открытый транзистор находится на границе активной области и не входит в режим насыщения, то триггер называется ненасыщенным.

В одном из устойчивых состояний триггер может находиться как угодно долго до момента, пока не поступит сигнал от источника внешнего управляющего напряжения. Пусть оно вводится в цепь базы запертого коллектора VT2. Как только напряжение управляющего сигнала достигнет уровня, при котором VT2 откроется, появится коллекторный ток 1К 2 и уменьшится ток базы 1Б 1. Транзистор VT1 выйдет в активную область и будет восстановлена петля положительной обратной связи. Возникающий при этом регенеративный процесс приведет к опрокидыванию триггера. В итоге транзистор VT1 закроется, а транзистор VT2 откроется и окажется в области насыщения. Триггер перейдет во второе устойчивое состояние. В процессе опрокидывания триггера на коллекторах транзисторов формируются положительные и отрицательные перепады токов и напряжений.

Конденсаторы C1 и С2 включены для ускорения процесса переключения и носят название ускоряющих. Они также выполняют роль элементов памяти о предыдущем состоянии триггера и обеспечивают четкость его переключения в новое состояние.

Работу триггера можно рассматривать более укрупненно, представляя каждый транзистор с соответствующими соединениями как логический элемент, выполняющий в зависимости от типа логики функцию И-НЕ или ИЛИ-НЕ. В этом случае выход логического элемента соединен с входом второго логического элемента и схема триггера для разных (положительной и отрицательной) логик имеет вид, показанный на рис. 1, б, в.

Основой классификации триггеров по функциональному признаку является вид логического управления, характеризующего состояние входов и выходов триггера в момент времени до tn и после его срабатывания tn + 1. По этому признаку триггеры подразделяют на RS-; D-; Т-; JK-типы и т. д.

Примеры условного обозначения триггера приведены на рис. 2, а—ж.

Рис. 2. Примеры условных обозначений триггеров:

а — асинхронный RS-триггер; б — синхронизируемый логическим нулем RS-триггер; в — D-триггер, срабатывающий по фронту 0,1; г — JК-триггер, срабатывающий по срезу 1,0; д — двухступенчатый JК-триггер с входами раздельной установки в нулевое (R) и единичное S состояния; е — Т-триггер, срабатывающий по срезу 1,0; ж — синхронизируемый фронтом 1,0 JК-триггер с логическими элементами И на входах J и К

Рис. 3. Схемы асинхронного RS-триггера на элементах:

a - ИЛИ-НЕ; б - И-НЕ; в – ИС типа 564ТР2

Триггер RS-типа (рис. 3, а) представляет собой устройство, имеющее два информационных входа: R и S. В нем возможны два устойчивых состояния.

При R = 0 и S=1 триггер принимает состояние 1 (Q=1), а при R=1, S=0 — состояние О (Q = 0). Иногда вход S называют единичным, a R — нулевым. Для триггера RS-типа. комбинация S=1; R=1 является запрещенной, так как после такой комбинации состояние триггера будет неопределенным (X) и он может оказаться или в нуле, или в единице. Состояния RS-триггера в зависимости от входных сигналов иллюстрирует табл. 1.

Таблица 1

Примечание. Q* — исходное состояние триггера; X—неопределенное состояние.

В триггерах, показанных на рис. 3, б, в, установка в определенное их состояние осуществляется кодом логической 1 (положительная логика).

Рис. 4. Синхронизируемые RS-триггеры:

а - на ЛЭ И-НЕ; 6 - на ЛЭ ИЛИ-НЕ: в - условное обозначение синхронизируемого RS-триггера

Синхронизируемые (тактируемые) RS-триггеры имеют на входе каждого плеча схемы совпадения, первые входы которых объединены и являются входами синхронизирующих (тактирующих) импульсов. На вторые входы подают информационные сигналы. Такое включение обеспечивает поступление на входы R и S триггера информационных сигналов только во время действия потенциала импульсов синхронизации. Некоторые варианты синхронизируемых RS-триггеров показаны на рис. 4, а, б. Условное графическое обозначение синхронного триггера приведено на рис. 4, в.

Триггеры D-типа иногда называют триггерами задержки. У них имеется один информационный вход D и возможны два устойчивых состояния.

Логическое уравнение, описывающее работы D -триггера, имеет вид

Qn+l = D n.

Рис. 5. Схемы асинхронных D-триггеров (а, б); диаграммы изменений входного и выходного напряжений (в, г); условное обозначение (д)

Роль простейшего асинхронного D -триггера может выполнять схема, состоящая из двух или нескольких последовательно включенных логических элементов (рис. 5,а), в которой входной сигнал из-за задержки распространения в каждом логическом элементе сдвинут во времени относительно входного сигнала.

В состав D -триггеров, применяемых на практике, обычно входят RS -триггеры, управление которыми организовано соответствующим образом. Возможная структура такого D -триггера показана на рис. 5,б. В нем вследствие задержки распространения в логических элементах сигнал на выходе Q появляется также с определенной задержкой времени.

Выходной сигнал повторит входной сигнал с задержкой tзд р (рис. 5,в,г).

Состояние триггера в различные моменты времени можно определить из табл. 2.

Таблица 2

Варианты практической реализации синхронизируемых однотактных триггеров D-типа, выполненные на элементах И-НЕ или ИЛИ-НЕ, показаны на рис. 6, причем схема рис. 6, а тактируется сигналами логической 1, а схема рис. 6,б—сигналами логического 0. На рис. 6, в показано условное обозначение синхронизируемого D -триггера.

Рис. 6. Синхронизируемые Д-триггсры:

а - на элементах И-НЕ; б - на элемешах ИЛИ-НЕ: в - условное обозначение; г - D-триггер с дополнительным управляющим входом Е

В триггере записывается та информация, которая была на входе D до прихода импульса синхронизации.

У ряда D-триггеров также имеется дополнительный вход Е (V) разрешения приема информации (DV-тригтеры). При E=1 такие триггеры функционируют как обычные D-триггеры, а при E=0 сохраняют исходное состояние независимо от информации на входе D. Реализовать такой триггер можно путем введения в D-триггер дополнительного элемента И, включенного так, как показано на рис. 6, г.

Рис. 7. T-триггер, выполненный на основе Д-триггера (а); устранение «гонки» в T-триггере (б)

Триггер T-типа — это логическая схема с двумя устойчивыми состояниями и одним информационным входом Т, изменяющая свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал. Его часто называют триггером со счетным входом. Основным способом построения счетных триггеров является введение соответствующих обратных связей в тактируемые RS-и D-триггеры (cм. рис. 7).

Рис. 8. Схема JK-триггера (а); применение триггера для построения триггеров RS (б), D (в) и Т (г)

Триггер JK-типа часто называют универсальным. Это устройства, имеющие входы J и К, у которых нет неопределенного состояния. Если на входы J и К подаются сигналы логической единицы, то состояние JK-триггера меняется на противоположное при каждом новом приходящем импульсе. Другими словами, если входы J и К объединены между собой, то JK-тригтер работает как T-триггер. В остальных случаях он функционирует как триггер RS-типа. При этом вход J эквивалентен входу S, а К — входу R. На рис. 8., а показана структурная схема простейшего JK-триггера. При одновременной подаче на входы J и К сигнала логической единицы триггер с помощью соответствующих схем совпадений устанавливается в положение 1 или 0 в зависимости от его начального состояния (т. е. ведет себя как триггер T-типа). Если сигнал подается на вход или К, то триггер, аналогично RS-триггеру, устанавливается соответственно в состояние 1 или 0.

Триггер JK-типа универсальным называют потому, что на его основе с помощью несложных коммутационных изменений можно получить RS- и T-триггеры (рис. 8, б, в, г).

Построение двухступенчатого триггера разберем на примере схемы рис. 9, а.

Рис. 9. Схема двухступенчатого JK-триггера (а) и его условные обозначения (б, в)

НЕСИММЕТРИЧНЫЕ ТРИГГЕРЫ

Несимметричные триггеры часто называют триггерами Шмитта. По своим свойствам они существенно отличаются от симметричных триггеров, так как у них нет памяти о предыдущем состоянии. Несимметричный триггер — это регенеративное устройство, имеющее гистерезисную передаточную характеристику, у которой выходной сигнал может принимать два значения. Переход от одного уровня выходного напряжения к другому происходит скачкообразно при определенном значении входного сигнала — напряжении срабатывания. Возвращение в исходное состояние происходит при другом уровне входного сигнала — напряжении отпускания. По модулю оно всегда меньше напряжения срабатывания на величину ∆U, характеризующую ширину петли гистерезиса.

Рис. 10. Схема триггера Шмита (а), его эквивалентная схема (б), передаточная (в) и входная (г) характеристики