- •Глава 10. Основы цифровой электроники

- •10.1 Представление информации в цифровой системе

- •10.2 Составление логических функций и соответствующих им функциональных схем

- •10.3 Основные типы цифровых интегральных схем

- •10.4 Параметры цифровых ис

- •10.5 Комбинационные цифровые устройства

- •10.5.1 Мультиплексоры

- •10.5.2 Демультиплексоры и дешифраторы

- •10.5.3 Комбинационные сумматоры и схемы сравнения

- •10.6 Последовательные цифровые устройства

- •10.6.1 Триггеры

- •10.6.2 Регистры и кольцевые счётчики

- •10.6.3 Счётчики с двоичными и недвоичными коэффициентами пересчёта

- •10.6.4 Запоминающие устройства.

- •10.6.5 Цифроаналоговые преобразователи.

- •10.6.6 Аналогово-цифровые преобразователи.

- •Существует несколько подходов к классификации типов аналогово-цифровых преобразователей. Например, по методам преобразования различают следующие преобразователи:

- •Последовательного счета (развертывающие ацп);

- •Разрядного уравновешивания;

- •10.7 Тренировочные задания.

- •10.8 Тестовые задания.

- •10.9 Выводы по десятой главе

10.3 Основные типы цифровых интегральных схем

В общем случае устройства, оперирующие с двоичной (дискретной) информацией, подразделяются на два больших класса: комбинационные схемы (дискретные автоматы без памяти) и последовательные устройства (дискретные автоматы с памятью).

Комбинационные устройства характеризуются тем, что сигналы на их выходах в любой момент времени определяются сочетанием сигналов на входах и не зависят от предыдущих состояний входных сигналов и элементов схемы.

Примерами таких схем служат логические схемы, шифраторы, дешифраторы, комбинационные арифметико-логические схемы и т.д. Одним из основных признаков этих схем является отсутствие цепей обратной связи.

Последовательные устройства обладают памятью и чтобы предсказать состояние выходных сигналов надо знать не только состояние входных сигналов, но и состояние элементов памяти устройства. Последовательные устройства организуются путем соответствующих соединений комбинационных схем с цепями обратных связей. К этому классу относятся триггеры, счетчики, запоминающие устройства и т.д.

Цифровые интегральные схемы (ИС) могут строиться по разному, но базовые элементы, как правило, выполняют функции И-НЕ или ИЛИ-НЕ. К наиболее распространенным базовым типам ИС относят транзисторно-транзисторные логические схемы (ТТЛ), быстродействующие транзисторные схемы с эмиттерными связями (ЭСЛ), логические схемы на комплиментарных МОП транзисторах (КМОП).

Элементы транзисторно-транзисторной логики строят на основе многоэмиттерного транзистора, реализующего функции И, и транзисторного инвертора. На рис 10.6 приведена схема типового элемента ТТЛ серии 155.

Схема содержит три каскада: входной (многоэмиттерный транзистор VT1 с резистором R1, реализующий функцию И); фазорасщепительный (транзистор VТ2, резистор R2, узел VТ3, R3 и R4); выходной (транзисторы VT4, VT5, диод VD4). Диоды на входе VD1VD3 непосредственно на работу схемы не влияют. Они находятся в закрытом состоянии. Однако, если на входах микросхемы появляются отрицательные потенциалы (например, при возбуждении операционных усилителей, работающих на вход схемы ТТЛ), соответствующие диоды открываются и удерживают входное напряжение на уровне - 0,7 В. Узел VT3, R3, R4 служит для улучшения передающей характеристики и повышения помехоустойчивости: в первом приближении при рассмотрении принципов работы элемента ТТЛ узел VT3, R3, R4 можно рассматривать как резистор 1Ом.

Рис.10.6. Схема типового элемента ТТЛ

Если на один или несколько входов многоэмиттерного транзистора подать потенциал близкий к нулю или соединить их с общей шиной, соответствующий эмиттерный переход транзистора VT1 открывается. Тогда напряжения на базе открытого транзистора VT1 (0,7 В) недостаточно для отпирания транзистора VT2. В результате транзистор VТ2 – закрыт, а ток, протекающий через резистор R2, открывает транзистор VT4 и диод VD4, транзистор VT5 из-за недостатка отпирающего тока оказывается закрытым. Через резистор R3, открытые транзистор VT4 и диод VD4 к выходу F подключается напряжение питания, создавая потенциал логической единицы на выходе ИС.

Если на всех входах х1х3 действует напряжение высокого уровня, переходы база-эмиттер VT1 закрываются, а переход база-коллектор открывается. Через резистор R1 в базу транзистора VT2 течет открывающий ток. Ответвление тока базы транзистора VT4 через открытый транзистор VT2 приводит к запиранию транзистора VT4 и к отпиранию транзистора VT5, что в свою очередь создает на выходе ИС потенциал близкий к нулю. То есть схема представленная на рис.10.6 реализует логическую функцию 3 И-НЕ.

Диод VD4 обеспечивает более надежное запирание транзистора VT4. В рассмотренной схеме открытые транзисторы работают в режиме насыщения, и в процессе запирания требуется время для рассасывания не основных носителей зарядов, что снижает быстродействие схем. Одним из вариантов повышения быстродействия схем ТТЛ является применение диодов Шотки (схемы ТТЛШ), в которых базо-эммиттерные переходы транзисторов шунтированы диодами Шотки, в которых накопления не основных носителей не происходит.

Номенклатура микросхем ТТЛ к настоящему времени развита достаточно хорошо от простых логических элементов до запоминающих и арифметико-логических устройств. Основные электрические параметры для всех серий ТТЛ согласованы, что позволяет соединять друг с другом различные серии микросхем.

Логические схемы на комплиментарных МОП транзисторах (КМОП) основаны на использовании последовательно включенных МОП транзисторов разных типов проводимости. На рис.10.7 показан пример логической схемы ИЛИ-НЕ на КМОП транзисторах.

Рис.10.7. Типовая логическая схема на КМОП транзисторах

В схемах на КМОП-структурах, транзисторы включаются друг на друга без дополнительных элементов, поскольку входные сопротивления транзисторов достаточно велики (1012-1014 Ом). В этой схеме подача низкого уровня входного напряжения (UВХ 0) закрывает соответствующий транзистор нижней части схемы и открывает транзисторы верхней части схемы. Подача высокого уровня напряжения (UВХ UП) оказывает обратное действие. Таким образом, на выходе схемы формируется потенциал логической единицы в том случае, если на все входы схемы будут поданы потенциалы низких уровней, то есть когда все транзисторы верхней группы открыты, а нижней закрыты.

Параметры микросхем КМОП-структуры близки к идеальным: в статическом режиме они практически не потребляют мощности, имеют очень большое входное и малое выходное сопротивления, высокую помехозащищенность, большую нагрузочную способность. Комплиментарные структуры допускают высокую плотность размещения элементов, что позволяет строить большие и сверхбольшие интегральные схемы (БИС и СБИС). Эти микросхемы работают в широком диапазоне питающих напряжений от 3 до 15 В, что позволяет устойчиво работать с различными питающими напряжениями и сопрягать их по входам и выходам с элементами других серий и операционными усилителями.

Основной недостаток серийных микросхем – достаточно низкое быстродействие. Высокое входное сопротивление КМОП-структур создает некоторые трудности при работе с ними. Дело в том, что напряжение пробоя изоляционного слоя ориентировочно лежит в интервале 30-50 В, поэтому при перевозе и монтаже таких ИС необходимо принимать специальные меры предосторожности. В частности монтажник и все монтажные инструменты должны заземляться.

При проектировании цифровых устройств иногда возникает необходимость подключения выходов нескольких микросхем к одной нагрузке. Одним из способов объединения выходов является использование в выходных каскадах микросхем транзисторов, один из выходов которых (коллектор, эмиттер, сток, исток) никуда не подключен. Такой вывод называют открытым. Микросхемы этого типа используют и в тех ситуациях, когда к выходу ИС необходимо подключать нагрузки различных типов работающих, возможно, от другого источника питания (индикаторные лампочки, маломощные релейные схемы и т.д.).

На рис. 10.8 приведен вариант ТТЛ реализации схемы с открытым коллектором.

Рис.10.8. Элемент ТТЛ с открытым коллектором

Из схемы рис.10.8 видно, что сама по себе схема работать не будет, поскольку выходной транзистор VT3 не имеет питающего напряжения. Для обеспечения ее работы нужно между выходным и питающим напряжением ввести сопротивление нагрузки RН.

На рис.10.9 показаны варианты подключения схем с открытым коллектором к внешним нагрузкам, питающимся от одного источника напряжения с ИС и от отдельных источников.

Рис.10.9. Варианты подключения схем с открытым коллектором.

Объединение схем по выходу с открытым коллектором принято называть монтажной (проводной) логикой (рис. 10.10).

Рис.10.10. Вариант реализации монтажной логики

При таком соединении, если на выходе хотя бы одного элемента появится потенциал низкого уровня, то этот потенциал окажется на входе всей объединенной системы. Чтобы обеспечить потенциал высокого уровня для всей системы необходимо иметь логические единицы на выходах всех объединяемых элементов, то есть такое объединение схем через общую нагрузку реализует логическую функцию вида F = y1y2…yn.

Для

обеспечения требуемого запаса

помехоустойчивости ИС с открытым

коллектором должны обеспечивать пределы

изменения выходных напряжений:

![]() .

Выполнение этих условий зависит от

величины RН,

числа объединяемых элементов, числа

элементов, подключаемых к объединенному

выходу и др. В этих условиях величина

RН

должна выбираться из двойного неравенства

.

Выполнение этих условий зависит от

величины RН,

числа объединяемых элементов, числа

элементов, подключаемых к объединенному

выходу и др. В этих условиях величина

RН

должна выбираться из двойного неравенства

![]() .

СопротивлениеRНМАКС

определяют из условия обеспечения

номинальной величины U1вых=2,4

В по формуле:

.

СопротивлениеRНМАКС

определяют из условия обеспечения

номинальной величины U1вых=2,4

В по формуле:

,

,

где Кобвых – число объединенных выходов, Кобвх – число подключаемых входов, I1вых – ток утечки на выходе (ток, протекающий через выход микросхемы при ее нахождении в состоянии «1»). Минимальное сопротивление определяется выражением:

,

,

где I0вых – максимальный допустимый выходной ток логического нуля одного элемента. Параметры токов I1вых, I0вых, I0вх, I1вх являются паспортными данными на ИС.

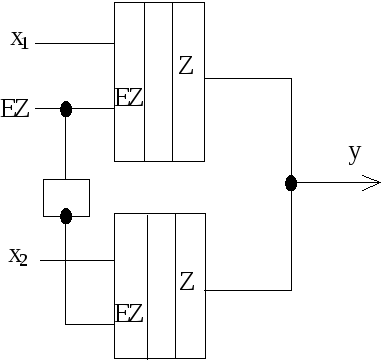

Устройства, оперирующие с дискретной информацией, при высоком уровне выходного напряжения имеют малое сопротивление между выводом «выход» и шиной питания, а при низком уровне – малое сопротивление между выводом «выход» и общей шиной. В обоих случаях выходы ИС воздействуют на окружающие их электронные элементы, что в ряде случаев не всегда приемлемо. Поэтому имеется класс ИС которые имеют так называемое управляемое третье состояние, при котором оконечные транзисторы ИС бывают заперты, что равносильно отключению микросхемы от нагрузки. Перевод в высокоимпедансное состояние Z осуществляется по специальному входу ЕZ. С тремя состояниями выхода выпускаются микросхемы различного функционального назначения, как комбинационного, так и последовательного типов. На рис.10.11 приведен пример работы двух элементов с третьим состоянием на общую нагрузку.

Рис.10.11. Пример работы элементов с третьим состоянием на общую нагрузку.

В этом примере при подаче сигнала EZ высокого уровня на вход EZ выход микросхемы переводится в высокоимпедансное (третье) состояние и перестает влиять на выходной сигнал У. Тогда работа приведенной схемы может быть определена выражением:

![]() .

.

На рис.10.12 приведен пример организации двунаправленной передачи данных с помощью ИС с третьим состоянием.

Рис.10.12. Организация двунаправленной передачи данных.