- •Базовая классификация Тип канала

- •Тип проводимости

- •Особые случаи

- •Пример триггера (d, rs)

- •Классификация сумматоров в зависимости от формы представления информации различают сумматоры аналоговые и цифровые.[1] По способу реализации

- •По способу организации переноса

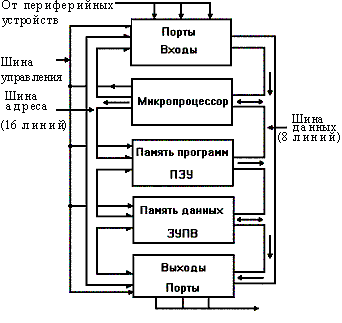

- •Структура типового микропроцессора

- •Разработка систем-на-кристалле

- •Технологии проектирования и изготовления специализированных имс

- •Внутренняя структура операционных усилителей

- •Классификация оу По типу элементной базы

- •По области применения

- •Аналоговые атсэ

- •Использование Механическое воздействие

- •Гальваническая развязка

- •Оптопары

- •Шумы транзисторной оптопары

- •Типы оптопар для гальванической развязки

- •Свойства и характеристики оптореле

- •Типы оптореле

- •Неэлектрическая передача

Классификация сумматоров в зависимости от формы представления информации различают сумматоры аналоговые и цифровые.[1] По способу реализации

механические

электромеханические

электронные

пневматические

По способу организации переноса

С последовательным переносом;

С параллельным переносом;

С условным переносом;

С групповым переносом.

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS. Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы - ИД.

Схема демультиплексора "1 на 3" с управлением от трёхбитного одноединичного трита

Автоматы с памятью. Принципы построения

Термин «автомат», как правило, используется в двух аспектах. С одной стороны, автомат - это устройство, выполняющее некоторые функции без непосредственного участия человека. С другой стороны, термин «автомат» обозначает математическую модель реальных технических автоматов, т.е. представляется как «черный ящик», имеющий конечное число входов и выходов и некоторое множество внутренних состояний, которые он может изменять мгновенно. Устройства, служащие для преобразования дискретной информации, называются дискретными (цифровыми) автоматами. Их делят на синхронные и асинхронные. В синхронных автоматах моменты времени, в которые оказывается возможным изменение состояния автомата, определяются специальным устройством – генератором синхронизирующих импульсов. Соседние моменты времени оказываются при этом обычно разделенными равными временными промежутками. Автомат называется конечным, если множество его внутренних состояний и множество значений входных сигналов – конечные множества. Конечные автоматы разделяют на автоматы без памяти и автоматы с памятью. Автоматом с памятью называют автомат, описываемый функциями переходов и выходов, оператор которого является оператором с памятью. Выходные слова автомата с памятью зависят не только от входных слов, но и от последовательности их поступления. Автомат с памятью имеет множество внутренних состояний, в которое он переходит под воздействием слов входного алфавита. Наличие множества внутренних состояний придает автомату способность запоминания входной информации, поступившей на вход автомата в прошлом.

Любой абстрактный автомат задается совокупностью из 6 объектов:

A=(X, Y, Q, q0, δ, λ )

где Х – конечное множество входных сигналов, называемое входным алфавитом автомата;

Y – конечное множество выходных сигналов, называемое выходным алфавитом автомата;

Q – произвольное множество, называемое множеством состояний автомата;

q0 – элемент из множества Q, называемый начальным состоянием автомата;

δ(q, x), λ(q, x) - две функции, задающие однозначные отображения множества пар (q, x), где q∈Q и x∈X, в множества Q и Х. Функция δ(q, x) называется функцией переходов автомата, а функция λ(q, x) – функцией выходов, либо сдвинутой функцией выходов.

Автомат, заданный функцией выходов, называется автоматом первого рода, автомат, заданный сдвинутой функцией выходов, – автоматом второго рода.

В зависимости от вида функции выходов автоматы с памятью делятся на автоматы Мили и автоматы Мура.

Автоматами Мура называют такие автоматы, у которых выходной сигнал Y(t) не зависит явно от входного сигнала X(t) , а определяется лишь внутренним состоянием автомата в момент времени t. Автомат Мура задается уравнениями:

В данной системе уравнений первая строка есть функция перехода, вторая – функция выхода.

В автомате Мили выходной сигнал в момент времени t, зависит как от внутреннего состояния автомата в момент t, так и от входного сигнала в момент времени t.

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной

параметр счётчика — модуль счёта —

максимальное число единичных сигналов,

которое может быть сосчитано счётчиком.

Счётчики обозначают через СТ (от англ.

counter).

4-х битный синхронный последовательный счётчик со сквозным ускоренным переносом использующий JK-триггеры

Двухразрядный двоичный асинхронный суммирующий счётчик с последовательной организацией переноса на JK-триггерах.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

Классификация/ Триггеры подразделяются на две большие группы — динамические и статические. Названы они так по способу представления выходной информации.

Динамический триггер представляет собой управляемый генератор, одно из состояний которого (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое (нулевое) — отсутствием выходных импульсов. Смена состояний производится внешними импульсами (рис. 3). Динамические триггеры в настоящее время используются редко.

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном двухинверторном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей реализации (2х2ИЛИНЕ) показаны на рис. 4.

Основной и наиболее общий классификационный признак — функциональный — позволяет систематизировать статические симметричные триггеры по способу организации логических связей между входами и выходами триггера в определённые дискретные моменты времени до и после появления входных сигналов. По этой классификации триггеры характеризуются числом логических входов и их функциональным назначением (рис. 5).

Вторая классификационная схема, независимая от функциональной, характеризует триггеры по способу ввода информации и оценивает их по времени обновления выходной информации относительно момента смены информации на входах (рис. 6).

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим и с динамическим управлением по входу синхронизации С.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Одноступенчатые триггеры (latch, защёлки) состоят из одной ступени представляющей собой элемент памяти и схему управления, бывают, как правило, со статическим управлением. Одноступенчатые триггеры с динамическим управлением применяются в первой ступени двухступенчатых триггеров с динамическим управлением. Одноступенчатый триггер на УГО обозначают одной буквой - Т.

Двухступенчатые триггеры (flip-flop, шлёпающие) делятся на триггеры со статическим управлением и триггеры с динамическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатый триггер на УГО обозначают двумя буквами - ТТ.

Триггеры со сложной логикой бывают также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют и асинхронные. Такой триггер изображён на рис. 1, верхний (S) и нижний (R) входные сигналы являются асинхронными.

Триггерные схемы классифицируют также по следующим признакам:

числу целочисленных устойчивых состояний (основанию системы счисления) (обычно устойчивых состояний два, реже — больше, см. двоичный триггер, троичный триггер, четверичный триггер[8], …, десятичный триггер, …, n-ичный триггер, …);

числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах[9], …, N-уровней в N-уровневых элементах, … ;

по способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые.

Посоставу логических элементов (триггеры на элементах И-НЕ, ИЛИ-НЕ и др.).

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

4-х разрядный сдвиговый регистр, преобразователь последовательного кода в параллельный и обратно

ПЗУ

Микросхемы ПЗУ (Постоянное Запоминающее Устройство, ROM — Read-Only Memory — память, доступная только для чтения) представляют собой однократно программируемое устройство памяти, предназначенное для чтения информации (энергонезависимое).

Различают несколько типов ПЗУ:

• ROM (Read-Only Memory, Постоянное Запоминающее Устройство, ПЗУ). Строятся на мультиплексорах или по масочной структуре (см. ниже). Программируются на заводе при производстве. Репрограммирование невозможно.

• PROM (Programmable ROM, Программируемое ПЗУ, ППЗУ). В качестве элементов программирования используются специальные перемычки. Программирование заключается в разрушении или образовании перемычки. Также является однократным действием, однако, в отличие от ROM, его можно осуществить даже в домашних условиях.

• EPROM (Erasable PROM, Стираемое ППЗУ, СППЗУ). Исторически явилось первым репрограммируемым ПЗУ. Технология основана на применении транзисторов с плавающим затвором. ПЗУ на основе EPROM требуют стирания старой конфигурации под воздействием ультрафиолетового (УФ) излучения с извлечением ИМС из устройств и имеют ограничение числа циклов программировании из-за деградации свойств материалов под воздействием УФ излучения.

• EEPROM

(Electrically Erasable PROM, Электрически

Стираемое

ППЗУ,

ЭС-ППЗУ).

ППЗУ,

очищаемое электрическими сигналами.

Для обновления не требует извлечения

микросхемы из устройства и допускает

достаточно большое число циклов стирания.

• FLASH (флэш-память). Технологически аналогична EEPROM, однако в ней используется блочный доступ к сохраняемым данным.

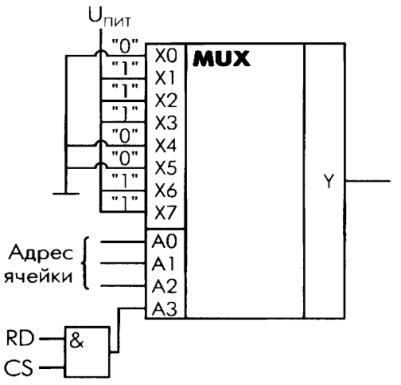

ROM. Очень часто в различных применениях требуется хранение информации, которая не изменяется в процессе эксплуатации устройства. Это такая информация, как программы в микроконтроллерах, начальные загрузчики и BIOS в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах. Практически всегда эта информация не требуется одновременно, поэтому простейшие устройства для запоминания постоянной информации можно построить на мультиплексорах (рис. 1).

В этой схеме построено постоянное запоминающее устройство на восемь одноразрядных ячеек. Запоминание конкретного бита в одноразрядную ячейку производится запайкой провода к источнику питания (запись единицы) или запайкой провода к корпусу (запись нуля).

Чтобы увеличить разрядность ячейки памяти ПЗУ, эти микросхемы можно соединять параллельно (выходы и записанная информация, естественно, остаются независимыми). Схема параллельного соединения одноразрядных ПЗУ приведена на рис. 2.

В

реальных ПЗУ запись информации

производится при помощи последней

операции производства микросхемы —

металлизации. Металлизация выполняется

при помощи маски, поэтому такие ПЗУ

получили название масочных ПЗУ. Еще

одно отличие реальных микросхем от

упрощенной модели, приведенной выше, —

это использование кроме мультиплексора

еще и демультиплексора. Такое решение

позволяет превратить одномерную

запоминающую структуру в многомерную

и тем самым существенно сократить объем

схемы дешифратора, необходимого для

работы схемы ПЗУ. Программирование ПЗУ

производится на заводе – изготовителе.

PROM. Также разработаны программируемые ПЗУ. В этих микросхемах постоянное соединение проводников в запоминающей матрице заменяется плавкими перемычками, изготовленными из поликристаллического кремния. При производстве микросхемы изготавливаются все перемычки, что эквивалентно записи во все ячейки памяти логических единиц. В процессе программирования на выводы питания и выходы микросхемы подается повышенное питание. При этом если на выход микросхемы подается напряжение питания (логическая единица), то через перемычку ток протекать не будет и перемычка останется неповрежденной. Если же на выход микросхемы подать низкий уровень напряжения (присоединить к корпусу), то через перемычку будет протекать ток, который испарит эту перемычку, и при последующем считывании информации из этой ячейки будет считываться логический ноль. Программирование производится при помощи специального программатора.

Возможно также применение другой технологии создания PROM, когда перемычка образована трехслойным диэлектриком с чередованием слоев «оксид-нитрид-оксид». Программирующий импульс напряжения пробивает перемычку и создает проводящий канал между электродами. Величина тока, создаваемого импульсами программирования, влияет на диаметр проводящего канала, что позволяет управлять параметрами проводящей перемычки.

ОЗУ: RAM, FIFO, LIFO, видеопамять, кэш.

Микросхемы ОЗУ (Оперативное Запоминающее Устройство, RAM — Random Access Memory — память с произвольным доступом) представляют собой устройство памяти, предназначенное для чтения и записи информации. Обычно ОЗУ является энергозависимым, т.е. теряет информацию при отключении питания.

Совокупность

элементов памяти (ЭП) в накопителе, в

котором размещается слово, называют

ячейкой памяти (ЯП). Каждая ЯП имеет свой

адрес, и для обращения к ней на адресные

входы микросхемы подается код адреса

этой ЯП. Ячейки памяти могут быть

объединены в запоминающую матрицу, и

тогда код адреса состоит из кода столбца

и кода строки. Микросхемы ОЗУ по типу

ЭП разделяют на динамические и статические.

Статическое ОЗУ (Static RAM — SRAM – кэш память, на триггерах) обеспечивает хранение записанной информации до тех пор, пока на микросхему подается питание. Структура SRAM требует 4-6 транзисторов для хранения одного бита (в качестве запоминающей ячейки используется параллельный регистр). В микросхемах ОЗУ присутствуют две операции: операция записи и чтения. Для записи и чтения информации можно использовать различные шины данных (как это делается в сигнальных процессорах, но чаще используется одна и та же шина данных. Это позволяет экономить выводы микросхем, подключаемых к этой шине и легко осуществлять коммутацию сигналов между различными устройствами. Статическое ОЗУ используется, как правило, для построения кэш-памяти. Пример схемы статического ОЗУ приведен на рис. 1. Здесь вход и выход микросхемы объединены при помощи шинного формирователя.

Для

построения ОЗУ большого объема применяют

динамическое

ОЗУ

(Dynamic RAM — использующее для запоминания

бита состояние

электрического конденсатора

(«заряжен»/«не заряжен»), сформированного

внутри кристалла. Для управления ее

зарядом и разрядом применяется электронный

ключ (рис 2). Заряд на емкости с течением

времени уменьшается, поэтому его

необходимо подзаряжать (регенерировать)

с периодом приблизительно 10 мс. Регенерация

заключается в считывании заряда

конденсатора и восстановлении этого

состояния посредством перезаписи

информации. Она требует дополнительного

циклического обращения к памяти, что

снижает пропускную способность и

усложняет устройство управления.

Для регенерации первоначального напряжения, хранившегося в запоминающей ячейке, в схеме применяется RS-триггер, включенный между двумя линиями записи/считывания. Схема такого включения приведена на рис.3. Эта схема за счет положительной обратной связи восстанавливает первоначальное значение напряжения в запоминающем элементе, подключенном к выбранной линии считывания. То есть при считывании ячейки производится регенерация хранящегося в ней заряда. Для уменьшения времени регенерации микросхема устроена так, что при считывании одной ячейки памяти в строке запоминающей матрицы регенерируется вся строка. Особенностью динамических ОЗУ также является мультиплексирование шины адреса. Адрес строки и адрес столбца передаются поочередно.

память типа "первым вошел - первым вышел" ( FIFO, First In - First Out);

память магазинного, стекового типа, работающая по принципу "последним вошел - первым вышел" (LIFO, Last In - First Out).

память FIFO выдает

читаемые данные в том же порядке, в

котором они были записаны, а память LIFO -

в порядке, обратном тому, в котором они

были записаны в память. Память FIFO можно

сравнить со сдвиговым регистром, на

выходе которого данные появляются в

том же порядке, в котором они были в него

записаны. А память LIFOобычно

сравнивают с магазином для подачи

патронов в автомате или пистолете, в

котором первым выдается патрон,

вставленный в магазин последним. Память

с принципом LIFO используется,

в частности, в компьютерах ( стек ),

где она хранит информацию о параметрах

программ и подпрограмм.

Для памяти FIFO требуется хранение двух кодов адреса (адрес для записи и адрес для чтения), для памяти LIFO достаточно одного кода адреса.

Рис. 12.5. Функциональная схема памяти типа FIFO

Видеопамять — часть оперативной памяти, отведённая для хранения данных, которые используются для формирования изображения на экранемонитора.

При этом в видеопамяти может содержаться как непосредственно растровый образ изображения (экранный кадр), так и отдельные фрагменты как в растровой (текстуры), так и в векторной (многоугольники, в частности треугольники) формах.

Существует выделенная оперативная память видеокарты, также называемая «видеопамять». Такая оперативная память используется только под нужды различных графических приложений и игр.

Как правило, чипы оперативной памяти современной видеокарты припаяны прямо к текстолиту печатной платы, в отличие от съёмных модулей системной памяти, которые вставляются в стандартизированные разъёмы ранних видеоадаптеров.

Архитектура CPLD и FPGA

| |

|

Архитектура CPLD напоминает популярную PAL архитектуру, когда логические ресурсы реализуются массивом элементов И, объединённых элементами ИЛИ, в свою очередь заведёнными на триггера или непосредственно на выход. Такая простая логическая структура достаточно проста для понимания, обеспечивает чрезвычайно корокое время компиляции и минимальные задержки pin-to-pin. Для программирования МС CPLD, выпускаемых Xilinx не требуется программатор – перепрограммирование осуществляется сигналами через специальные выводы МС (JTAG), т.е. производится в той же системе, где и применяется данная ПЛИС. К особенностям МС CPLD Xilinx можно отнести:

В настоящее время выпускается две серии ПЛИС с CPLD архитектурой: Серия Fast Flash CPLD XC9500 Серия CoolRunner CPLD |

CPLD (англ. complex programmable logic device — сложные программируемые логические устройства) содержат относительно крупные программируемые логические блоки — макроячейки (англ. macrocells), соединённые с внешними выводами и внутренними шинами. Функциональность CPLD кодируется в энергонезависимой памяти, поэтому нет необходимости их перепрограммировать при включении. Может применяться для расширения числа входов/выходов рядом с большими кристаллами, или для предобработки сигналов (например, контроллер COM-порта, USB, VGA).

Основой CPLD является матрица макроячеек, в которой реализованы логические соединениявентилейили более сложные логические операции. Блоки макроячеек объединены программируемой коммутационной матрицей с последующим выходом на входы (выходы) схемы.[1]

Общие особенности технологий:

CPLD и PAL:

Энергонезависимая («Non-volatile»(англ.)) конфигурационная память. В отличие от большинства FPGA, для CPLD не требуется еще одна микросхема для их конфигурации (ROM), и CPLD может функционировать непосредственно после подачи на него питания (включения).

В исходных вариантах CPLD маршрутизация ограничивала возможность подключения большинства логических блоков к их каналам ввода/вывода через внешние пины, что не позволяло оптимально использовать внутреннюю память микросхем и реализовать многоуровневую логику. Для более новых семейств больших CPLD это ограничение уже не характерно.

CPLD и FPGA:

Большое количество доступных логических вентилей. CPLD обычно имеют от нескольких тысяч до десятков тысяч логических вентилей, что позволет реализовать сравнительно сложные устройства обработки данных (для PAL это - до нескольких сотен логических вентилей, максимум. В отличие от них, количество вентилей в современных FPGA может достигать нескольких миллионов.

|

Для FPGA возможно программирование более гибкой и сложной логики, чем простейшие выражения типа суммы произведений, вплоть до реализации как элементовDSP,цифровых фильтров, так иCPUв целом (в отличие от CPLD, технология FPGA базируется на вентильных матрицахLook-up tables (LUTs). ПЛИС типа FPGA фирмы Xilinx выполнены по SRAM к-МОП технологии. Характеризуются высокой гибкостью структуры и изобилием на кристалле триггеров. При этом логика реализуется посредством так называемых LUT - таблиц (Look Up Table) Xilinx, а внутренние межсоединения - посредством разветвлённой иерархии металлических линий, коммутируемых специальными быстродействующими транзисторами. Блок схема архитектуры ПЛИС FPGA Отличительными системными особенностями являются:

|

FPGA (англ. field-programmable gate array) содержат блоки умножения-суммирования, которые широко применяются при обработке сигналов (DSP), а также логические элементы (как правило, на базе таблиц перекодировки — таблиц истинности) и их блоки коммутации. FPGA обычно используются для обработки сигналов, имеют больше логических элементов и более гибкую архитектуру, чем CPLD. Программа для FPGA хранится в распределённой памяти, которая может быть выполнена как на основе энергозависимых ячеек статического ОЗУ (подобные микросхемы производят, например, фирмы Xilinx и Altera) — в этом случае программа не сохраняется при исчезновении электропитания микросхемы, так и на основе энергонезависимых ячеек Flash-памяти или перемычек antifuse (такие микросхемы производит фирма Actel и Lattice Semiconductor) — в этих случаях программа сохраняется при исчезновении электропитания. Если программа хранится в энергозависимой памяти, то при каждом включении питания микросхемы необходимо заново конфигурировать её при помощи начального загрузчика, который может быть встроен и в саму FPGA. Альтернативой ПЛИС FPGA являются более медленные цифровые процессоры обработки сигналов. FPGA применяются также, как ускорители универсальных процессоров в суперкомпьютерах (например: Cray — XD1, SGI — Проект RASC).

В России микросхемы обоих типов принято называть ПЛИС - Программируемая Логическая Интегральная Схема. Основные отличия производителей устройств ПЛИС друг от друга заключается в архитектуре построения внутренних программируемых комбинационных схем, способом загрузки программирования ПЛИС, емкостью логических элементов, числом эквивалентных вентилей, технологии изготовления кристаллов, различные типы корпусов ПЛИС и т. д.

Языки описания цифровых схем

Язык описания аппаратуры (англ. hardware description language) — класс языков программирования для формального описания электрических цепей, особенно цифровой логики. Он описывает структуру и функционирование цепи.

AHDL — проприетарный язык описания аппаратуры от Altera Corporation предназначенный для программированя выпускаемых ей ПЛИС. Язык имеет Ада-подобный синтаксис и схож с VHDL или Verilog. Он поддерживается компиляторами Quartus и Max+ от Altera.

Недостаток AHDL в его проприетарности. Преимущество AHDL в том, что все конструкции языка синтезируемы. В сравнении с Verilog AHDL как язык ассемблера в сравнении с языком высокого уровня: в AHDL больше контроля, но меньше высокоуровниевой поддержки.

VHDL (англ. VHSIC (Very high speed integrated circuits) Hardware Description Language) — язык описания аппаратуры интегральных схем. Язык проектирования VHDL является базовым языком при разработке аппаратуры современных вычислительных систем.

Был разработан в 1983 г. по заказу Министерства обороны США с целью формального описания логических схем для всех этапов разработки электронных систем, начиная модулями микросхем и заканчивая крупными вычислительными системами.

Verilog, Verilog HDL (англ. Verilog Hardware Description Language) — это язык описания аппаратуры, используемый для описания и моделирования электронных систем. Verilog HDL, не следует путать с VHDL (конкурирующий язык), наиболее часто используется в проектирование, верификации и реализации (например, в виде СБИС) аналоговых, цифровых и смешанных электронных систем на различных уровнях абстракции.

Разработчики Verilog сделали его синтаксис очень похожим на синтаксис языка C, что упрощает его освоение. Verilog имеет препроцессор, очень похожий на препроцессор языка C, и основные управляющие конструкции «if», «while» также подобны одноимённым конструкциям языка C. Соглашения по форматированию вывода также очень похожи

Отличие Verilog от VHDL в данном случае состоит в том, что для описания фронтов и срезов сигналов используются не специализированные атрибуты сигнала, а специальная конструкция языка.

module trig(clock, a, b, switch, reset, out); input clock, reset; //Тактовая частота и сброс input a, b; //Входы input switch; //Управляющий сигнал

output out; //Выход триггера. Здесь будет то, что он запомнил reg out; //Пояснили, что это кусочек памяти

wire in; assign in = switch ? a : b; //Жесткая привязка //assign in = a ? 1 : 0; //Так мы бы получили D-триггер, запоминающий один параметр //assign in = a; //А вот так - RS-триггер, где Set - это «a», а Reset - «reset»

always @(posedge clock or posedge reset) //Если пришел клок или ресет if (reset) //Если ресет, то обнуляем выход out <= 0; else //Иначе обновляем значение out <= in; endmodule

Последовательность создания проектов на ПЛИС

Отладка:

Проект, заданный в виде модели, может быть оптимизирован по следующим пунктам:

по скорости – при этом обеспечиваются минимальные задержки

по минимальному расходу аппаратных ресурсов

проект может быть оптимизирован под разные структуры микросхем (PLD, FPGA), следовательно, цена будет изменяться в зависимости от выбора структуры

проект может быть реализован на разных семействах микросхем

проект можно реализовать на микросхемах, программируемых непосредственно пользователем или на полузаказных микросхемах

проект может быть выполнен на заказных микросхемах, где будет все максимально оптимизировано, но это будет выгодно только для больших партий (100-10000 штук).

Верификация – процесс выявления работоспособности системы на симуляторе. Позволяет оценить функциональность, работоспособность, выявить реальные задержки и т.д. Если верификация доведена практически до готового проекта, то с помощью симулятора могут быть выявлены проблемы целостности сигнала, помехи, тепловые режимы и т.д.

Верификации: проектов путем запуска комплексных тестов, получающих данные от сторонних программ и имеющих встроенные средства контроля правильности своего исполнения.

Внутри чипа у нас целая цифровая схема из набора триггеров и таблиц истинности. Естественно цифровые устройства отлаживают с помощью логического анализатора: подключаемся к нужным сигналам на плате и смотрим как они изменяются. Внутрь микросхемы мы конечно же щупом не залезем, но можно вывести необходимые сигналы на неиспользуемые выводы и к ним уже подключать лог. анализатор (или светодиоды :)). С этим может помочь SignalProbe (Tools->SignalProbe Pins…), он позволяет взять название любого сигнала из проекта и назначит его на какой-то вывод, интерфейс довольно понятный, описывать не буду, да и средство не очень интересное. Более интересная штука это внутрисхемный логический анализатор который можно добавить в проект на FPGA (ограничение связано с наличием внутренней память, в CPLD микросхем ее покаместь нет). SignalTap II Logic Analyzer Мощная и интересная штука: — позволяет наблюдать почти любой внутренний или внешний сигнал — частота выборок ограничена только быстродействием чипа (для Циклона 250 МГц) — до 2048 каналов — 128к выборок на канал — поддерживаются все FPGA семейства — отслеживание состояний конечного автомата — гибкая настройка моментов выборки За все это конечно придется платить местом в чипе и блоками памяти, чем больше каналов и сложнее система выборок тем больше логических ячеек займет анализатор.

Синхронизация в ПЛИС. Работа с несколькими частотами.

Большие проекты для ПЛИС обычно разбиваюца на отдельные части - компоненты. Реализацию пишут, например, на VHDL. В моем случае я сперва разработал архитектуру проекта, соединил "кубики" в графическом редакторе ISE 7. Написал на VHDL код для этих "кубиков". Один из компонентов проекта - ресивер для RS-232. Я сделал ему клок 50 МГц чтобы не мучаца с ошибками. Остальные компоненты у меня раюотают от частоты 20МГц, т.к. у меня внешнее АЦП работает от 20МГц. Возникла проблема синхронизации данных. Клок сделал как написано в мануале - взял DCM, вытацил из него через буфферы BUFG два клока - 50 МГц и 20 МГц, завел feedback (цепь обратной связи для синхронизации). Но полезли глюки ))) вот сижу и думаю, как бы сделать синхронизацию.

Тут есть два варианта: либо делайте все на 50 МГц, либо ставьте синхронизаторы и FIFO для передачи данных и управляющих сигналов между блоками, работающими на разных частотах. Поищите на форуме по ключевым словам "синхронизатор", "метастабильность". Эта тема уже не раз обсуждалась в разных вариациях.

Метастабильность - это состояние триггера, в котором может находиться после нарушения его временных параметров (времени предварительной установки, удержания и т.п.). Бороться нужно с помощью специальных схем - синхронизаторов.

Синхронизация в ПЛИС, Работа с несколькими частотами

Архитектура микропроцессоров

Архитектура совокупность программно-аппаратных свойств, предоставляемых пользователю.

Микропроцессор (МП) - это программно управляемое устройство, которое предназначено для обработки цифровой информации и управления процессом этой обработки и выполнено в виде одной или нескольких больших интегральных схем (БИС).

Понятие большая

интегральная схема в

настоящее время четко не определено.

Ранее считалось, что к этому классу

следует относить микросхемы, содержащие

более 1000 элементов на кристалле. И

действительно, в эти параметры укладывались

первые микропроцессоры. Например,

4-разрядная процессорная секция

микропроцессорного комплекта К584,

выпускавшегося в конце 1970-х годов,

содержала около 1500 элементов. Сейчас,

когда микропроцессоры содержат десятки

миллионов транзисторов и их количество

непрерывно увеличивается, под БИС будем

понимать функционально сложную

интегральную схему.