- •2 Описание и принцип работы узлов учебной микроэвм

- •2. Описание клавиатуры и индикации

- •3. Команды системы “Монитор”

- •3.1. Индикация и изменение содержимого памяти

- •3.2. Индикация и изменение содержимого регистров

- •3.3. Передача управления программе пользователя

- •3.4. Определение контрольной суммы массива памяти

- •3.5. Заполнение массива памяти константой

- •3.6. Перемещение массива памяти в адресном пространстве

- •3.7. Прерывание выполнения программы пользователя

- •3.8. Пошаговое выполнение программы

- •2. Порядок выполнения

- •3.Содержание отчета

- •Контрольные вопросы

- •Практическое занятие 3 Программирование алгоритмов с циклической структурой

- •Общие указания

- •2. Порядок выполнения

- •Программирование алгоритмов с разветвленной структурой

- •Дешифрация адресного пространства мпс

- •2. Порядок выполнения работы

- •3. Содержание отчета

- •4.Контрольные вопросы

- •Практическое занятие 6 Построение модулей памяти микропроцессорных систем

- •1. Общие сведения

- •2. Задание для самостоятельной работы:

- •3.Порядок выполнения:

- •4. Содержание отчета:

- •Практическое занятие 7 Исследование и настройка параллельного адаптера

- •1. Общие сведения

- •2. Порядок выполнения работы

- •3. Содержание отчета

- •4.Контрольные вопросы

- •Методичні вказівки

- •«Компъютерная схемотехника»

- •91034 Р. Луганськ

Дешифрация адресного пространства мпс

Цель занятия: приобретение навыков дешифрирования адресного пространстиа 8-ми разрядных МП методом частичной дешифрации на базе аппаратрых дешифраторов.

1. Общие сведения

Адресное пространство МПС.

Адресное пространство определяет число возможных отличимых друг от друга кодовых комбинаций (адресов), которые может выдать на адресную шину активное устройство. Это, конечно, не означает, что каждой такой комбинации соответствует программно-доступный элемент. Адресное пространство определяет лишь потенциальные возможности системы—максимальное число программно-доступных элементов, которые могут присутствовать в ней. Поэтому адресное пространство можно сравнить с пустым или частично заполненным помещением библиотеки, в котором можно разместить, например, не более 64К книг.

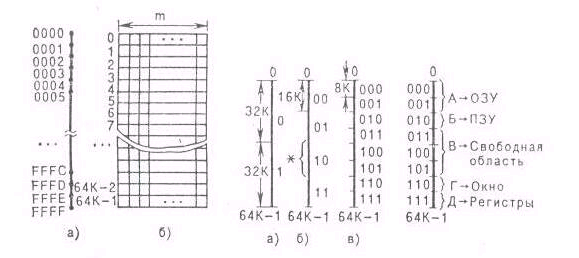

Старший двоичный разряд адреса делит адресное пространство на две равные части (рис.5.2, а), два старших разряда делят его на четыре равные части (рис.5.2,6), три старших разряда—на восемь равных частей (рис. 2, б) и т.д. Шестнадцать разрядов адреса делят адресное пространство емкостью 64К на 64К частей по одной

ячейке.

Если адресная шина содержит всего три сигнальные линии, то по ней можно передать 23= 8 различных адресов: 000, 001, 010, 01l, 100, 101, 110, 111. При четырех линиях число возможных состояний шины составляет 24=16: 0000, 0001,..., 1111; при 16 линиях число возможных состояний составляет 216=65536=64К, где К=210=1024.

Адресное пространство представляет собой упорядоченное множество кодов 0, 1, 2,..., (2n—1); где n—число адресных линий. Это множество для наглядности представляют в виде отрезка числовой оси либо в виде таблицы, как показано на рис.5.1 (n=16). Нумерация точек, или «ячеек», адресного пространства при его графическом представлении производится снизу вверх или сверху вниз (что удобнее) в десятичной, восьмеричной или шестнадцатеричной форме.

р ис5.1.

Табличная форма изображения рис 5.2.

Примеры распределения

ис5.1.

Табличная форма изображения рис 5.2.

Примеры распределения

адресного пространства адресного пространства

Схемы адресных дешифраторов

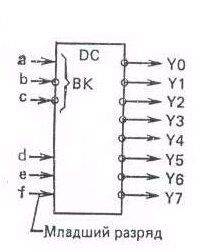

И спользование

стандартных дешифраторов для разделения

адресного пространства. На рис. 9

приведена схема дешифратора, имеющего

три входа ВК выбора кристалла (а, Ь, с),

три информационных входа (d, е, f) и

восемь выходов YO — Y7. Если (а, Ь, с) <>

(1, 0, 0), то YO=Y1=...=Y7==1, т.е. дешифратор

выключен. При (а, Ь, с)==(1, 0, 0), т.е. при

обеспечении условий выбора кристалла,

. работа дешифратора описывается

табл.5.1.

спользование

стандартных дешифраторов для разделения

адресного пространства. На рис. 9

приведена схема дешифратора, имеющего

три входа ВК выбора кристалла (а, Ь, с),

три информационных входа (d, е, f) и

восемь выходов YO — Y7. Если (а, Ь, с) <>

(1, 0, 0), то YO=Y1=...=Y7==1, т.е. дешифратор

выключен. При (а, Ь, с)==(1, 0, 0), т.е. при

обеспечении условий выбора кристалла,

. работа дешифратора описывается

табл.5.1.

Р ис.5.1.дешифратор

3х8(74LS138)

ис.5.1.дешифратор

3х8(74LS138)

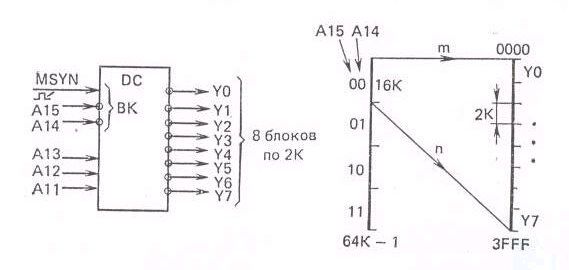

Рис.5.3. Разделение адресного пространства объемом 64K ячеек на восемь зон по 8К ячеек

Таблица 5.1. Состояния дешифратора

d |

е |

f |

YO |

VI |

Y2 |

Y3 |

Y4 |

Y5 |

yj |

Y7 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

! |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Рассмотрим несколько примеров использования этого дешифратора для разделения адресного пространства.

Пример 1. Подключим прямой вход ВК к линии сопровождения адреса MSVN, заземлив два других (инверсных) входа ВК. Информационные входы дешифратора подключим к трем старшим линиям адресной шины (рис. 10). Такое включение дешифратора позволяет разбить адресное пространство объемом 64K ячеек на восемь зон по 8К ячеек. Если подключить осциллограф, например, к выводу Y4 дешифратора, то, обнаружив отрицательный импульс на этом выводе, можно быть уверенным, что процессор в этот период времени обращался по одному из адресов, лежащих в зоне 8000—9FFF. Эта зона помечена на рис. 10 знаком *.

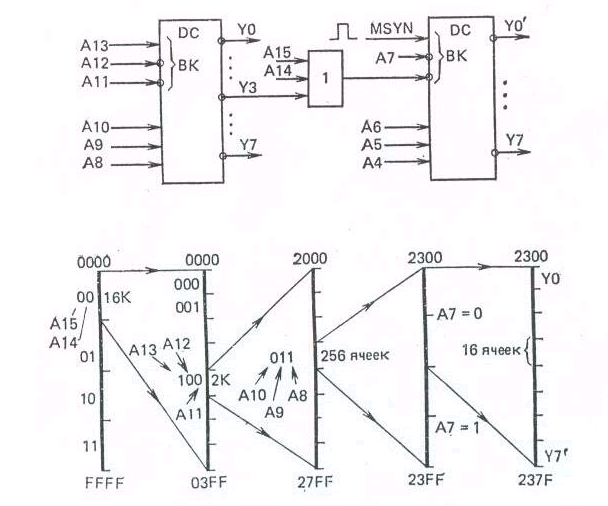

Пример2. Схема включения, показанная на рис. 11, позволяет выделять в адресном пространстве восемь блоков no 2K ячеек.

Р ис.

5.3.Выделение восьми блоков по 2K ячеек

ис.

5.3.Выделение восьми блоков по 2K ячеек

Работа дешифратора возможна только тогда, когда на входы ВК поступит нужное сочетание сигналов, т. е. при А15=А14=0. Это произойдет при попадании адреса в первую четверть адресного пространства, вынесенную на рис. 11 для наглядности вправо с помощью стрелок m и n. В зависимости от сочетания нулей и единиц на входах А13—А11 мы попадаем в одну из восьми долей первой четверти адресного пространства, т. е. в зону размером 2K ячеек.

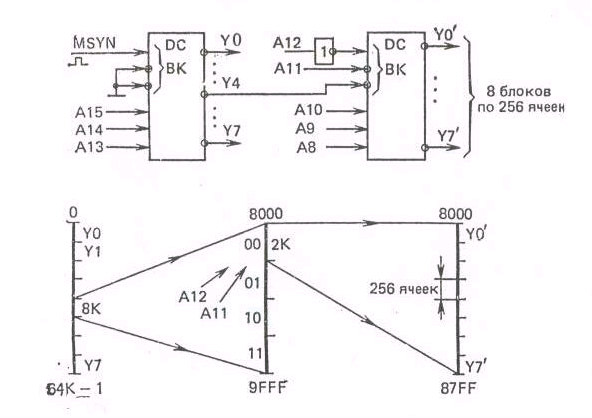

Пример.3. Схема последовательно включенных дешифраторов, приведенная на рис. 5.4 позволяет выделять восемь блоков по 256 ячеек.

Пример 4. Схема, приведенная на рис.5.5. позволяет выделять восемь блоков но 16 ячеек.

Использование ПЗУ в качестве адресного дешифратора. Пусть требуется выделить зоны адресного пространства для размещения в них адресов следующих устройств, каждое из которых представляет собой одну микросхему:,

а) ПЗУ1 зону F000—FFFF, 4K ячеек;

б) ПЗУ2 зону E000—EFFF, 4K ячеек;

в) ОЗУ1 зону A000—A7FF, 2K ячеек;

г) УВВ зону 8000—87FF, 2K ячеек;

д) ОЗУ2 зону 0000—3FFF, 16К ячеек.

Р ис.5.4.

Выделение восьми блоков по 256 ячеек

ис.5.4.

Выделение восьми блоков по 256 ячеек

Рис.5.5. Выделение восьми блоков по 16 ячеек

Так как наименьший блок имеет размер 2К ячеек, то разрешающая способность дешифратора должна обеспечивать деление адресного пространства с точностью до зон размером 2К ячеек. Анализируя пять старших разрядов адреса, получаем необходимую точность, поскольку они делят все адресное пространство объемом 64К ячеек на 25=32 части по 2К ячеек, что и требуется.

Выбираем за основу ПЗУ с пятью адресными входами, имеющее структуру 32х8 бит (рис.5.6). Выходы А—Д этого ПЗУ подключаем к инверсным входам выбора кристалла соответствующих микросхем (см. условие задачи).

Р ис.

5.6 Микросхема ПЗУ 32Х8 бит, подключенная

к адресной шине

ис.

5.6 Микросхема ПЗУ 32Х8 бит, подключенная

к адресной шине

Теперь задача сводится к тому, чтобы разметать все адресное пространство, продвигаясь по нему с шагом 2К ячеек и выбирая на каждом шаге желаемую выходную реакцию. Другими словами, задача сводится к разработке таблицы кодировки ПЗУ, которая в дальнейшем «зашивается» в микросхему. Содержимое ПЗУ представлено в табл.5.2

Если, например, старшие разряды адреса попадают в диапазон 00000— 001112, то это означает, что полный 16-разрядный адрес лежит в диапазоне 0000—3FFF16. При этом, согласно условию задачи, на выходе Д ПЗУ нужно закодировать 0 (см. табл.5.2,)что обеспечит выбор ОЗУ2. Программирование остальных условий производится аналогично.

Заметим, что в данном применении ПЗУ напоминает стандартный дешифратор, в котором нуль не «бежит по диагонали», как в табл. 5.1, а программируется по усмотрению пользователя (табл.5. 2). Перераспределение адресного пространства микроЭВМ достигается простой заменой микросхемы (кодировки ПЗУ). Для удобства замены микросхема ПЗУ может не припаиваться своими выводами к печатной плате, а устанавливаться на контактирующей колодке.

Таблица 5.2. Дешифрация адресои на базе микросхемы ПЗУ

Диапазон

|

|

|

Входы

|

|

|

|

|

Выходы

|

|

|

адресов

|

А15

|

А14

|

AI3

|

A12

|

All

|

А

|

Б |

В

|

Г

|

Д |

0000— 07FF

|

0

|

0

|

0

|

0

|

0

|

1

|

1 |

1

|

1

|

0

|

0800-OFFF

|

0

|

0

|

0

|

0

|

1

|

1

|

1 |

1

|

1

|

0

|

1000— 17FF

|

0

|

0

|

0

|

1

|

0

|

1

|

1 |

1

|

1

|

0

|