- •3. Оператор generate порождающей схемы if Оператора generate порождающей схемы if имеет такой синтаксис:

- •Как видно из рис.2, схема счетчика помимо регулярного блока (Regular block) содержит в своем составе и особые места, где регулярность в соединениях и по составу компонент нарушается.

- •Примечание:

- •Последний механизм позволяет вкладывать проекты имеющих регулярных структур и формировать многомерные массивы из компонентов.

- •Оператором Generic( ) имеет такой синтаксис:

- •Временная диаграмма работы проекта

Файл:

Лекция № 7 (5-тый курс)

Тема: Структурная методология описания проектов цифровых систем (устройств) с регулярной структурой посредством оператора generate.

О задании глобальных параметров проекта из внешней среды (оператор generic( ))

(Структурная методология описания проектов систолических цифровых систем (устройств) посредством оператора generate)

Вопросы по теме:

Вводные замечания

Оператор generate порождающей схемы for

Оператор generate порождающей схемы if

4. О задании глобальных настроечных параметров для проекта из внешней среды (оператор generic( ))

Систолическими цифровыми устройствами в цифровой схемотехнике принято называть такие устройства, которые содержат в своей структуре (архитектуре) множество однотипных (абсолютно одинаковых) по своему устройству элементов (компонентов). Примерами цифровых устройств с регулярной структурой являются N-разрядный двоичный счетчик, N-разрядный сумматор. Так N-разрядный двоичный счетчик содержит в своей структуре множество однотипных триггеров (триггеров типа D или триггеров типа JK). В свою очередь, N-разрядный сумматор содержит в своей структуре множество полных однотипных одноразрядных сумматоров. Заметим, что в систолических цифровых устройствах схема соединений компонентов часто также является регулярной.

Естественно, что для проектирования цифровых устройств такого вида посредством языка VHDL целесообразно использовать структурную (компонентную) методологию описания их проектов. Выгода использования этой методологии объясняется тем, что один раз создав субпроект описания компонента (триггера, одноразрядного сумматора) она позволяет его многократное использование (существующего описания компонента).

Проекты систолических цифровых устройств, естественно, можно создавать на основе структурной классической методологии, которая предусматривает использование в проекте семейства операторов внедрения компонента. При этом количество содержащихся проекте операторов внедрения компонент должно соответствовать разрядности проектируемого устройства.

Значительно упростить процесс создания проектов цифровых устройств (имеющих большую разрядность) с систолической структурой можно за счет применения оператора generate.

Применение оператора generate (generate statement) также значительно уменьшает объем описание проектов устройств с регулярной структурой.

Следует заметить, что удобство использования оператора проявляется, когда требуется создать проект устройства с большей или меньшей разрядностью, из уже существующего проекта того же функционального назначения.

Таким образом, применение оператора generate даст возможность определить группу идентичных компонентов, использующих только одну спецификацию компонента и многократное внедрение спецификации компонента за счет генерирующего (порождающего) механизма оператора.

По своему конструктивному устройству оператор generate относится к классу составных операторов.

Конструкция Оператора generate состоит из трех главных частей:

Объявления generation scheme (порождающей (генерирующей) схемы). Порождающая схема может иметь вид for или вид if; Порождающая схема for определяет, каким образом (сколько раз) должны выполнятся операторы, располагаемые в подразделе выполняемых конкурентных операторов. Порождающая схема for определяет, каким образом (сколько раз) должны выполнятся операторы, располагаемые в подразделе выполняемых конкурентных операторов. Порождающая схема if определяет, каким образом (при каком условии) должны выполнятся операторы, располагаемые в подразделе выполняемых конкурентных операторов

Подраздела Деклараций (В подразделе деклараций могут располагаться локальные объявления подпрограмм, типов, сигналов, констант, компонентов, атрибутов, конфигураций, файлов и групп);

Подраздела выполняемых конкурентных (параллельно выполняемых) операторов.

2. Оператора generate порождающей схемы for

Оператора generate порождающей схемы for имеет такой синтаксис:

Label(метка) : for parameter (переменная цикла) in range (параметры цикла) generate

[ { declarations – подраздел деклараций}

begin ]

{ concurrent_statements – подраздел конкурентных операторов}

end generate [ label ] ;

Каждый оператор generate порождающей схемы for… generate должен иметь метку.

Если оператор generate порождающей схемы for… generate не содержит никакие локальные объявления, то ключевое слово begin использовать не нужно.

Оператор generate порождающей схемы for… generate может быть вложенным.

Оператор обязательно должен заканчиваться ключевыми словами end generate

Как видно из синтаксиса оператора generate этой разновидности, порождающая схема for определяет, каким образом (сколько раз) должны выполнятся операторы, располагаемые в его подразделе выполняемых конкурентных операторов. Другими словами, порождающая схема for используется, чтобы описать сколько раз требуется внедрить в проект систолического устройства имеющееся описание одного и того же компонента.

Пример 1 иллюстрирует применение концепции порождающей схема for в VHDL проекте 4-битного двоичного счетчика, где в качестве компонент использованы 4 триггера типа D.

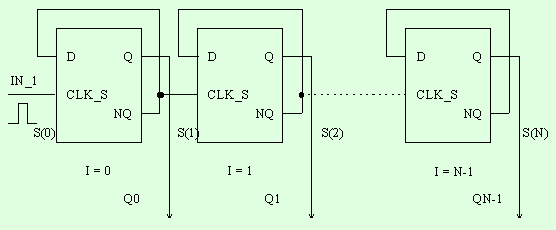

Для наглядности иллюстрации этой концепции на Рис.1 приведена схема электрическая принципиальная двоичного счетчика реализованного (instantiates) из N D-триггеров.

Рис. 1. Двоичный N-битный накапливающий счетчик.

Пример 1.

Субпроект триггера типа D. (Этот Субпроект является определением будущей компоненты (component D_FF), которая будет многократно внедряться, в проект счетчика с систолической структурой)

entity D_FF is

port (D,CLK_S : in BIT;

Q : out BIT := '0';

NQ : out BIT := '1' );

end entity D_FF;

architecture A_RS_FF of D_FF is

begin

BIN_P_RS_FF: process(CLK_S)

begin

if CLK_S = '1' and CLK_S'Event

then Q <= D;

NQ <= not D;

end if;

end process;

end architecture A_RS_FF;

Субпроект верхнего уровня Двоичного 4-битного накапливающего счетчика.

entity COUNTER_BIN_N is

generic (N : Integer := 4);

port (Q : out Bit_Vector (0 to N-1);

IN_1 : in Bit );

end entity COUNTER_BIN_N;

architecture BEH of COUNTER_BIN_N is

component D_FF

port(D, CLK_S : in BIT; Q, NQ : out BIT);

end component D_FF;

signal S : BIT_VECTOR(0 to N);

begin

S(0) <= IN_1;

G_1 : for I in 0 to N-1 generate

D_Flip_Flop : D_FF port map(S(I+1), S(I), Q(I), S(I+1));

end generate;

end architecture BEH;

В примере 1 сначала дана спецификация D триггера, который затем использован в качестве компонента (в соответствии с объявлением component D_FF) в проекте верхнего уровня entity COUNTER_BIN_N. Оператор generate порождающей схемы for… generate используется в проекте верхнего уровня entity COUNTER_BIN_N, чтобы 4-ре раза внедрить компонент component D_FF посредством оператора внедрения компонента D_Flip_Flop : D_FF port map(S(I+1), S(I), Q(I), S(I+1)); Количество внедрений компонента component D_FF определено параметрами переменной цикла I. Предельное верхнее значение параметра N переменной цикла I указано в проекте посредством оператора generic (N : Integer := 4);

3. Оператор generate порождающей схемы if Оператора generate порождающей схемы if имеет такой синтаксис:

label (метка): if condition (условие) generate

[ { declarations – подраздел деклараций}

begin ]

{ concurrent_statements – подраздел конкурентных операторов}

end generate [ label ] ;

Как видно из синтаксиса оператора generate порождающей схемы if ... generate операторы, располагаемые в его подразделе конкурентных операторов, будут выполнены только в случае истинности (true) некоторого условия (condition). Введение этого вида оператора в язык VHDL вызвано тем, что цифровые устройства в своем составе кроме фрагментов систолической структуры могут содержать и особые места, где соединения входов/выходов компонент следует выполнить особым образом. Возможны также ситуации, когда структурная схема цифрового устройства содержит в своем составе два (или несколько) фрагментов совершенно разных регулярных фрагментов. В таких случаях, при создании VHDL проектов цифровых устройств с полурегулярной структурой может оказаться очень полезной порождающая схема if... generate.

Каждый оператор generate порождающей схемы if... generate должен иметь метку.

Если оператор generate порождающей схемы if... generate не содержит никакие локальные объявления, то ключевое слово begin использовать не нужно.

Оператор generate порождающей схемы if... generate может быть вложенным.

Оператор обязательно должен заканчиваться ключевыми словами end generate

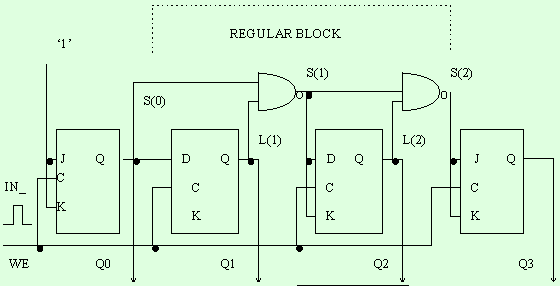

Примером цифрового устройства с полурегулярной структурой является синхронный двоично-десятичный счетчик. Схема электрическая принципиальная двоично-десятичного счетчика построенного на базе JK-триггеров показана на Рис.2. Схема такого счетчика помимо JK-триггеров содержит в своем составе логические элементы И-НЕ.

Рис. 2. Накапливающий счетчик ДВОИЧНО-ДЕСЯТИЧНОГО КОДА.

Как видно из рис.2, схема счетчика помимо регулярного блока (Regular block) содержит в своем составе и особые места, где регулярность в соединениях и по составу компонент нарушается.

«Палочкой-выручалочкой», при создании VHDL проекта такого счетчика, может стать оператор generate порождающей схемы if ... generate.

В примере 2 показана методология применения оператора generate порождающей схемы if ... generate.

Пример 2

-- the BCD counter (Проект счетчика entity COUNTER_BCD разработан здесь, в предположении того, что определение компонент component D_FF и component NAND_GATE уже существуют)

entity COUNTER_BCD is –- объявление проекта

port (IN_1 : in Bit; --объявление входных портов

Q:out Bit_Vector(0 to 3)); --объявление выходных портов

end entity COUNTER_BCD;

architecture STRUCT of COUNTER_BCD is -- объявление и определение архитектуры

component D_FF -–объявление компоненты

port (J, K, CLK_S : in BIT; Q: out BIT);

end component D_FF;

component NAND_GATE -–объявление компоненты

port (IN1, IN2 : in Bit; OUT1 : out Bit);

end component NAND_GATE;

signal S: Bit_vector(0 to 2); --объявление внутреннего сигнала

signal L: Bit_vector(0 to 1);

begin

--подраздел выполняемых конкурентных операторов тела архитектуры

D_FF_0 : D_FF port map ('1','1',IN_1, S(0)); --оператор внедрения компонента (крайнего левого

- - триггера на схеме рис.2)

Gen_1 : for I in 1 to 3 generate

Gen_2 : if I = 1 or I = 2 generate - - оператор порождающий проверку компонент

- - входящих в регулярный блок Рис.2

D_FF_I : D_FF port map (S(I-1),S(I-1), IN_1, L(I-1));--внедр.D_FF

NAND_I : NAND_GATE port map (S(I-1),L(I-1), S(I));--внедр.NAND_GATE

Q(I) <= L(I-1); -- назначение значения выходному порту Q(I)

end generate Gen_2;

Gen_3 : if I = 3 generate - - оператор порождающий проверку правой крайней компоненты

- - Рис.2

D_FF_3 : D_FF port map (S(I-1),S(I-1), IN_1, Q(I) );

end generate Gen_3;

end generate Gen_1;

Q(0) <= S(0); --назначение значения выходному порту Q(0)

end STRUCT;

В проекте примера 2 применение вложенных операторов Gen_2 : if I = 1 or I = 2 generate и Gen_3 : if I = 3 generate позволило сократить объем описания проекта. Ведущий оператор Gen_1 : for I in 1 to 3 generate доопределил в проекте три старших разряда, т.е. сгенерировал инструкциями (операторами) своего тела внедрение компонент номера которых на схеме ассоциированы с со значением переменной цикла I.