- •Автоматизированное проектирование криптографических систем

- •Вводная лекция

- •Задачи, стоящие перед курсом и формы обучения.

- •Раздел vhdl проектирования электронной системы защиты информации, алгоритм которой базируется на одном из известных Вам методов шифрования/дешифрования информации.

- •Язык vhdl в проектировании электронных систем защиты информации.

- •3. Примеры программных проектов криптографических процессоров в разных версиях языка vhdl

- •3.1 Vhdl проект шифрующего/дешифрующего (криптографического) процессора оперирующего с ascii кодами и построенного на использовании одного из вариантов аналитических методов защиты.

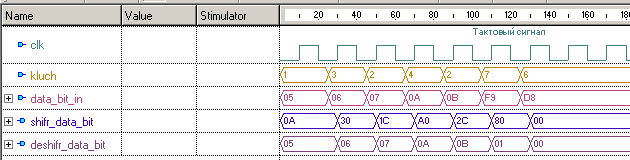

- •Временная диаграмма работы проекта

- •5. Дополнительный материал

Временная диаграмма работы проекта

3.2 VHDL проект шифрующего/дешифрующего (криптографического) процессора оперирующего с ASCII кодами и построенного на использовании одного из вариантов логических методов шифрования (Здесь используются сдвиговые операции).

-- library IEEE;

-- use IEEE.STD_LOGIC_1164.all;

-- use IEEE.Numeric_Bit.all;

entity bit_shift is

port(

clk : in bit;

data_bit_in : in BIT_Vector (7 downto 0);

kluch : in INTEGER range 0 to 7;

shifr_data_bit : out BIT_Vector(7 downto 0);

deshifr_data_bit : out BIT_Vector(7 downto 0));

end bit_shift;

architecture bit_shifta of bit_shift is

begin

process (clk)

variable data_in_prom, data_prom_Sdv_righ : BIT_Vector(7 downto 0);

begin

data_in_prom := data_bit_in;

data_in_prom := data_in_prom sll kluch; --шифров.дан.

shifr_data_bit <= data_in_prom ;

data_prom_Sdv_righ := data_in_prom srl kluch;

deshifr_data_bit <= data_prom_Sdv_righ;

end process;

end bit_shifta;

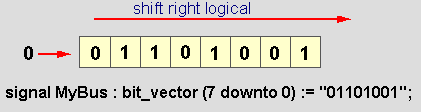

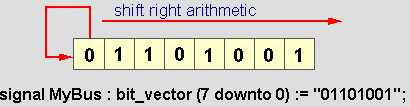

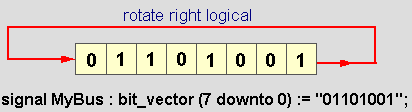

В этом проекте криптографический процессор построен на базе сдвиговых операций. Исходные шифруемые данные, а также зашифрованные и дешифрованные данные представлены типом bit_vector(7 downto 0). Как Вам известно, из курса САПР в базовой версии языка VHDL над данными типа bit_vector поддерживаются такие виды сдвиговых операций:

sll - логический сдвиг влево;

srl - логический сдвиг вправо;

sla - арифметический сдвиг влево;

sra - арифметический сдвиг вправо;

rol - циклический сдвиг влево;

ror - циклический сдвиг вправо.

Структура приведенных выше сдвиговых операций показана на Рис.Л1

Рис.Л1

Все сдвиговые операции являются двухместными. Это означает, что при их применении они могут использоваться в выражениях стоящих в правых частях операторов назначения значения сигналу или операторах присвоения значений переменным. Причем, 1-м операндом (левым операндом) в таких выражениях должен указываться сдвигаемый вектор, а 2-м операндом (правым операндом) должна быть величина целого ( integer) типа, отождествляемая с количеством сдвигов.

Заметим, что в данном проекте все данные можно было представить типом std_logic_vector(7 downto 0) и оформить проект в версии языка VHDL’93. В таком варианте проекта следовало бы включить в заголовок проекта строки (В выше приведенном проекте они закомментированы):

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.Numeric_Bit.all;

Включение в проект этих строк необходимо по той причине, что все сдвиговые операции над данными типа std_logic_vector(7 downto 0) не поддерживаются базовой версией языка.

Все сдвиговые операции над данными типа std_logic_vector(7 downto 0) определены пакете Numeric_Bit библиотеки IEEE.

Временная диаграмма работы проекта.

4. Домашнее задание по материалам лекции:

Разработать и промоделировать работу проекта криптографического процессора оперирующего с данными типа std_logic_vector(7 downto 0) . При разработке проекта использовать операции циклического сдвига. Исходные данные для шифрования:

Шифруемый текст - Двоичные ASCII коды символов фамилии студента;

Коды ключей - Десятичные ASCII коды символов фамилии студента;