3.6. Триггеры – устройства с памятью

Триггерами называют большой класс функциональных устройств имеющих два статически устойчивых состояния. Имеются десятки типов триггеров, отличающихся схемами, выполняемыми функциями элементной базой и другими параметрами. Общими свойствами триггеров является способность неограниченно долго сохранять каждое из устойчивых состояний и практически мгновенно переключаться из одного состояния в другое под воздействием управляющих сигналов.

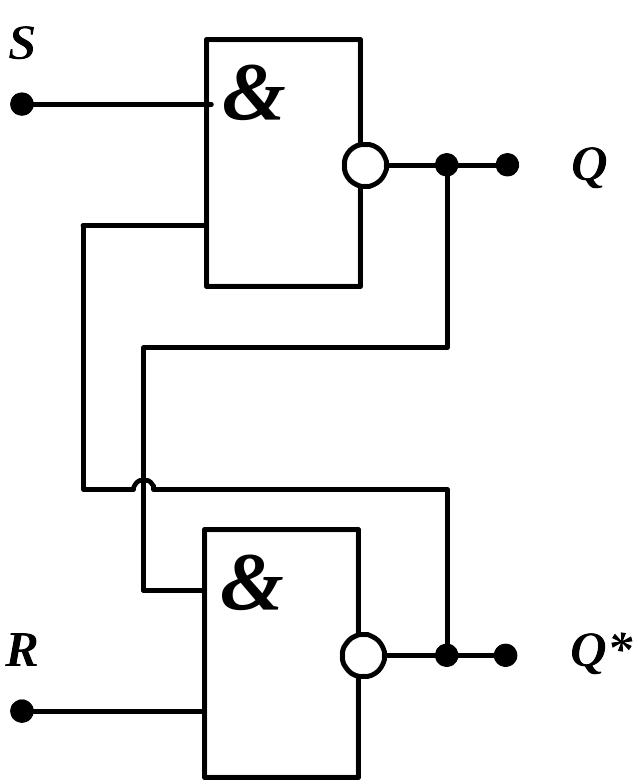

Наиболее широкое применение получили статические триггеры, в которых устойчивые состояния различаются уровнем постоянного потенциала. Основу таких триггеров составляет бистабильная ячейка на двух логических элементах И-НЕ (возможна реализация на ИЛИ-НЕ), охваченных перекрёстной положительной обратной связью, получившая название – асинхронный RS-триггер. Выходы и свободные входы логических элементов образуют соответственно выходы и входы триггера.

Выходные

сигналы в триггере взаимно инверсны

(противоположны в логическом смысле).

Один выход называют «прямым», а другой

«инверсным», и обозначаются они

соответственно

![]() и

и

![]() (или Q*)

(рис.3.7). Состояние триггера отождествляется

с сигналом на прямом

выходе:

говорят, что триггер находится в единичном

состоянии, когда Q

= 1, и в нулевом,

когда Q

= 0.

(или Q*)

(рис.3.7). Состояние триггера отождествляется

с сигналом на прямом

выходе:

говорят, что триггер находится в единичном

состоянии, когда Q

= 1, и в нулевом,

когда Q

= 0.

Рис.3.7.

Асихронный RS-триггер

Состояние,

когда оба выхода имеют ВЫСОКИЙ (или

НИЗКИЙ) уровень, является запрещённым

состоянием.

В момент подачи питания на вход R

необходимо подать кратковременный

нулевой импульс, а на вход S

постоянный единичный (ВЫСОКИЙ) уровень

для установки триггера в нулевое

состояние. В этом состоянии триггер

будет находиться до того момента, пока

на вход S

не придёт нулевой импульс (перепад

![]() ),

и «перебросит» триггер в единичное

состояние. Дальнейшее изменение сигнала

на входе S

будет игнорироваться триггером до тех

пор пока он вновь не будет переведён в

нулевое состояние по входу R.

),

и «перебросит» триггер в единичное

состояние. Дальнейшее изменение сигнала

на входе S

будет игнорироваться триггером до тех

пор пока он вновь не будет переведён в

нулевое состояние по входу R.

Асихронный RS-триггер широко применяется в схемах автоматики, например, в качестве запоминающего устройства первого срабатывания (блинкер) или устройства подавления дребезга контактов управляющих кнопок.

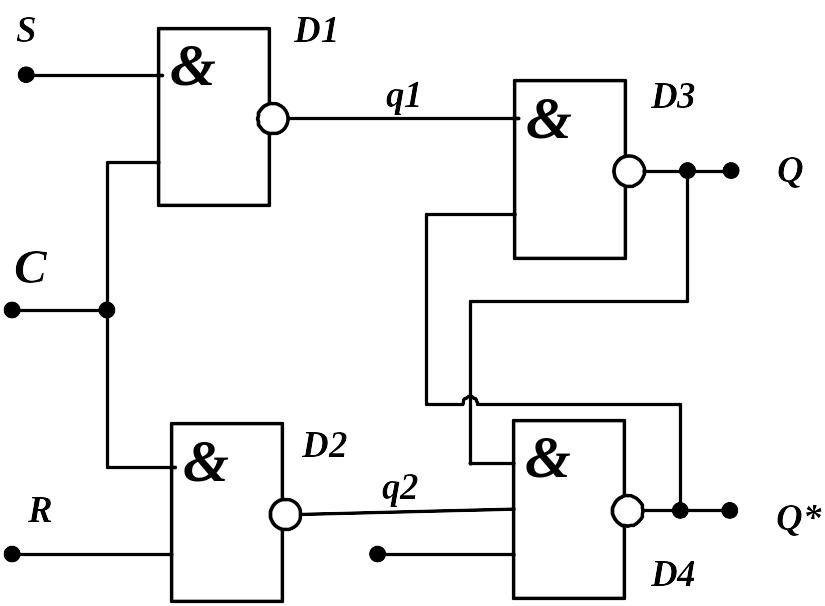

С

Рис.3.8.

Синхронный RS-триггер инхронные

триггеры получаются из асинхронных при

подключении к входам логических

элементов, имеющих синхронизирующий

(тактовый) вход С

(рис. 3.8). Логические элементы D3,

D4

образуют ячейку памяти (бистабильную

ячейку), а D1,

D2

— простейшую схему

управления. При отсутствии тактового

сигнала (С = 0)

элементы D1

и D2

закрыты, внутренние сигналы q1

= q2

= 1 и имеет место режим хранения информации.

Информация с входов S

и R

может быть передана в триггер только

при единичном значении сигнала на

тактовом входе С.

При наличии сигнала логической единицы

на входе S

(S=1)

в триггер записывается единица (Q=1).

При наличии сигнала логической единицы

на входе R

(R=1)

в триггер записывается ноль (Q=0).

Третий вход элемента D4

(рис.3.8) может или отсутствовать, или

быть использован для дополнительной

установки в нулевое состояние.

инхронные

триггеры получаются из асинхронных при

подключении к входам логических

элементов, имеющих синхронизирующий

(тактовый) вход С

(рис. 3.8). Логические элементы D3,

D4

образуют ячейку памяти (бистабильную

ячейку), а D1,

D2

— простейшую схему

управления. При отсутствии тактового

сигнала (С = 0)

элементы D1

и D2

закрыты, внутренние сигналы q1

= q2

= 1 и имеет место режим хранения информации.

Информация с входов S

и R

может быть передана в триггер только

при единичном значении сигнала на

тактовом входе С.

При наличии сигнала логической единицы

на входе S

(S=1)

в триггер записывается единица (Q=1).

При наличии сигнала логической единицы

на входе R

(R=1)

в триггер записывается ноль (Q=0).

Третий вход элемента D4

(рис.3.8) может или отсутствовать, или

быть использован для дополнительной

установки в нулевое состояние.

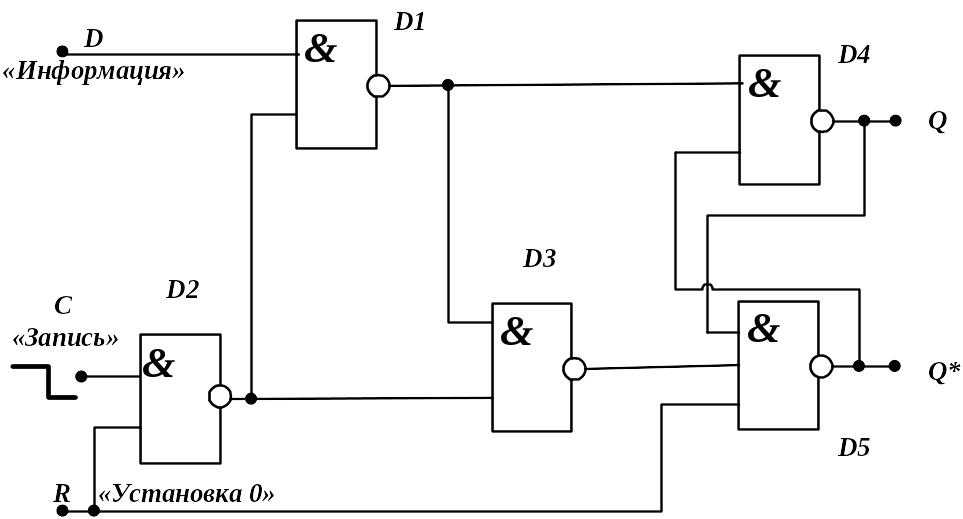

Н а

основе синхронного RS-триггера

легко получить тактируемый D-триггер,

предназначение которого – запоминать

один бит информации в момент прихода

тактового импульса (рис.3.9).

а

основе синхронного RS-триггера

легко получить тактируемый D-триггер,

предназначение которого – запоминать

один бит информации в момент прихода

тактового импульса (рис.3.9).

П

Рис.3.9.

D-триггер

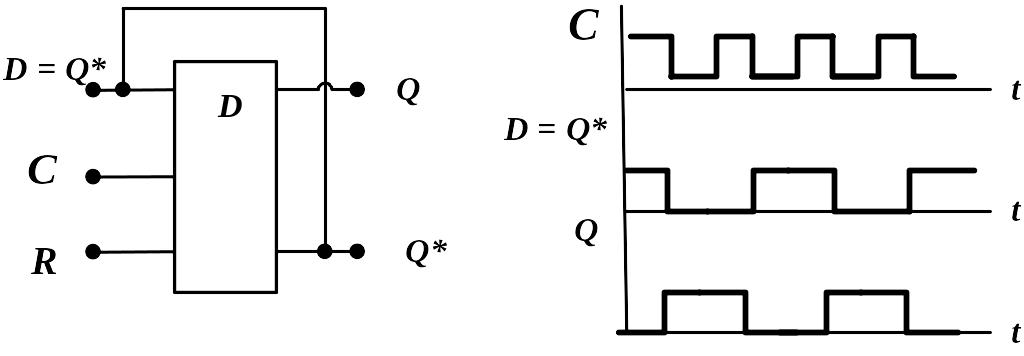

При соединении инверсного выхода Q* c входом D «Информация» D-триггер преобразуется в счётный триггер. На рис.3.10. приведена схема соединения и диаграммы работы счетного триггера, который в дальнейшем будем обозначать буквами СТ.

Рис.3.10.

D-триггер

с обратной связью (счетный триггер СТ)

и диаграммы его работы

Из диаграмм видно, что при приходе первого импульса на вход С (перепад ) триггер перебрасывается в состояние Q=1 (Q*=0), при приходе второго импульса на вход С (второй перепад ) триггер перебрасывается в состояние Q=0 (Q*=1), приходе третьего пять в состояние Q=1 (Q*=0) и т. д.

На основе счетных триггеров созданы счетчики импульсов, которые будут рассмотрены в следующей главе.

-