- •Розділ 5 інтерфейс пристроїв введення-виведення

- •5.1. Функції інтерфейсу введення-виведення

- •5.2. Програмований паралельний інтерфейс

- •5.3. Програмований інтерфейс клавіатури та індикації

- •5.4. Програмований таймер

- •5.5. Архітектура і функціональні можливості контролера прямого доступу до пам'яті

- •5.6. Програмований послідовний інтерфейс

- •5.7. Програмований контролер переривань

- •5.8. Приклад розробки мікропроцесорної системи

Розділ 5 інтерфейс пристроїв введення-виведення

5.1. Функції інтерфейсу введення-виведення

Одним з найважливіших завдань проектування МПС є організація взаємодії із зовнішніми пристроями — джерелами і приймачами даних. Прикладами пристроїв введення-виведення (ПВВ), що є як джерелами, так і приймачами інформації, є накопичувачі на гнучких і твердих магнітних дисках. До пристроїв введення належать перемикачі, клавіатура, аналого-цифрові перетворювачі (АЦП), датчики двійкової інформації, а до пристроїв виведення — індикатори, світлодіоди, дисплеї, друкувальні пристрої, цифроаналогові перетворювачі (ЦАП), транзисторні ключі, реле, комутатори. Пристрої введення-виведення відрізняються розрядністю даних, швидкодією, протоколами, тобто визначеним порядком обміну, керуючими сигналами. Дані у ПВВ змінюються у довільний або чітко визначений момент часу. З'єднання ПВВ з системною шиною МПС здійснюється за допомогою інтерфейсу введення-виведення, який узгоджує ПВВ з системною шиною МПС. Як правило, інтерфейс складається з одного або кількох портів введення-виведення та схем керування ними.

Під час проектування інтерфейсу введення-виведення треба забезпечити:

• зберігання інформації, яка надходить від ПВВ;

• доступ до інформації з боку МП;

• керування обміном;

• перетворення форматів даних.

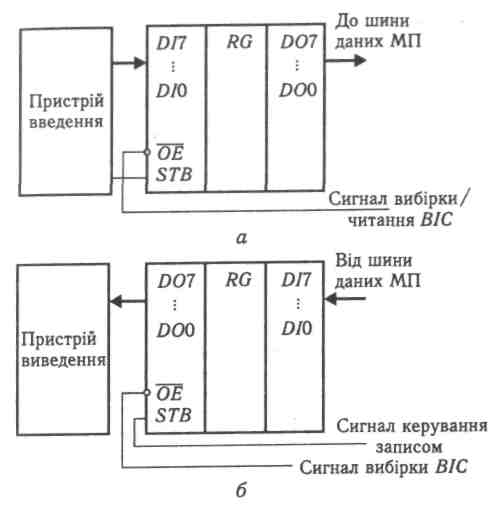

Зберігання інформації і доступ до неї з боку МП. Введення і виведення інформації виконується за допомогою портів введення-виведення, які є 8- або 16-розрядними регістрами зі схемами вибірки та керування читанням-записом. Як порти можуть бути використані буферні регістри, наприклад і8282, і8285, КР580ИР82, КР589ИР12, КР580ВВ55. Використання регістра КР580ИР82 для з'єднання відповідно з пристроєм введення та пристроєм виведення показано на рис. 5.1, а і 6.

Рис. 5.1. Використання регістра КР580ИР82 для з'єднання: а - з пристроєм введення; б — з пристроєм виведення

Якщо регістр використовується

як порт введення (рис. 5.1, а),

то дані від пристрою введення надходять

у регістр по лініях D17-D10

і записуються за стробом STB.

Вихідні дані DO7—

DO0 порту

надходять у МПС по шині даних. МП формує

також сигнал керування читанням і

вибіркою порту, який надходить на вхід

![]() .

Якщо регістр

використовується як порт виведення

(див. рис. 5.1, б), то дані від МП надходять

по шині даних на входи D17-D10

порту та супроводжуються

сигналами керування записом і вибірки

ВІС. Вихідні дані DO7—DO0

порту надходять у пристрій

виведення.

.

Якщо регістр

використовується як порт виведення

(див. рис. 5.1, б), то дані від МП надходять

по шині даних на входи D17-D10

порту та супроводжуються

сигналами керування записом і вибірки

ВІС. Вихідні дані DO7—DO0

порту надходять у пристрій

виведення.

Введення або виведення даних можна здійснювати двома способами:

• з використанням окремого адресного простору ПВВ;

• з використанням спільного з пам'яттю адресного простору, тобто з відображенням на пам'ять.

У першому випадку введення і виведення даних виконується за командами IN та OUT (див. табл. 2.11).

Приклад 5.1. Виконати виведення даних на 16-розрядний порт з адресою 1000Н.

Адреса порту займає два байти, тому для адресації порту слід використати непряму регістрову адресацію. Для цього треба адресу 1000Н занести у регістр DX, а потім виконати команду виведення:

MOV DX, 1000Н |

Занести у DX число 1000Н |

OUTDX,AX |

Вивести вміст АХ на 16-розрядний порт виведення з адресою, яка знаходиться у DX, тобто АХ→PI6(DX). |

Під час виконання команди OUT DX, АХ на лініях А15 — А0 шини адреси з'являється адреса порту:

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

=1000Н |

установлюється низький рівень

сигналу запису введення-виведеня

![]() ,

і вміст акумулятора АХ

передається на 16-розрядну

шину даних. Для фіксації даних (умісту

АХ) треба

використати два 8-розрядних порти, один

з яких з'єднаний з молодшою половиною

шини даних, а другий — зі старшою. Сигнали

керування записом і вибірки подаються

паралельно на два порти.

,

і вміст акумулятора АХ

передається на 16-розрядну

шину даних. Для фіксації даних (умісту

АХ) треба

використати два 8-розрядних порти, один

з яких з'єднаний з молодшою половиною

шини даних, а другий — зі старшою. Сигнали

керування записом і вибірки подаються

паралельно на два порти.

Приклад 5.2. Виконати введення даних з 8-розрядного порту з адресою 32Н.

Введення даних здійснюється за командою введення:

IN AL, 32Н; AL- Р8(32Н).

Дії МП у цьому випадку

аналогічні наведеним у прикладі 5.1.

Відмінність полягає лише в тому, що

активним стає сигнал

![]() читання введення-виведення,

і передавання інформації здійснюється

від порту до МП по молодшій половині

шини даних D7

— D0.

читання введення-виведення,

і передавання інформації здійснюється

від порту до МП по молодшій половині

шини даних D7

— D0.

За другим способом адреси портів розташовуються у спільному з пам'яттю адресному просторі, і звернення до портів не відрізняється від звернення до комірки пам'яті.

Сигнали вибірки ВІС (див. рис. 5.1, б) конкретних портів формуються за допомогою дешифраторів. Адреса 16-розрядного порту Р16 має бути парною, щоб звернення до неї відбулося за один цикл шини. Адреси 8-розрядних портів введення-виведення Р8 можуть бути будь-якими (парними, непарними), але за парної адреси 8-розрядні порти слід з'єднати з молодшою половиною шини даних D1—D0, а за непарної — зі старшою половиною D15 — D8.

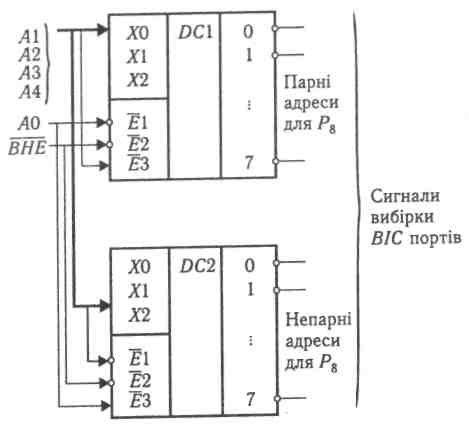

Приклад 5.3. Розробити функціональну схему дешифратора (рис. 5.2) на ВІС К155ИД7 для адресації восьми 8-розрядних і восьми 16-розрядних портів, причому адреси 8-розрядних портів обрати непарними, а адреси 16-розрядних — парними.

Схема містить два ВІС дешифраторів DC1 і DC2. Із виходів дешифраторів сигнали надходять на входи відповідних портів. Тому ця схема (див. рис. 5.2) дає змогу адресувати 16 портів. Усі вихідні сигнали 0 — 7 ВІС мають Н-рівні, якщо не забезпечене надходження сигналів L-рівня на інверсні входи дозволу Е1 і Е2 та сигналу Н-рівня на вхід ЕЗ. Інакше сигнал на виході DC, двійковий код номера якого визначається кодом на інформаційних входах DC Х2, Х1, Х0, є актив ним, тобто має L-рівень. Сигнали на інших виходах мають Н-рівень. Цей принцип роботи DC дає змогу в будь-який момент роботи МП звернутися лише до одного з портів. Визначимо адреси портів.

Рис. 5.2. Функціональна схема дешифратора портів

Низькі рівні на виході DCX з'являються,

якщо значення сигналів на адресних

лініях А4=1, А0=0, і сигнал вибірки

старшого банку

![]() .

Сигнал на виході 0 DC1 буде

активним (L-рівень) для адреси

.

Сигнал на виході 0 DC1 буде

активним (L-рівень) для адреси

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

0 |

0 |

0 |

0 |

=0010Н, |

на виході 1 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

1 |

0 |

0 |

1 |

0 |

=0012Н, |

на виході 2 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

1 |

0 |

1 |

0 |

0 |

=0014Н, |

........................................................................................................................................................ |

||||||||||||||||

на виході 7 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

0 |

0 |

1 |

1 |

=001ЕН |

Низькі рівні на виході DC2 з’являються якщо А4=0, А4=1, . Сигнал на виході 0 DC2 буде активним (L-низикий рівень) для адреси

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

0 |

0 |

0 |

1 |

=0001Н, |

на виході 1 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

0 |

0 |

1 |

1 |

=0003Н, |

на виході 2 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

1 |

0 |

1 |

0 |

0 |

=0014Н, |

........................................................................................................................................................ |

||||||||||||||||

на виході 7 - для адреси |

||||||||||||||||

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

1 |

1 |

1 |

1 |

=001FН |

Зазначимо, що 8-розрядні порти з непарними адресами мають бути з'єднаними зі старшою половиною шини даних D15—D8.

Керування обміном. Відомо три способи керування обміном:

• програмний обмін;

• обмін з перериванням;

• обмін у режимі прямого доступу до пам'яті.

Програмний обмін ініціюється МП і здійснюється під

його керуванням. Розрізняють простий програмний обмін та програмний обмін за стробом готовності. За простого програмного обміну вважають, що ПВВ у будь-який момент готовий до обміну за командами IN або ОUT. Під час обміну за стробом готовності ПВВ сповіщає про свою готовність до обміну стробом. Наприклад, видача 8-розрядних даних супроводжується дев'ятим бітом — стробом. У процесі такого обміну схема інтерфейсу містить тригер або порт керування для зберігання інформації про готовність зовнішнього пристрою до обміну. Процесор опитує відповідний розряд порту керування для визначення стану готовності зовнішнього пристрою.

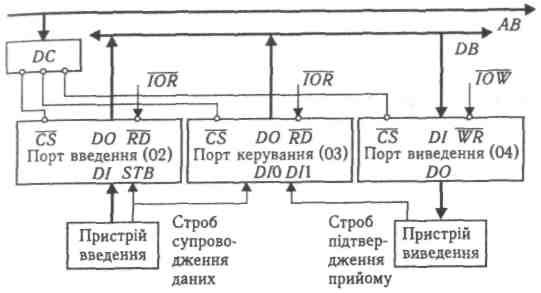

Приклад 5.4. Розробити функціональну схему введення і виведення 8-розрядних даних за стробом готовності. Адреса порту введення — 02H, порту керування — 03H, порту виведення — 04H.

Функціональну схему обміну за стробом готовності зображено на рис. 5.3. Схема містить: пристрій введення, з'єднаний з портом введення; пристрій виведення, з'єднаний з портом виведення; порт керування для зберігання сигналів готовності пристроїв введення і виведення. Пристрій введення має вісім інформаційних вихідних ліній та одну вихідну лінію стробу супроводження даних. Поява цього стробу сигналізує про те, що дані на інформаційних лініях є дійсними (коректними). Пристрій виведення має вісім інформаційних вхідних ліній та одну вихідну лінію стробу підтвердження приймання даних. Поява цього стробу сигналізує про те, що дані прийняті пристроєм і МП може передавати нову порцію даних. Порт керування зберігає інформацію про строби від двох пристроїв.

Програма введення за стробом готовності має такий вигляд:

М1: |

IN AL, 03 AND AL, 00000001В ; JZ M1 1N AL, 02 ; |

AL порт керування (адреса 03) Маскування всіх розрядів, крім D0 Якщо D0 = 0 (порт не готовий), то на М1, інакше — введення інформації з порту введення (адреса 02) |

Програма виведення за стробом готовності:

М2: |

IN AL,03 |

AL порт керування (адреса 03) |

|

AND AL, 00000010B |

Маскування всіх розрядів, крім D1 |

|

JZ M2 |

Якщо D1=0 (порт не готовий), то на М2 |

|

OUT 04, AL |

інакше — виведення інформації на порт ; виведення (адреса 04) |

Рис. 5.3. Схема введення-виведення даних за стробом готовності

Якщо ПВВ має вбудований апаратний засіб для визначення готовності для обміну, то про стан пристрою свідчить прапорець готовності READY або прапорець готовності-зайнятості READY/BUSY. Інформація про готовність пристроїв належить до статусної інформації і входить до складу слова стану пристрою. Іноді стан готовності та зайнятості ідентифікується окремими прапорцями — READY і BUSY. Прапорець READY замінює біт порту керування (див. рис. 5.3).

Схему алгоритму програмного обміну даними за значенням прапорця READY наведено на рис. 5.4.

Якщо ПВВ не готовий до обміну, то МП знаходиться у режимі програмного очікування готовності зовнішнього пристрою, виконуючи команди блоків 1 і 2. Після виявлення стану готовності МП передає дані за командами блока З, а потім працює з продовженням основної програми. На читання статусної інформації та її аналіз МП витрачає кілька циклів роботи, що призводить до непродуктивних втрат його часу. Недоліками програмного обміну за стробом готовності є те, що цей спосіб обміну інформацією не дає змоги зовнішнім пристроям ініціювати обмін. Перевага програмного обміну полягає у простоті реалізації та у тому, що немає потреби у додаткових апаратних засобах.

Рис. 5.4. Алгоритм програмного введення

Програмний обмін використовується для обміну з ПВВ, продуктивність яких менша, ніж продуктивність МП.

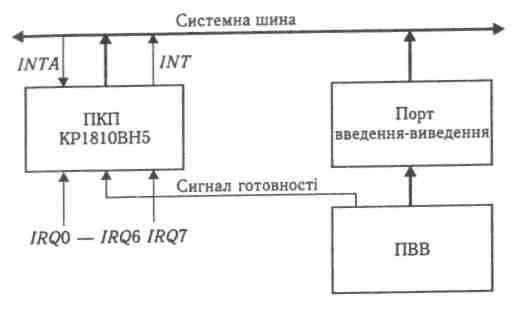

Обмін за перериванням ініціюється ПВВ і здійснюється під керуванням МП. У цьому разі сигнал готовності ПВВ до обміну використовується як запит переривання і надходить до програмованого контролера переривань (ПКП) (рис. 5.5). Введення або виведення здійснюється за підпрограмою оброблення запиту переривання.

Пристрій введення-виведення формує сигнал готовності IRQ, коли він готовий до обміну. Програмований контролер переривання (див. рис. 5.5) здатний сприйняти 8 сигналів IRQ7 — IRQ0. На рис. 5.5 сигнал готовності ПВВ надходить на вхід IRQ6. Сигнал готовності ПВВ — це вихідний сигнал тригера, який фіксує стан готовності READY. На виході програмованого контролера переривань асинхронно з діями МП формується сигнал INT. Заздалегідь не відомо, в який момент та які периферійні пристрої ініціюють переривання. Реагуючи на сигнал INT, МП перериває виконання програми, ідентифікує пристрій, переходить до підпрограми обслуговування переривань роботи цього пристрою, а після її завершення відновлює виконання перерваної програми. За командою ІNT уміст програмованого лічильника та прапорців автоматично запам'ятовується у стеку. Вміст акумулятора та РЗП треба занести у стек за допомогою команди PUSH у підпрограмі обробки переривання.

У кожному МП реалізовано особливу структуру системи переривань. Однак загальна послідовність обміну за перериванням містить такі дії:

• ПВВ генерує сигнал готовності, який викликає появу сигналу переривання, що подається на вхід INT МП;

• МП завершує виконання поточної команди і, якщо переривання дозволені (не замасковані), формує сигнал І NT A підтвердження переривання;

• МП здійснює запам'ятовування вмісту акумулятора, програмованого лічильника, РЗП у стеку;

• МП ідентифікує пристрій, що зумовив переривання, і виконує відповідну підпрограму обслуговування переривання;

• за допомогою команди POP відновлюється значення вмісту акумулятора та РЗП зі стеку;

• за командою повернення з переривання RET, що є останньою командою підпрограми обслуговування переривання, відновлюються значення програмованого лічильника та прапорців і триває виконання перерваної програми.

Рис. 5.5. Схема обміну за перериванням

Рис. 5.6. Схема обміну в режимі ПДП

Обмін за перериванням продуктивніший, ніж програмний обмін, оскільки не потребує часу для опитування стану готовності ПВВ до обміну.

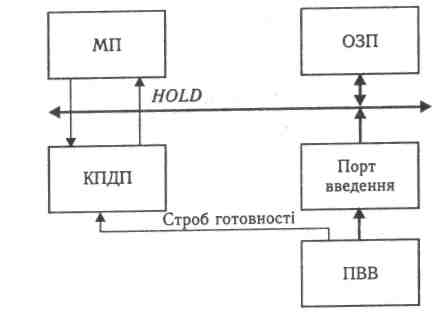

Обмін у режимі прямого

доступу до пам'яті ініціюється

ПВВ, здійснюється під керуванням

контролера прямого доступу до пам'яті

(КПДП) без участі МП. За необхідності

обміну між ПВВ і пам'яттю немає потреби

у пересиланні даних через МП. Дані

за допомогою КПДП пересилаються

безпосередньо з ПВВ у пам'ять або навпаки.

Прямий доступ до пам'яті під час виконання

операцій введення-виведення дає змогу

значно збільшити швидкість передавання

даних і підвищити ефективність

використання засобів МП. Схему обміну

в режимі ПДП зображено на рис. 5.6. Контролер

прямого доступу приймає запит від

ПВВ, формує сигнал запиту захоплення

ший МП HOLD

і, отримавши від МП

дозвіл HLDA,

формує адреси пам'яті

та керуючі сигнали

![]() ,

— у разі читання пам'яті,

або

,

— у разі читання пам'яті,

або

![]() ,

— у разі запису в

пам'ять.

,

— у разі запису в

пам'ять.

Інформацію про область пам'яті, що використовується для обміну у вигляді початкової адреси і довжини масиву, завантажують у КПДП під час програмування. Продуктивність обміну в режимі ПДП є найвищою.

Перетворення форматів даних. Якщо розрядність даних, з якими оперує МП, менша, ніж розрядність даних, з якими оперує ПВВ, то для узгодження розрядності збільшується кількість портів введення-виведення. Якщо розрядність даних, з якими оперує МП, більша, ніж розрядність даних, з якими оперує ПВВ, то для узгодження розрядності виконується пакування даних, отриманих з кількох джерел, в одне слово потрібної розрядності або доповнення нулями. Для перетворення послідовного коду на паралельний і навпаки використовують контролер послідовного обміну.