- •Розділ 4 побудова модулів пам'яті мікропроцесорних систем

- •4.1 Класифікація систем пам'яті

- •4.2. Побудова модулів постійного запам'ятовувального пристрою

- •4.3. Побудова модулів оперативного запам'ятовувального пристрою статичного типу

- •4.4. Побудова модулів оперативного запам'ятовувального пристрою динамічного типу

- •4.5. Принципи організації кеш-пам'яті

- •4.6. Принципи організації стекової пам'яті

4.4. Побудова модулів оперативного запам'ятовувального пристрою динамічного типу

У мікросхемах ОЗП динамічного типу елементом пам'яті є конденсатор р-n-переходу МДН-траизистора. Заряджений стан конденсатора вважається станом логічної одиниці, розряджений — станом логічного нуля. Такі елементи пам'яті не можуть тривалий час зберігати свій стан і тому потребують додаткового обладнання для забезпечення періодичного відновлення (регенерації) інформації. Тривалість вибірки для динамічного ОЗП становить 70—200 нc. Порівняно з ОЗП статичного типу ОЗП динамічного типу характеризуються більшою інформаційною ємністю, що зумовлюється меншою кількістю компонент в одному елементі пам'яті, та меншими швидкодією (пов'язано з потребою заряджання і розряджання конденсатора), потужністю споживання і вартістю. Переважно модулі оперативної пам'яті сучасних МПС реалізуються на базі ВІС ОЗП динамічного типу.

Оперативні ЗП динамічного

типу (див. розд. 9, кн. 2) працюють у

таких режимах: запису, зчитування,

зчитування — модифікації—запису,

сторінкового запису, сторінкового

зчитування, регенерації. Для

забезпечення адресування всієї ємності

пам'яті використовують мультиплексування

адресних сигналів у часі. Спочатку

відбувається зчитування або запис

даних, адреса яких визначається т

молодшими розрядами

шини адреси, що супроводжується сигналом

строба

![]() (Row

Address

Strobe

— строб адреси рядка).

Після цього відбувається зчитування

або запис даних, адреса яких визначається

т старшими

розрядами шини адреси, що супроводжується

сигналом строба

(Row

Address

Strobe

— строб адреси рядка).

Після цього відбувається зчитування

або запис даних, адреса яких визначається

т старшими

розрядами шини адреси, що супроводжується

сигналом строба

![]() (Column

Address

Strobe

— строб адреси стовпця).

Зчитування інформації здійснюється за

заднім фронтом сигналу

за

=

1, запис — за заднім

фронтом сигналу

за

=

0. Режим

зчитування—модифікації—запису

полягає у зчитуванні інформації з

подальшим записом в один і той самий

елемент пам'яті. Сторінкові режими

запису і зчитування реалізуються

зверненням до ВІС за адресою рядка з

вибіркою елемента пам'яті цього рядка

зміною адрес стовпців. Регенерація

інформації здійснюється зверненням

до кожного з рядків, при цьому формується

адреса рядка і сигнал

, а сигнал

дорівнює логічній

одиниці. Процес регенерації припиняється

після звернення МП до ОЗП. У цьому випадку

обробляється вимога МП, після чого

режим регенерації триває з тієї адреси,

на якій він був припинений.

(Column

Address

Strobe

— строб адреси стовпця).

Зчитування інформації здійснюється за

заднім фронтом сигналу

за

=

1, запис — за заднім

фронтом сигналу

за

=

0. Режим

зчитування—модифікації—запису

полягає у зчитуванні інформації з

подальшим записом в один і той самий

елемент пам'яті. Сторінкові режими

запису і зчитування реалізуються

зверненням до ВІС за адресою рядка з

вибіркою елемента пам'яті цього рядка

зміною адрес стовпців. Регенерація

інформації здійснюється зверненням

до кожного з рядків, при цьому формується

адреса рядка і сигнал

, а сигнал

дорівнює логічній

одиниці. Процес регенерації припиняється

після звернення МП до ОЗП. У цьому випадку

обробляється вимога МП, після чого

режим регенерації триває з тієї адреси,

на якій він був припинений.

Для керування ОЗП динамічного типу використовують контролери динамічної пам'яті, наприклад, К1810ВТ03, К1810ВТ02, i8207, які формують адресні та керуючі сигнали у режимах роботи і регенерації, а також здійснюють арбітраж, тобто розв'язання конфліктів між запитами на регенерацію і звернення до пам'яті. Контролер формує також сигнал готовності блока динамічної пам'яті до обміну.

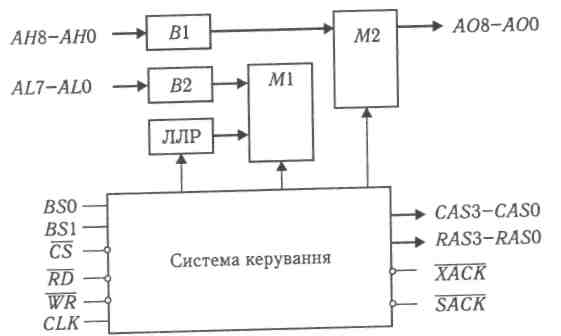

Контролер динамічної пам'яті i8207 (рис. 4.7) призначений для керування чотирма ВІС ОЗП динамічного типу по 512 Кбайт кожний. Він складається з адресних буферів В1 і В2, лічильника рядків регенерації (ЛРР), двох мультиплексорів М1 і М2 та системи керування. Система керування аналізує вхідні сигнали і здійснює керування всіма блоками контролера.

Під час виконання команд

читання-запису пам'яті контролер

забезпечує з'єднання з виходами АО8—АО0

спочатку з молодшою, а

потім зі старшою половинами адреси,

формування стробувальиих сигналів

і

для кожної з чотирьох

ВІС пам'яті, а також сигналу

![]() (Write

Enable

—дозвіл запису). У

режимі регенерації контролер забезпечує

з'єднання з виводами АО8—АО0

виходів лічильника

рядків регенерації і формування сигналу

.

(Write

Enable

—дозвіл запису). У

режимі регенерації контролер забезпечує

з'єднання з виводами АО8—АО0

виходів лічильника

рядків регенерації і формування сигналу

.

Рис. 4.7. Структурна схема контролера динамічної пам'яті i8207

Таблиця 4.2. Вибір ВІС динамічної пам'яті

Сигнал |

Блок пам'яті |

|

SS1 |

BS0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

2 |

1 |

1 |

3 |

Вибір однієї з чотирьох ВІС пам'яті здійснюється сигналами BS1 — BS0 ( табл. 4.2).

Контролер формує сигнал

![]() наприкінці циклу

читання-запису, вказує на закінчення

циклу взаємодії з

центральним процесором та сигнал

наприкінці циклу

читання-запису, вказує на закінчення

циклу взаємодії з

центральним процесором та сигнал

![]() на початку циклу звернення

до пам'яті.

на початку циклу звернення

до пам'яті.

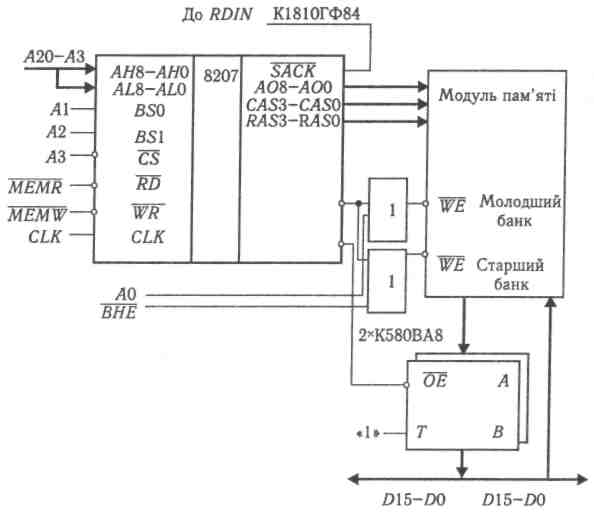

Використання цих сигналів показано на прикладі під'єднання контролера i8207 із системною шиною 16-розрядного процесора (рис. 4.8).

На виході формується сигнал логічного нуля тоді, якщо контролер виконує такти регенерації інформації в динамічному ОЗП. Сигнал використовується як стробувальний сигнал для керування шинними формувачами модуля пам'яті. У цьому прикладі використано два шинних формувачі К580ВА86 (i8286), оскільки шина даних є 16-розрядною.

Рис. 4.8. З'єднання контролера динамічної пам'яті з системною шиною

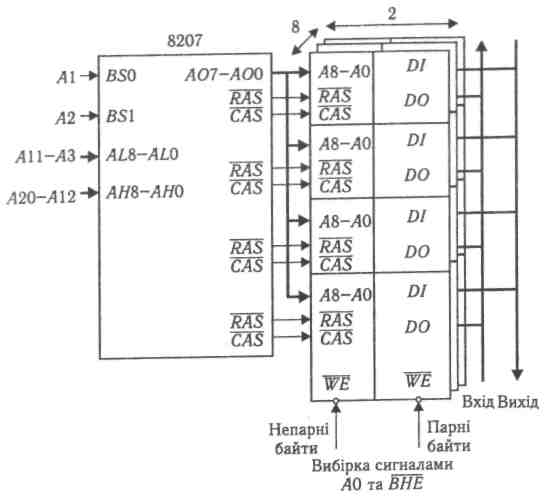

Рис. 4.9. Система динамічної пам'яті

Схему модуля динамічної пам'яті 16-розрядного процесора зображено на рис. 4.9.

Контролер динамічної пам'яті фактично виконує роль інтерфейсу модуля пам'яті та шини процесора. Динамічну пам'ять організовано у вигляді двох банків, кожний з яких складається з чотирьох блоків ємністю по 512 Кбайт. Загальна ємність пам'яті дорівнює 2 Мбайт. Шина адреси процесора з'єднана з контролером. Лінії А1 і А0 під'єднуються до входів вибирання банку BS0, BS1, біти A11— A3 є адресою рядка, а біти A20 —A12 — адресою колонки динамічної пам'яті.