- •Розділ 4 побудова модулів пам'яті мікропроцесорних систем

- •4.1 Класифікація систем пам'яті

- •4.2. Побудова модулів постійного запам'ятовувального пристрою

- •4.3. Побудова модулів оперативного запам'ятовувального пристрою статичного типу

- •4.4. Побудова модулів оперативного запам'ятовувального пристрою динамічного типу

- •4.5. Принципи організації кеш-пам'яті

- •4.6. Принципи організації стекової пам'яті

4.3. Побудова модулів оперативного запам'ятовувального пристрою статичного типу

Елементом пам'яті ОЗП статичного типу є тригер. Кожний елемент пам'яті має свою адресу. Для того щоб зчитати інформацію з елемента пам'яті або записати в нього нове значення, його треба обрати поданням на ВІС ОЗП відповідної адреси . Якщо запам'ятовувальний пристрій допускає звернення до будь-якого елемента пам'яті у довільному порядку, його називають ОЗП з довільною вибіркою (RAM — Random Access Memory — пам'ять з довільним доступом), див. розд. 9, кн. 2.

Існують ОЗП з інформаційною

ємністю

![]() біт (серії К541, К132) і з ємністю

біт (серії К541, К132) і з ємністю

![]() (К537, К581). Для введення інформації в ОЗП

першого типу використовують вхід D1

(Data

Input),

а для виведення — вихід

DО

(Data

Output).

Великі інтегральні

схеми ОЗП другого типу мають п

інформаційних

входів-виходів

(К537, К581). Для введення інформації в ОЗП

першого типу використовують вхід D1

(Data

Input),

а для виведення — вихід

DО

(Data

Output).

Великі інтегральні

схеми ОЗП другого типу мають п

інформаційних

входів-виходів

![]() .

Такий ОЗП припускає

читаиня-запис 8-розрядного коду. Керування

режимами (запису, зчитування,

зберігання) здійснюється за допомогою

сигналів

і

.

Такий ОЗП припускає

читаиня-запис 8-розрядного коду. Керування

режимами (запису, зчитування,

зберігання) здійснюється за допомогою

сигналів

і

![]() . Одиничний стан сигналу

визначає режим запису біта інформації

в елемент пам'яті, а нульовий — режим

зчитування біта інформації з елемента

пам'яті.

. Одиничний стан сигналу

визначає режим запису біта інформації

в елемент пам'яті, а нульовий — режим

зчитування біта інформації з елемента

пам'яті.

Розглянемо будову модуля ОЗП статичного типу для МПС з 8-розрядними процесорами, використовуючи ВІС ОЗП з інформаційною ємністю N × 1. Для цього слід нарощувати розрядність даних.

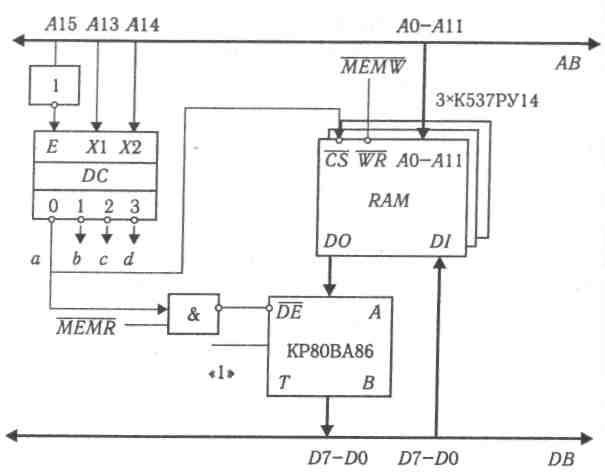

Приклад 4.3. Для МПС з 8-розрядним МП розробити схему модуля ОЗП з інформаційною ємністю 4К × 8 на базі ВІС К537РУ14 з інформаційною ємністю 4К × 1.

Для побудови модуля пам'яті

ємністю 4К×8

треба вісім ВІС ОЗП

К537РУ14, рис. 4.5. Оскільки такі ВІС не мають

входу сигналу ОЕ, тобто

під час записування інформації вони не

переходять у г-стан, слід використовувати

шинний формувач. У цьому разі використаємо

шинний формувач КР580ВА86, що з'єднує вихід

ВІС із шиною даних під час виконання

циклу ЧИТАННЯ ПАМ'ЯТІ,

= 0 та нульовому рівні

сигналів на входах

![]() і

.

Кожну з ВІС ОЗП з'єднано

з однією з ліній шини даних D7

— D0.

і

.

Кожну з ВІС ОЗП з'єднано

з однією з ліній шини даних D7

— D0.

Для мікросхем ОЗП, в яких під час записуваня інформації виходи переходять у високоімпедансний стан, шинний формувач не використовується, і виходи ВІС безпосередньо з'єднуються з шиною даних.

Отже, розрядність нарощується під'єднанням однієї ВІС ОЗП до кожної лінії шини даних. При цьому адресні входи для всіх ВІС ОЗП з'єднуються паралельно. Паралельно також з'єднуються входи керування і вибірки. Нарощування ємності ОЗП здійснюється аналогічно нарощуванню ємності ПЗП. На рис. 4.5 показано один з чотирьох можливих варіантів під'єднання модуля ОЗП — до виходу а дешифратора, інших трьох модулів ОЗП — до виходів b, с, d дешифратора.

Рис. 4.5. Нарощування розрядності модуля статичного ОЗП

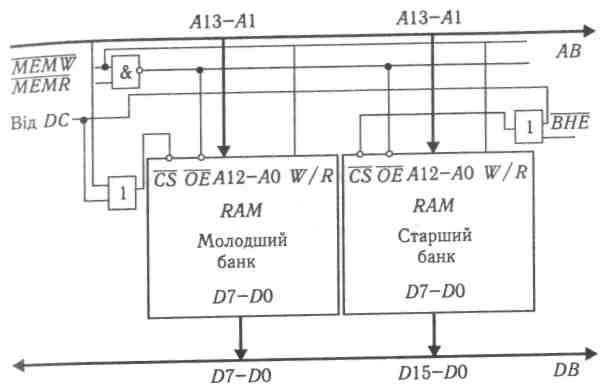

Розглянемо будову модуля оперативної пам'яті для МПС на основі 16-розрядних процесорів. Модуль ОЗП, так само, як і ПЗП, виконується у вигляді двох банків, під'єднаних відповідно до молодшої та старшої половин шини даних.

Приклад 4.4. Розробити схему модуля ОЗП інформаційною ємністю 16К × 16 для МПС із 16-розрядним МП.

У схемній реалізації модуля ОЗП має бути забезпечене читання-запис як 8-, так і 16-розрядних даних. Модуль ОЗП складається з двох банків — молодшого і старшого (рис. 4.6).

Адресні розряди A13—A1

з'єднані з адресними входами A12—

A0 обох

банків. Вибірка банків здійснюється

одиничним значенням сигналу на виході

дешифратора DC,

сигналами A0

для вибірки молодшого банку або

![]() (.Bus

High

Enable

— дозвіл старшого байта

шини) для вибірки старшого банку.

Одиничний рівень сигналу на виході DC

з'являється після

надходження на шину

адреси АВ відповідної

адреси ОЗП. Сигнал

або

(.Bus

High

Enable

— дозвіл старшого байта

шини) для вибірки старшого банку.

Одиничний рівень сигналу на виході DC

з'являється після

надходження на шину

адреси АВ відповідної

адреси ОЗП. Сигнал

або

![]() вказує на виконання

відповідно циклу ЧИТАННЯ ПАМ'ЯТІ або

ЗАПИС У ПАМ'ЯТЬ.

вказує на виконання

відповідно циклу ЧИТАННЯ ПАМ'ЯТІ або

ЗАПИС У ПАМ'ЯТЬ.

Рис. 4.6. Модуль ОЗП у 16-розрядних МПС

Комбінація значень сигналів A0 і визначає чотири можливих випадки звернення до пам'яті:

• вибірку байта за парною адресою;

• вибірку байта за непарною адресою;

• вибірку слова за парною адресою;

• вибірку слова за непарною адресою.

Під час вибірки байта за парною адресою A0 = 0, = 1. Байт з парною адресою передається по лініях D7 — D0, тобто здійснюється зчитування або запис байта. У разі запису байта у молодший банк інформація в старшому банку захищена від стирання, тобто одиничне значення сигналу ВНЕ забороняє звернення до старшого банку.

Під час вибірки байта за непарною адресою A0 = 1, = 0. Наприклад, за командою

MOV BL, BYTE PTR [10001H]

вміст комірки пам'яті з адресою DS:10001 H пересилається в молодшу половину 16-розрядного регістра ВХ, тобто у 8-розрядний регістр BL. При цьому вміст комірки пам'яті записується у розряди D15 — D8, тобто старшу половину шини даних, потім, у процесі виконання команди, на молодшу половину внутрішньої 16-розрядної шини МП, а після цього—в регістр BL. Цей процес, який називають маршрутизацією байта, відбувається автоматично і непомітно для програміста.

Під час вибірки слова за парною адресою - 0, A0 = 0. У цьому разі водночас обираються два банки, і 16-розрядне слово передається по лініях D15—D0 за один цикл шини.

Якщо слово має непарну адресу, його молодший байт розміщується у старшому банку пам'яті, а старший байт — у молодшому банку. У процесі вибірки слова за непарною адресою спочатку A0 = 1, = 0, і по лініях шини D15 — D8 передається молодший байт. Після цього генеруються сигнали A0=0, = 1, здійснюється інкремент (збільшення на одиницю) повної адреси А19—A0, старший байт слова передається з молодшого банку або в молодший банк по лініях шини D7—D0. Отже, вибірка слова за непарною адресою потребує два цикли шини. Тому слова доцільно розміщувати за парними адресами, особливо під час організації операцій зі стеком.