3.3 Особливості архітектури мікропроцесорів i386 та i486

Мікропроцесор i386. Перший 32-розрядний процесор i386 було створено у 1985 р. Він виконаний за технологією 1,5 мкм і містить 275 тис. транзисторів. Розрядність регістрів, шини даних та адреси дорівнює 32. Ємність пам'яті, що прямо адресується, становить 4 Гбайт. Процесор може працювати у трьох режимах — реальному, захищеному і віртуального процесора 8086 — V86. Допускається паралельна робота кількох віртуальних процесорів 8086 під керуванням операційної системи типу Windows, OS/2, Unix. Перемикання режимів відбувається швидше, ніж у МП i80286. Є механізми сторінкової адресації, які істотно підвищують ефективність роботи з пам'яттю понад 1 Мбайт навіть у межах DOS. Черга команд — 16 байт. Мікропроцесор i80386 має модифікації: DX — регістри, шини даних та адреси є 32-розрядними; SX — із зовнішньою 16-розрядною шиною даних та 24-розрядною шиною адреси; SL — відрізняється від модифікації SX зниженим енергоспоживанням та вбудованим контролером зовнішньої кеш-пам'яті на 16 — 64 Кбайт. До комплекту 3865L входить мікросхема 823605L — набір периферійних контролерів для ноутбуків. Основні характеристики процесорів 80 86 наведено у табл. 3.7.

Мікропроцесор i486. Цей процесор випустили у 1989 р. Він характеризується значно вищою швидкодією порівняно з мікропроцесором i8086. Мікропроцесор виконано за технологією 1 мкм; містить 1,2 млн транзисторів. Основні особливості МП i486 — наявність внутрішньої кеш-пам'яті, вбудованого математичного співпроцесора, сумісного за командами арифметичного співпроцесора І387. У МП i486 збільшено чергу команд, прискорено виконання операцій як у цілочисловому АЛП, так і в блоці математичного співпроцесора за рахунок архітектури, введено множення тактової частоти системної плати. У модифікаціях процесора 486DX2 внутрішня частота дорівнює подвоєній зовнішній, а в процесорах 486DX4 кратність може бути 2, 2,5, 3. Математичного співпроцесора у модифікаціях SX та в деяких модифікаціях SL немає. Залежно від модифікації процесори DX4 можуть працювати від джерела живлення 5 В та 3,3 В і мають режим SMM {System Management Mode), що дає змогу керувати енергоспоживанням.

Крім розглянутих вище процесорів фірми Intel (див. табл. 3.7) є аналогічні за технічними характеристикам процесори, які виготовляють фірми IBM, AMD, Cyrix, Texas Instruments. Так, процесор 386SLC — це поліпшений варіант процесора 386SX. Він має внутрішню кеш-пам'ять і характеризується прискореним виконанням операцій. Мікропроцесор 486SLC є варіантом процесора і486SX, а процесори SLC2/SLC3 здійснюють подвоєння (потроєння) зовнішньої частоти.

Таблиця 3.7. Основні характеристики процесорів 80 86 фірм і IBM

Процесор

|

Розрядність |

Ємність кеш-пам'яті, Кбайт |

Наявність співпроцесора

|

Частота процесора, МГц

|

||

регістрів |

шини даних |

шини адреси |

||||

8088 |

16 |

8 |

20 |

- |

- |

4,77-8 |

8086 |

16 |

16 |

20 |

- |

- |

5 |

286 |

16 |

16 |

24 |

- |

- |

6-25 |

386SX |

32 |

16 |

24 |

- |

- |

16-23 |

386SL |

32 |

16 |

24 |

- |

- |

25 |

386SLC |

32 |

16 |

24 |

8 |

- |

25-40 |

486SLC |

32 |

16 |

24 |

16 |

- |

25-40 |

486SLC2 |

32 |

16 |

24 |

16 |

- |

40-66 |

486SLC3 |

32 |

16 |

24 |

16 |

- |

75 |

386DX |

32 |

32 |

32 |

- |

- |

25-40 |

486DLC |

32 |

32 |

32 |

16 |

- |

25-40 |

486SX |

32 |

32 |

32 |

8 |

- |

16-33 |

486BL2 |

32 |

32 |

32 |

16 |

- |

40-66 |

486BL3 |

32 |

32 |

32 |

16 |

- |

75-100 |

486DX |

32 |

32 |

32 |

8 |

+ |

25-50 |

487SX |

32 |

32 |

32 |

8 |

+ |

25-50 |

486SL |

32 |

32 |

32 |

8 |

+ |

25-50 |

486DX2 |

32 |

32 |

32 |

8/16 |

+ |

40-80 |

486DX4 |

32 |

32 |

32 |

16 |

+ |

75-120 |

Процесори SCL2 і SL характеризуються зниженим енергоспоживанням і мають напругу живлення 3,3 В. Так, більшість процесорів фірми AMD мають знижені енергоспоживання (літера L у позначенні ВІС) і напругу живлення 3,3 В (літера V у позначенні МП), наприклад, процесор AMD 5X-133ADV — це варіант мікропроцесора i486 зі збільшеною частотою вчетверо та зниженою напругою живлення.

Внутрішня кеш-пам'ять. Починаючи з МП і486, застосовується внутрішнє роздільне видавання команд і даних (докладно принципи організації кеш-пам'яті розглянуто в п. 16.5). Якщо область, яка адресується, відображено у кеш-пам'яті (випадок попадання — cache hit), то запит на читання обслуговується лише кеш-пам'яттю без звернення до основної пам'яті. У разі запиту на запис спочатку модифікується інформація у кеш-пам'яті, а після цього, залежно від типу кеш-пам'яті, й основна пам'ять.

У перших процесорах і486 використовувався режим наскрізного запису Write Through, коли інформація одночасно записувалася як у буфер, так і в ОЗП. У новіших модифікаціях використано режим зворотного запису Write Back, який полягає у тому, що копія блока записується в ОЗП лише тоді, коли вміст його змінювався.

Заповнення рядка кеш-пам'яті процесор намагається виконати найшвидше — пакетним циклом з 32-бітовими передачами. Вибір рядка для заміщення новими даними здійснюється на підставі аналізу біта LRU (Least Recently Used), який виконується лише для кеш-промахів читання. У разі кеш-промахів запису заповнення рядків не відбувається.

Пакетний режим передачі даних. Пакетний режим передавання даних (Burst Mode) призначений для швидких операцій з рядками кеш-пам'яті. При цьому вміст чотирьох 32-роз-рядних комірок основної пам'яті пересилається в один рядок кеш-пам'яті або навпаки — вміст одного рядка кеш-пам'яті пересилається у чотири 32-розрядні комірки основної пам'яті. Оскільки рядок кеш-пам'яті процесора 486 має довжину 16 байт (128 біт), то для його пересилання треба чотири 32-розрядних циклів шини, впродовж кожного з яких відбувається пересилання вмісту однієї 32-розрядної комірки з основної пам'яті або 32 біт з кеш-пам'яті.

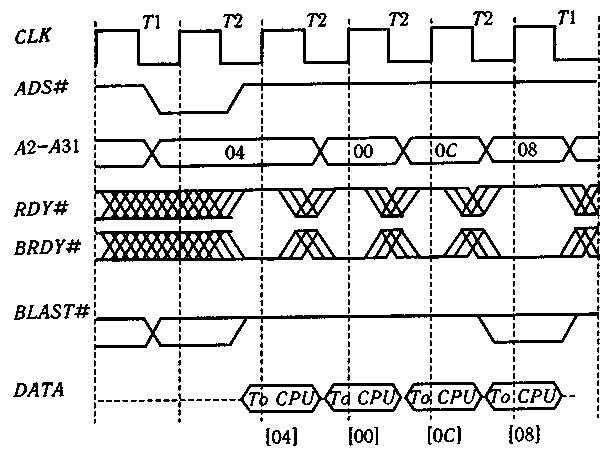

Розглянемо випадок пересилання вмісту чотирьох 32-розрядних комірок основної пам'яті в один рядок кеш-пам'яті (рис. 3.15). Під час зчитування вмісту 32-розрядної комірки розряди ЛО і А1 участі у формуванні адрес не беруть, оскільки вони означають положення кожного з чотирьох байтів у 32-розрядній комірці. Тому на рис. 3.15 подано значення розрядів А31—А2.

У першому такті П встановлюється адреса А31 — А2, сигнали ідентифікації типу циклу і формується строб ADS#. Цей такт виконується процесором так само, як і за звичайного передавання даних.

У наступному такті (Т2) передається перше 32-розрядне слово. При цьому сигнал BLASTU має значення L-рівня.

Рис. 3.15. Діаграма пересилання вмісту чотирьох 32-розрядних комірок пам'яті

Про завершення пакетного циклу процесор повідомляє зовнішньому пристрою сигналом BLASTtt, що набуває значення L-рівня в останньому такті передавання пакета. Якщо зовнішній пристрій підтримує пакетний режим, він генерує сигнал готовності до пакетного передавання BRDYU (замість сигналу RDY#). У цьому разі процесор продовжує цикл як пакетний, не вводячи такти Т1 адресації-ідентифікації (з сигналом ADS#), а відразу переходячи до передавання наступного 32-розрядного слова. Формуванням сигналу RDY# замість BRDY# зовнішній пристрій може у будь-який момент перервати пакетне передавання, і процесор продовжить її звичайними циклами. Для передавання 16 байт у пакетному режимі потрібно п'ять тактів шини (без тактів чекання) замість восьми тактів за звичайного режиму передавання.

Пояснимо чередування адрес 32-розрядних слів у пакетному режимі. Подамо адресу слова у такому вигляді:

А31-A4 |

AЗ |

A2 |

A1 |

A0 |

Довільні значення |

Номер 32-розрядного слова у пакетній посилці |

Номер байта у 32-розрядному слові |

||

Розряди А1та А0 у цій адресі дорівнюють нулю. Розряди A3, А2 визначають положення кожної з чотирьох 32-розряд-них комірок у рядку кеш-пам'яті завдовжки 128 біт. Розряди А31—А4 визначають адресу 32-розрядного слова в основній пам'яті, яке пересилається у кеш-пам'ять.

Рядок кеш-пам'яті вирівняно по межі 128-розрядних даних, його адреса має нульові значення розрядів A3 —А0. У пакетному передаванні завжди зчитуються дані, що відповідають одному рядку кеш-пам'яті, адреса якого кратна 128. Адреса першого 32-розрядного слова пакетної посилки кратною 128 може не бути. За нульових значень розрядів А31— А4 та А1, А0 адреса першого слова визначається розрядами А3, А2:

Передування адрес 32-розрядних слів у пакетному режимі залежно від адреси першого слова наведено у табл. 3.8.

Якщо перша адреса блока не збігається з межею рядка, то вона дорівнює 04H (див. рис. 3.15). Порядок чергування адрес при цьому відповідає другому рядку табл. 3.8, тобто дорівнює 04H, 00H, ОСH, 08H. Наведений порядок череду-вання адрес у пакетному режимі характерний для всіх процесорів Intel та сумісних з ними, починаючи з i486.

Таблиця 3.8. Послідовність зміни адрес у пакетному циклі

Адреса слова |

|||

першого |

другого |

третього |

четвертого |

0 |

4 |

8 |

С |

4 |

0 |

С |

8 |

8 |

С |

0 |

4 |

С |

8 |

4 |

0 |

Буфери відкладеного запису призначені для запаміято-вування даних у буфері тоді, коли зовнішня шина зайнята. Процесор i486 має чотири буфери відкладеного запису. Інформація у буфер записується за один такт. Після закінчення поточного циклу шини інформація з буферів передається зовні — у пам'ять або ПВгЗ. Зовнішні операції запису з буферів виконуються у тому самому порядку, в якому надійшли запити на запис. Якщо у незвільнених буферах усі запити на запис у пам'ять пов'язані з кеш-попаданнями, а запит на читання пов'язаний з кеш-промахом, то операція читання може відбутися раніше, ніж операції запису. Однак більше ніж один раз змінювати порядок виконання команд у МП не дозволяється, оскільки нові прочитані дані можуть замінити модифікований рядок кеш-пам'яті, з якого поновлена інформація очікує у буфері черги на запис в основну пам'ять. У такому разі друга спроба зміни послідовності команд може порушити цілісність даних. Для операцій введения-виведен-ня зміна послідовності команд не допускається, бо це може призвести до порушення протоколу обміну.

OverDrive-процесори призначені для модернізації мікропроцесорної системи або комплекс. Модернізація здійснюється заміною початкової моделі МП на нові моделі, так звані OverDrive-процесори, які мають вищі техніко-економічні показники. Такими моделями для i486 є Intel DX2 OverDrive, Intel DX4 OverDrive, Pentium OverDrive 63 та 83 МГц.

Для модернізації мікропроцесорної системи на системній платі, крім уже встановленого процесора, у додатковий роз'єднувач (сокет), позначений як OverDrive, встановлюється OverDrive-процесор у корпусі PGA-169. OverDrive-процесор спеціальним вихідним сигналом від'єднує основний процесор, що залишається на платі.

Режим системного керування

32-розрядних мікропроцесорів. Деякі

модифікації процесорів 386 і 486, крім

перелічених режимів (реального,

захищеного і віртуального F86),

мають режим системного керування SMM

(System

Management

Mode),

який призначено для

керування енергоспоживанням або

виконання програм, повністю ізольованих

як від прикладного програмного

забезпечення, так і від операційної

системи. Перемикання в режим SMM

здійснюється або апа-ратно

— подачею нульового потенціалу на

контакт

![]() мікросхеми процесора, або,

в деяких моделях, програмно — за

прийняттям повідомлення по шині АРІС.

Під час переходу в режим

SMM МП

виставляє сигнал підтвердження на

контакті

мікросхеми процесора, або,

в деяких моделях, програмно — за

прийняттям повідомлення по шині АРІС.

Під час переходу в режим

SMM МП

виставляє сигнал підтвердження на

контакті

![]() .

Після цього процесор зберігає свій стан

— уміст майже всіх регістрів — у

спеціальній області пам'яті SMRAM.

Якщо режим SMM

використовується для

вимкнення живлення процесора з

можливістю швидкого ввімкнення, пам'ять

SMRAM

має бути енергоиезалежною.

У цій області пам'яті знаходиться

підпрограма обробки переривання SMI.

Доступ до пам'яті дозволений

лише за наявності сигналу

.

Повернення з режиму

SMM здійснюється

як програмно, так і за перериванням.

.

Після цього процесор зберігає свій стан

— уміст майже всіх регістрів — у

спеціальній області пам'яті SMRAM.

Якщо режим SMM

використовується для

вимкнення живлення процесора з

можливістю швидкого ввімкнення, пам'ять

SMRAM

має бути енергоиезалежною.

У цій області пам'яті знаходиться

підпрограма обробки переривання SMI.

Доступ до пам'яті дозволений

лише за наявності сигналу

.

Повернення з режиму

SMM здійснюється

як програмно, так і за перериванням.