Розділ 3

ОДНОКРИСТАЛЬНІ УНІВЕРСАЛЬНІ МІКРОПРОЦЕСОРИ (СТАРШІ МОДЕЛІ)

3.1. Мікропроцесор i80286

Загальні відомості. Мікропроцесор i80286 належить до другого покоління 16-розрядних МІГ. Він виконаний за технологією 1,5 мкм, містить 134 000 транзисторів і працює з тактовою частотою 12,5 МГц. Після вдосконалення архітектури швидкодія МП i80286 у б разів вища, ніж МП i8086 з тактовою частотою 5 МГц. Розрядність регістрів дорівнює 16. Шина адреси 24-розрядна, що дає змогу адресувати 224 = 16 Мбайт пам'яті. Простір адрес введення-виведення становить 64 Кбайт. Система команд містить усі команди i8086, кілька нових команд загального призначення та команди керування захистом. Мікропроцесор i80280 має спеціальні засоби для роботи у системах з багатьма користувачами та багатозадачиих режимах. Його найістотнішою відмінністю від мікропроцесорів серії i8086/88 є механізм керування адресацією пам'яті, що забезпечує чотирирівневу систему захисту та підтримку віртуальної пам'яті. Спеціальні засоби призначено для підтримки механізму перемикання задач. Мікропроцесор i80286 має засоби контролю за переходом через межу сегмента, які працюють у реальному режимі.

Мікропроцесор може працювати у двох режимах:

• 8080 Real Address Mode, або Real Mode, — режим реальної адресації, або реальний режим. У цьому режимі МП i80286 фактично є високошвидкісним МП i8086 і адресує 1 Мбайт пам'яті;

• Protected Virtual Address Mode, або Protected Mode, — захищений режим віртуальної адресації або просто захищений режим. У цьому режимі МП адресує до 16 Мбайт пам'яті, а за використання механізму сторінкової адресації до 1 Гбайт віртуальної пам'яті кожної задачі.

Перемикання у захищений режим здійснюється швидко — однією командою (із заздалегідь підготовленими таблицями дескрипторів), а в режим реальної адресації — повільно, лише через апаратне скидання процесора. У MS DOS використовується реальний режим. Захищений режим використовується в операційних системах на зразок XENIX, UNIX, OS/2, NetWare286, MS Windows.

Для процесора i80286 можливі 256 різних типів переривань. Відрізняється від системи переривань МП i8086 перериванням під час виникнення особливих умов під час виконання команд, наприклад за розміщення двобайтового операнда в останній комірці сегмента даних зі зміщенням FFFFH. Таке переривання називають особливим випадком, або винятком. На відміну від переривань після оброблення винятків (крім винятку 9, що стосується співпроцесора) керування передається знову тій самій команді (включаючи всі префікси), що зумовила переривання. Після усунення умов, що спричинили виняток, відбувається повторне виконання команди.

Організація пам'яті. У реальному режимі адресація пам'яті переважно така сама, як і в МП i8086. Відмінність полягає у можливості використання додаткового блока пам'яті ємністю 64 Кбайт. Якщо у процесі виконання команди під час обчислення адреси комірки пам'яті виникає переповнення у двадцятий розряд шини адреси A20, процесор починає працювати з комірками пам'яті, адреси яких знаходяться в діапазоні 100 000H-10FFFFH.

Приклад 3.1. Знайти значення фізичної адреси операнда в реальному режимі під час виконання команди MOV AL, [57]; пересилання у регістр AL вмісту комірки пам'яті з адресою DS.SI, якщо вмістом сегментного регістра DS є число 0F802H, а вмістом регістра SI — 0В175H.

Для обчислення фізичної адреси до значення DS додамо чотири

нулі праворуч:

DS(0000) = 1111 1000 0000 0010 0000В = 0F8020H.

Виконавши операцію додавання отриманої величини з вмістом регістра 57, дістанемо фізичну адресу:

Отже, під час обчислення фізичної адреси отримане одиничне значення розряду А20 означає, що операнд розташується у другому мегабайті фізичної пам'яті.

Ще однією особливістю реального режиму i80286 є можливість контролю за переходом за межі сегмента. Під час адресації слова зі зміщенням 0FFFFH генерується виняток 13 (Segment Overrun Exception). За спроби виконання команди ESC з операндом пам'яті, що не вміщається у сегменті, генерується виняток 9 — Processor Extension Segment Overrun Interrupt.

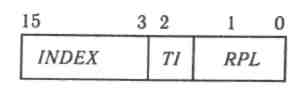

Рис. 3.1. Формат селектора сегмента

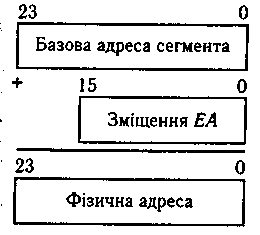

Рис. 3.2. Формування фізичної 24-розрядної адреси у захищеному режимі

У захищеному режимі також використовується сегментна адресація; кількість сегментів може бути від 1 до 16 Мбайт, довжина сегментів задається і може варіювати від 1 до 64 Кбайт, задаються атрибути або права доступу до сегмента (дозвіл запису або лише читання, рівні привілеїв тощо). Кожний сегмент характеризується 8-розрядною структурою даних — дескриптором сегмента, що містить інформацію про базову адресу сегмента, його межу та атрибути. Дескриптори розміщені у спеціальних таблицях — глобальній дескрипторній таблиці GDT або локальній дескрипторній таблиці LDT, які зберігаються в ОЗП. Незалежно від рівня привілею програма не може звертатися до сегмента доти, доки він не описаний у дескрипторній таблиці.

У захищеному режимі вміст сегментних регістрів називають селекторами сегментів. їх використовують для пошуку базової (початкової) адреси сегмента в одній з дескрипторних таблиць. Формат селектора показано на рис. 3.1.

Селектори, що завантажуються у 16-розрядні сегментні регістри CS, DS, SS, ES, мають три поля:

• RPL (Requested Privilege Level) (біти 0 і 1) — запрошений рівень привілеїв сегмента;

• ТІ (Table Indicator) (біт 2) — індикатор використання таблиці дескрипторів (якщо ТІ = 1, використовується глобальна таблиця, а якщо ТІ = 0, — локальна);

• INDEX (біти 3 — 15) — номер дескриптора у таблиці.

Глобальна дескрипторна таблиця єдина. Вона містить дескриптори для всіх задач, які виконує МП у багатозадачному режимі. Локальних дескрипторних таблиць може бути кілька, причому для кожної задачі можна задати свою локальну дескрипторну таблицю.

Фізичну 24-розрядну адресу операнда знаходять додаванням початкової 24-розрядної адреси сегмента з дескрипторної таблиці та адреси-зміщення, яка вказується у команді. Формування фізичної 24-розрядної адреси у захищеному режимі наведено на рис. 3.2.

Приклад 3.2. Знайти значення фізичної адреси комірки пам'яті [DS.SI], якщо базова адреса сегмента даних дорівнює 456 789H, а вміст регістра SI — 1234H.

Виконавши операцію додавання 24-розрядної базової адреси з адресою-зміщенням, тобто з вмістом регістра SI, отримаємо фізичну адресу:

Отже, фізична адреса дорівнює 4579ВВН.

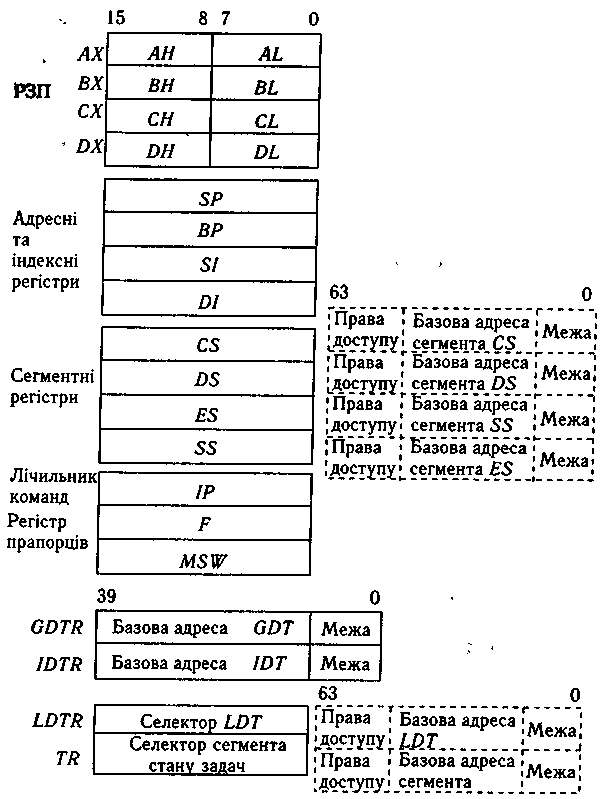

Програмна модель. До програмної моделі МП i80286 (рис. 3.3) входять 19 програмно-доступних регістрів і 6 недоступних (тіньових). Із 19 програмно-доступних регістрів МП i80286 14 повторюють регістри процесора i8086 (див. п. 3.5). П'ять нових регістрів такі:

40-розрядний регістр GDTR (Global Descriptor Table Register) — регістр глобальної дескрипторної таблиці. Призначений для задання розміщення глобальної дескрипторної таблиці в пам'яті. Регістр GDTR безпосередньо містить базову адресу і значення межі таблиці, яке задає її розмір. Розмір таблиці більший, ніж значення межі, на одиницю;

16-розрядний регістр LDTR (Local Descriptor Table Register) — регістр-селектор локальної дескрипторної таблиці. Його вміст вказує, де в глобальній дескрипторній таблиці знаходиться інформація про початкову адресу, межу і права доступу до локальної таблиці. Ця інформація переписується у тіньовий програмно-недоступний регістр;

40-розрядний регістр IDTR (Interrupt Descriptor Table Register) — регістр дескрипторної таблиці переривань. Завдяки цьому регістру в МП i80286 з'явилася можливість розміщувати таблицю векторів переривань у довільному місці ОЗП, а не з нульової адреси, як у МП і8086. Регістр IDTR за структурою аналогічний регістру GDTR;

16-розрядний регістр задачі TR (Task Register) — регістр-селектор сегмента стану поточної задачі TSS (Task State Segment). Такі сегменти асоціюються з кожною задачею. їхнє призначення — збереження контексту задачі під час перемикання задач;

Рис. 3.3. Програмна модель МП i80286

16-розрядний регістр стану машини MSW (Machine State Word), що керує режимом процесора і містить такі біти (рис. 3.4):

РЕ (Protection Enable) — дозвіл захисту. Встановлення цього прапорця переводить процесор у захищений режим. Повернення до реального режиму можливе лише за сигналом RESET.

MP (Monitor Processor Extension) — наявність співпроцесора. Якщо арифметичний співпроцесор i80287 з'єднаний з процесором i80286, то за ініціалізації операційна система має встановити цей біт у етап логічної одиниці. Тоді під час виконання команд WAIT та ESC і значення TS = 1 мікропроцесор генеруватиме виняток 7.

Рис. 3.4. Регістр стану машини MSW

EM (Processor Extension Emulated) — емуляція співпроцесора. Встановлення цього прапорця викликає виняток 7 після виконання команд арифметичного співпроцесора.

TS (Task Switch) — перемикання задач. Зі встановленням прапорця наступна команда, яка належить до співпроцесора, викличе виняток 7.

Тіньові регістри відіграють роль надоперативної пам'яті, їхнє призначення — підвищення швидкодії роботи МП (на рис. 3.3 тіньові регістри показано штриховою лінією).

Крім того, у програмній моделі, на відміну від МП i8086, додано нові біти у регістрі прапорців і змінено використання сегментних регістрів у захищеному режимі. У регістрі прапорців біт 14 визначений як NT (Nested Task Flag — прапорець певної задачі), а біти 13—12 — як IOPL (Input/Output Privilege Level — двобітове поле рівня привілеїв введення-виведення). Ці прапорці діють лише в захищеному режимі. Прапорець NT встановлюється у стан логічної одиниці під час перемикання задач за допомогою команди CALL. Після виконання команди І RET перевіряється стан прапорця NT і якщо NT = 1, здійснюється перемикання, якщо ні, то виконується звичайне повернення з переривання. Поле IOPL вказує рівень привілею поточної задачі, за якого дозволяється виконання певних операцій.

Сегментні регістри CS, SS, ES і DS визначають початкові адреси сегментів. У реальному режимі 20-розрядна початкова адреса сегмента визначається як вміст 16-розрядиого сегментного регістра, доповненого праворуч чотирма нульовими бітами. У захищеному режимі початкова 24-розрядна базова адреса сегмента знаходиться у дескрипторній таблиці в ОЗП, а вміст сегментних регістрів є селекторами, які вказують на тип таблиці та номер запису в ній (див. рис. 3.1).

Під час завантаження нового значення селектора дескриптори зчитуються з ОЗП і запам'ятовуються у внутрішніх програмно-недоступних або тіньових регістрах процесора. Це дає змогу підвищити швидкодію процесора, оскільки значення базових адрес сегментів змінюються порівняно рідко.

Регістри GDTR, LDTR, IDTR задають розташування дескрипторних таблиць у пам'яті (рис. 3.5). На рис. 3.5 показано, що глобальна дескриптор на таблиця містить N + 1 дескрипторів, локальна — К + 1, дескрипторна таблиця переривань — М + 1. Початкова адреса глобальної дескрипторної таблиці визначається бітами 39—16 регістра GDTR та обчислюється додаванням значень початкової адреси і межі таблиці (біти 15 — 0). Аналогічно початкова і кінцева адреси таблиці переривань визначаються вмістом регістра IDTR. Для адресації дескрипторів локальної таблиці використовують вміст регістра LDTR, який є селектором. Він вказує на номер дескриптора у глобальній дескрипторній таблиці. Цей дескриптор завантажується у тіньовий регістр (на рис. 3.5 зображено штриховою лінією). Перша та остання адреси локальної дескрипторної таблиці визначаються вмістом цього регістра.

Приклад 3.3. Знайти значення, яке треба завантажити у регістр GDTR, щоб задати у пам'яті глобальну дескрипторну таблицю з 21 дескриптора і з початковою адресою 000100H.

Біти 39—16 регістра GDTR задають початкову 24-розрядну адресу, отже, мають дорівнювати 000100H. Кожний запис у таблиці займає

Рис. 3.5. Розміщення дескрипторних таблиць у пам'яті

8 байт, тому, адреса 21 дескриптора визначається як 000100H + 20 • 8 = 0001А0H. У бітах 15-0 регістра GDTR треба розмістити число 0A0H, після чого вміст регістра GDTR становить

0001000AH.

Зазначимо, що команди завантаження регістрів таблиць GDTR, LDTR, IDTR, LGDT, LLDT, LIDT є привілейованими і виконуються у програмах з вищим рівнем пріоритету.

Адресний простір портів введення-виведення. Адресний простір портів МП i80286 такий самий, як і для МП i8086, тобто становить 64 • 2 одно- або 32 • 2 двобайтових портів. Додаткові рядкові команди REP INSB/INSW, REP OUTSB/OUTSW (табл. 3.1) забезпечують блокове оброблення зі швидкістю, що перевищує аналогічні операції в режимі ПДП. У захищеному режимі команди є привілейованими, тобто вони можуть виконуватися лише з певним рівнем привілею, що визначається полем IOPL регістра прапорців. Інакше викликається виняток 13 — порушення захисту.

Система команд. До системи команд МП i80286 входять усі команди МП i8086 і ряд додаткових (див. табл. 3.1). У табл. 3.1 використано ті самі позначення, що й у табл. 2.11.

Приклад 3.4. Написати програму переведення МП у захищений режим адресації.

Для переведення МП у захищений режим адресації треба встановити біт РЕ — молодший біт регістра MSW. Однак перед установленням цього біта треба задати початкові значення регістрів таблиць GDTR, LDTR, IDTR значення елементів дескрипторних таблиць в ОЗП. Зазвичай таблиці переписують із ПЗП в ОЗП. Зазначимо, що таблиці мають знаходитися в ОЗП, оскільки під час виконання програми їхній вміст може модифікуватися.

Програма переведення МП має вигляд:

SMSW |

ВХ |

Збереження MSW у ВХ |

OR |

ВХ,0001Н |

Установлення молодшого біта у стан логічної одиниці |

LMSW |

ВХ |

Завантаження MSW |

JMP |

M1 |

Скидання черги команд |

M1 |

|

Початок роботи у захищеному режимі |

Короткий перехід JMP M1 на наступну команду потрібний для скидання черги команд. У МП i80286 існує випереджальна вибірка команд. Якщо МП виконав команду LMSW, яка перевела його у захищений режим, а в черзі команд залишилися команди, які мали виконуватися у реальному режимі, то після переведення процесора у захищений режим команди реального режиму будуть декодовані неправильно.

Таблиця 3.1 Додаткові команди МП i80286

Мнемокод |

Опис |

PUSH immed |

Команди роботи зі стеком Переміщення безпосередніх даних immed у стек |

PUSH A |

Переміщення у стек вмісту регістрів АХ, ВХ, СХ, DX, SI, DI, BP, SP |

РОРА |

Переміщення даних зі стеку в регістри АХ, ВХ, СХ, DX, SI, DI, BP, SP |

IMUL reg16,r/m |

Арифметичні команди Множення вмісту reg 16 на вміст r/m (16 біт) |

IMUL reg16, r/m, immed |

Множення вмісту r/m на 16-бітовий безпосередній операнд і переміщення результату в reg16 |

[REP] INSB ([REP] INSW) |

Рядкові команди Введення байта (слова) у комірку пам'яті ES: [DI] із порту з адресою DX з автоінкрементуванням (DF = 0) або автодекрементуванням (DF = 1) адреси. У разі використання префікса REP операція повторюється СХ разів |

[REP] OUTSВ ([REP] OUTSW) |

Виведення байта (слова) з комірки пам'яті DS: [S1] у порт з адресою DX з автоінкрементуванням (DF = 0) або автодекрементуванням (DF = 1) адреси. У разі використання префікса REP операція повторюється СХ разів |

BOUND reg16, lmts |

Команди переривань Перевірка меж масиву — якщо знакове число у reg16 не знаходиться в заданих межах, виконується І NT 5. Межі задаються у двох суміжних словах пам'яті за адресою Imts. |

ENTER frmsiz, frms |

Команди підтримки процедур Підготовка блока параметрів процедур (frmsiz — кількість байт для змінних процедури, frms — рівень укладення процедур) |

LEAVE |

Відміна чинності ENTER (відновлює значення вмісту регістрів SP і ВР) |

CLTS |

Команди керування станом МП Скидання прапорця перемикання задач |

SEG |

Префікс заміни сегмента |

LGDT src |

Команди керування захистом Завантаження регістра GDTR з пам'яті (6 байт)* |

SCDT dest |

Збереження вмісту регістра GDTR у пам'яті (6 байт)* |

LIDT src |

Завантаження регістра IDTR з пам'яті (6 байт)* |

SIDT dest |

Збереження вмісту регістра IDTR у пам'яті (6 байт)* |

LLDT src |

Завантаження регістра LDTR з регістра або пам'яті reg /тет16 |

SLDT dest |

Збереження вмісту регістра LDTR у reg / тет16 |

LMSW src |

Завантаження регістра MSW з регістра або пам'яті reg / тет16 |

SMSW dest |

Збереження регістра MSW у reg / тет16 |

LTR src |

Завантаження регістра задачі з reg / тет16 |

STR dest |

Збереження вмісту регістра задачі в reg / тет16 |

LAR dest, src |

Завантаження старшого байта dest байтом прав доступу дескриптора src |

LSL dest, src |

Завантаження dest межею сегмента, дескриптор якого заданий src |

ARPL reg/тетіб, гедіб |

Вирівнювання RPL у селекторі до найбільшого числа з поточного рівня і заданого операндом |

VERR seg |

Верифікація читання: встановлення прапорця ZF у стан логічної одиниці (ZF = 1), для дозволу читання у сегменті seg |

VERW seg |

Верифікація запису: встановлення ZF = 1 для дозволу запису в сегмент seg |

*Команди LGDT, LIDT завантажують у 40-розрядні регістри GDTR, IDTR п'ять байтів, але під час виконання команди передаються шість байтів: перші п'ять з них пересилаються у регістри, а шостий (з найбільшою адресою) ігнорується. Однак для сумісності з майбутніми розробками МП він повинен мати нульове значення. Команди SGDT, SIDT передають вміст регістрів GDTR, IDTR у пам'ять, при цьому передаються шість байтів: у п'яти знаходиться вміст регістра, а шостий — невизначений.

Таблиця 3.2. Переривання і винятки МП i80286

Номер переривання

|

Адреса повернення |

Функції |

||

Реальний режим |

Захищений режим |

|||

0 |

Перший байт команди |

Помилка ділення — виникає, якщо частка занадто велика або дільник дорівнює нулю |

||

1 |

Наступна команда |

Переривання покрокової роботи |

||

2 |

Немає |

Немасковане переривання |

||

3 |

Наступна команда |

Контрольна зупинка {ІNT 3) |

||

4 |

Тe саме |

Особливий випадок переповнення (INTO) |

||

5 |

Перший байт команди |

Особливий випадок виходу з діапазону — виникає за виконання команди BOUND |

||

6 |

Те саме |

Неприпустимий код операції — виникає, якщо зустрічається недійсний код операції або команда завдовжки понад 10 байт |

||

7 |

- « - |

Співпроцесор недоступний |

Співпроцесор недоступний або відбулося перемикання задач |

|

8 |

- « - |

|

Подвійна відмова — ситуація, коли МП виявляє два незалежних винятки у процесі відпрацювання однієї команди. Якщо під час його обслуговування станеться виняток, то МП вимкнеться (цикл Shutdown). У цьому стані процесор припиняє свої дії і виводиться з нього сигналами скидання або не-маскованого переривання |

|

9 |

Невизначена |

Порушення межі сегмента співпроцесором — виникає, якщо операнд співпроцесора не поміщається у сегмент, наприклад, 16-розрядний операнд має зміщення 0FFFFH |

||

10 |

Перший байт команди |

— |

Неприпустимий сегмент стану задачі |

|

11 |

Тe саме |

— |

Сегмента немає |

|

12 |

- « - |

Порушення межі сегмента стеку |

Порушення межі сегмента стеку або стеку немає |

|

13 |

- « - |

Порушення межі сегмента даних або коду — виникає, якщо операнд або код операції у сегмент не поміщається |

Порушення захисту — виникає у таких випадках: за виходу за межі таблиці дескрипторів; з порушенням привілеїв; після завантаження недійсного дескриптора або типу сегмента; за спроби запису в сегмент коду або сегмент даних, призначених лише для читання, під час читання лише з виконуваного сегмента кодів; за спроби виконати привілейовані команди, дозволені лише для певних рівнів CPL і IOPL |

|

14 |

|

Зарезервовано |

||

15 |

— « — |

|||

16 |

Наступна команда ESC або WAIT |

Особливий випадок співпроцесора — виникає в МП i80286 за будь-якого немаскованого особливого випадку в співпроцесорі |

||

17 |

Зарезервовано |

|||

|

|

|||

31 |

Зарезервовано |

|||

Цикли шини. Мікропроцесор i80286 має шинний інтерфейс з 6-байтовою чергою команд, що забезпечує конвеєрну адресацію (Pipelined Addressing). Це забезпечує вибірку кодів команд або даних із пам'яті з випередженням, що дає змогу почати фазу ідентифікації або адресації нового циклу, не дочекавшись закінчення попереднього. Розрізняють шість типів циклів шини:

• ЧИТАННЯ ПАМ'ЯТІ;

• ЗАПИС У ПАМ'ЯТЬ;

• ЧИТАННЯ ПОРТУ;

• ЗАПИС У ПОРТ;

• ПІДТВЕРДЖЕННЯ ПЕРЕРИВАННЯ;

• СТОП-ЗУПИНКА.

Зазначимо, що слово з непарною адресою передається за два цикли шини, а з парною — за один. На рис. 3.6 показано цикли шини ЧИТАННЯ і ЗАПИС слова у комірку пам'яті з парною адресою. Зчитування слова з ОЗП здійснюється щонайменше за чотири періоди тактових імпульсів CLK або за два стани процесора (без урахування сигналу готовності READY). Кожний стан МП триває два такти CLK. Під час першого стану, позначеного через ТS, процесор виставляє на шину адреси значення адреси комірки пам'яті, з якої буде зчитуватися слово. Завдяки конвеєрній адресації адреса комірки виставляється з деяким випередженням, однак вона не зберігається на шині адреси впродовж циклу. Для сумісності

Рис. 3.6. Цикли шини ЧИТАННЯ і ЗАПИС слова у комірку пам'яті з парною адресою

з шиною ISA

сигнали шини адреси

запам'ятовуються у регістрах-фіксаторах

за стробом ALE.

Керуючі сигнали читання

пам'яті

![]() і адресний строб ALE

формуються системним

контролером 82288 на початку другого стану

TC.

Сигнали керування та

адреси обробляються схемою керування

пам'яттю, внаслідок чого, починаючи

з середини другого стану TC,

на шині даних з'являється

слово з ОЗП, і процесор зчитує його із

шини даних. Тривалість циклу ЧИТАННЯ з

парною адресою становить тривалість

двох станів.

і адресний строб ALE

формуються системним

контролером 82288 на початку другого стану

TC.

Сигнали керування та

адреси обробляються схемою керування

пам'яттю, внаслідок чого, починаючи

з середини другого стану TC,

на шині даних з'являється

слово з ОЗП, і процесор зчитує його із

шини даних. Тривалість циклу ЧИТАННЯ з

парною адресою становить тривалість

двох станів.

Під час зчитування слова з непарною адресою в першому циклі переноситься байт за старшою половиною шини даних D15 — D8, а в другому — передається другий байт за молодшою половиною D7—D0. Цикл шини ЗАПИС У ПАМ'ЯТЬ з парною адресою також дорівнює тривалості двох станів. У першій половині циклу ТS виставляється адреса і дані, в другій — відбувається запис в ОЗП.

Виконання циклів шини ЧИТАННЯ

ПОРТУ та ЗАПИС У ПОРТ аналогічне

розглянутим вище циклам ЧИТАННЯ ПАМ'ЯТІ

та ЗАПИС У ПАМ'ЯТЬ, однак у цьому випадку

на шину A15—A0

виставляється адреса порту і замість

сигналів читання або запису пам'яті

генеруються сигнали

![]() — для читання портів

введения-виведення, або

— для читання портів

введения-виведення, або

![]() — для

запису в порти введення-виведення.

— для

запису в порти введення-виведення.

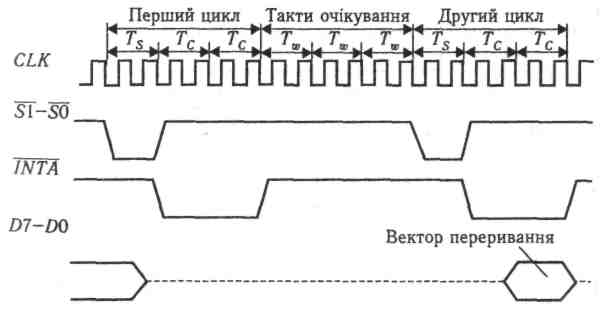

Цикл шини ПІДТВЕРДЖЕННЯ ПЕРЕРИВАННЯ (рис. 3.7) виконується у разі виникнення апаратного переривання (наявності активного рівня на виводі INTR). Цикл складається з двох процесорних циклів, поділених трьома тактами очікування Tw.

Рис. 3.7. Цикл шини ПІДТВЕРДЖЕННЯ ПЕРЕРИВАННЯ

Кожний процесорний цикл складається з трьох станів — TS, ТC, ТC- Це потрібно для того, щоб продовжити дію сигналу І NT А, що посилається на контролер переривань 8259A. Перший цикл дозволяє ведучому контролеру визначити, який з ведених контролерів викликав переривання. У другому циклі МІГ зчитує із шини даних вектор переривання, що використовується для знаходження адреси у таблиці векторів переривань. Цикл шипи СТОП-ЗУПИНКА {Halt/Shutdown) виникає або під час виконання команди HLT, або під час оброблення особливого випадку 8 (табл. 3.2) у захищеному режимі.

Типи переривань. Переривання і винятки в реальному і захищеному режимах наведено у табл. 3.2.

Кожному номеру переривання відповідає елемент у таблиці IDT дескрипторів переривань, яка містить вектори переривань. Після скидання МП, а також під час роботи МП у реальному режимі, таблиця векторів IDT розміщується, починаючи з нульової адреси, однак командою завантаження регістра JDTR можна змінити її місцезнаходження у межах першого мегабайта і зменшити розмір таблиці.

Приклад 3.5. Визначити, чи виникне переривання у процесі роботи МП у реальному режимі під час виконання команди

MOV AX,[0FFFFH].

Під час виконання цієї команди в акумулятор АХ пересилається слово з сегмента даних, причому молодший байт слова має зміщення 0FFFFH, а старший — 0000Н. Цей випадок є порушенням межі сегмента і виникає переривання 13.