- •1. Математические и логические основы вычислительной техники

- •1.1. Основные сведения об электронно-вычислительной технике

- •1.1.1. Классификация эвм

- •1.1.2.Основные характеристики эвм

- •1.2. Виды информации и способы представления ее в эвм

- •1.2.1.Сигналы импульсных и цифровых устройств

- •1.2.2.Системы счисления

- •1.2.3. Правила двоичной арифметики

- •1.2.4. Основные логические операции

- •Операция импликация

- •Операция запрет

- •1.2.5.Законы алгебры логики

- •1.2.6. Основной базис алгебры логики

- •1.2.7. Нормальные и совершенные нормальные формы логических функций

- •1.2.8. Минимизация логических функций методом Квайна

- •1.2.9.Синтез логических устройств в базисах «или-не», «и-не»

- •Некоторые особенности построения схем логических устройств

- •1.2.10. Минимизация логических функций методом карт Вейча

- •1.3. Логические элементы эвт

- •1.3.1. Классификация и система обозначений цифровых микросхем

- •1.3.2. Условные графические обозначения цифровых микросхем

- •1.3.3. Параметры логических элементов

- •1.3.4. Базовые логические элементы

- •Базовый ттл-элемент и—не

- •Базовый эсл-элемент или/или—не

- •Базовый кмоп-элемент или—не

- •Сравнительная оценка базовых логических элементов

- •2.Типовые узлы и элементы вычислительной техники

- •2.1. Типовые комбинационные цифровые устройства

- •2.1.1. Шифратор (кодер)

- •2.1.2. Дешифратор (декодер)

- •Расширение разрядности дешифратора

- •2.1.3. Мультиплексор

- •Расширение разрядности мультиплексора

- •2.1.4. Демультиплексор

- •Расширение разрядности демультиплексора

- •2.1.5. Сумматор

- •Многоразрядные двоичные сумматоры

- •Программируемая логическая матрица

- •2.2. Последовательностные цифровые устройства

- •2.2.1. Интегральные триггеры

- •Асинхронный rs триггер с инверсными входами.

- •Синхронный rs – триггер.

- •Микросхема к555тр2

- •Микросхема к155тв9

- •Микросхема к155тм 2

- •2.2.2. Регистры Общие сведения

- •Параллельно-последовательный регистр

- •2.2.3. Счетчики

- •Микросхема к155ие7

- •2.2.4. Полупроводниковые запоминающие устройства

- •Условные обозначения ис зу

- •Оперативное запоминающее устройство

- •Принцип наращивания емкости памяти

- •Постоянные запоминающие устройства

- •Перепрограммируемые постоянные запоминающие устройства

- •2.2.5. Аналого-цифровое преобразование информации Принцип аналого-цифрового преобразования информации

- •Цап с резисторной матрацей r—2r

- •Аналого-цифровой преобразователь последовательного счета

- •Времяимпульсный аналого-цифровой преобразователь

- •Параметры аналого-цифрового и цифроаналогового преобразователей

2.2. Последовательностные цифровые устройства

2.2.1. Интегральные триггеры

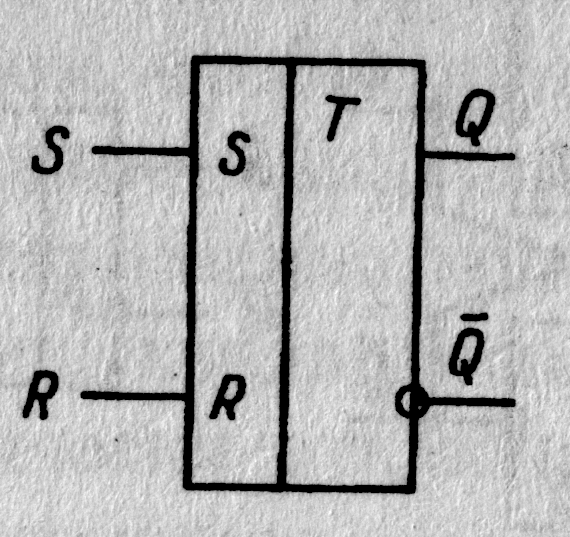

Триггер- это устройство, имеющее два устойчивых состояния и способное под действием управляющего сигнала скачком переходить из одного состояния в другое.

Триггер имеет два выхода:

прямой Q и инверсный

![]() .

Состояние триггера определяется по

логическому уровню на прямом выходе.

Если триггер в единичном состоянии, то

Q=1,

=0.

Если триггер в нулевом состоянии, то

Q=0,

=1. Триггер может иметь различные

информационные входы:

.

Состояние триггера определяется по

логическому уровню на прямом выходе.

Если триггер в единичном состоянии, то

Q=1,

=0.

Если триггер в нулевом состоянии, то

Q=0,

=1. Триггер может иметь различные

информационные входы:

S – раздельный вход установки триггера в единичное состояние,

R – раздельный вход установки триггера в нулевое состояние,

J – вход установки универсального триггера в единичное состояние,

К - вход установки универсального триггера в нулевое состояние,

D - вход установки триггера в состояние, соответствующее логическому уровню, действующему на нем,

Т – счетный вход.

В зависимости от того, какие входы имеет триггер, различают: RS- триггер, JK- триггер, D- триггер, T- триггер.

Синхронные триггеры, кроме информационных, имеют дополнительный синхронизирующий (управляющий) вход С. Срабатывание синхронного триггера происходит в том случае, если на входе С действует определенный сигнал. Срабатывание триггеров со статическим синхронизирующим входом С происходит в том случае, если на нем действует логическая единица. Срабатывание синхронного триггера с прямым динамическим входом С может произойти в момент положительного перепада напряжения на нем, а срабатывание синхронного триггера с инверсным динамическим синхронизирующим входом происходит в момент отрицательного перепада напряжения на нем.

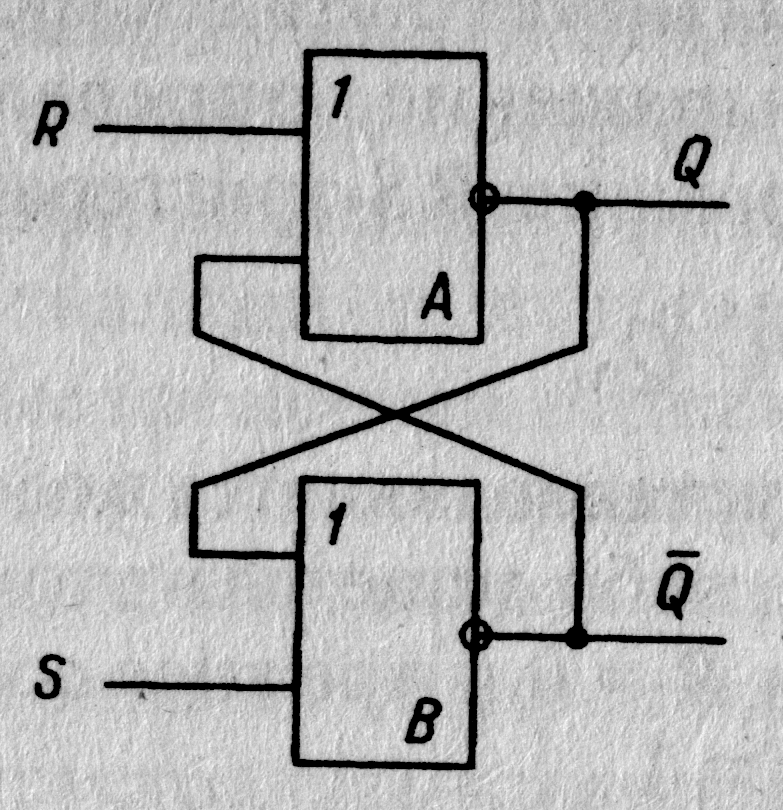

Асинхронный RS триггер с прямыми входами.

Может быть построен на элементах «или-не», для которых активным уровнем является логическая единица (рисунок 2.2.1.1.)

|

|

Рисунок 2.2.1.1.

Таблица функционирования

Вход |

Выход |

|

S |

R |

Q |

0 |

0 |

Q0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

X |

При S=0 и R=0 на триггер действуют пассивные логические уровни, срабатывание триггера не происходит и он остается в исходном состоянии Q0.

При S=0 и R=1 активный уровень логической единицы действуют на вход установки в нулевое состояние R, поэтому триггер переходит в нулевое состояние.

При S=1 и R=0 активный уровень логической единицы действуют на вход установки в единичное состояние S, поэтому триггер переходит в единичное состояние.

При S=1 и R=1 состояние триггера будет неопределенным, поэтому такая комбинация входных сигналов называется запрещенной.

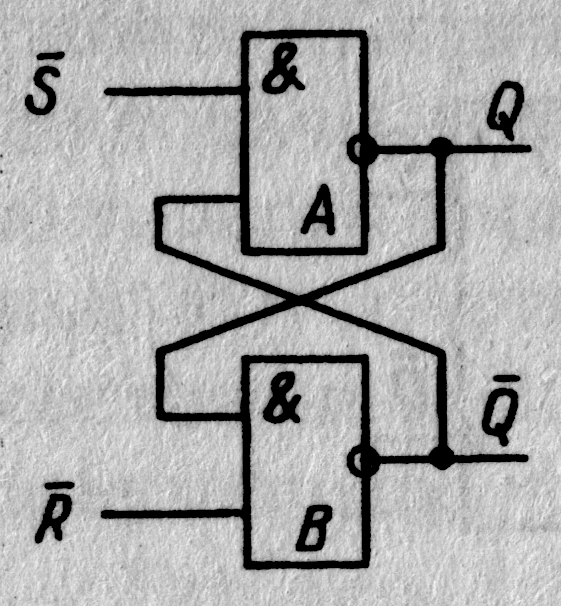

Асинхронный rs триггер с инверсными входами.

Он может быть построен на элементах «и-не», для которых активным уровнем является логический ноль (рисунок 2.2.1.2.)

|

|

Рисунок 2.2.1.2.

Таблица функционирования для триггера с инверсными входами инверсна таблице функционирования для триггера с прямыми входами.

Вход |

Выход |

|

S |

R |

Q |

0 |

0 |

X |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

Q0 |