- •1. Математические и логические основы вычислительной техники

- •1.1. Основные сведения об электронно-вычислительной технике

- •1.1.1. Классификация эвм

- •1.1.2.Основные характеристики эвм

- •1.2. Виды информации и способы представления ее в эвм

- •1.2.1.Сигналы импульсных и цифровых устройств

- •1.2.2.Системы счисления

- •1.2.3. Правила двоичной арифметики

- •1.2.4. Основные логические операции

- •Операция импликация

- •Операция запрет

- •1.2.5.Законы алгебры логики

- •1.2.6. Основной базис алгебры логики

- •1.2.7. Нормальные и совершенные нормальные формы логических функций

- •1.2.8. Минимизация логических функций методом Квайна

- •1.2.9.Синтез логических устройств в базисах «или-не», «и-не»

- •Некоторые особенности построения схем логических устройств

- •1.2.10. Минимизация логических функций методом карт Вейча

- •1.3. Логические элементы эвт

- •1.3.1. Классификация и система обозначений цифровых микросхем

- •1.3.2. Условные графические обозначения цифровых микросхем

- •1.3.3. Параметры логических элементов

- •1.3.4. Базовые логические элементы

- •Базовый ттл-элемент и—не

- •Базовый эсл-элемент или/или—не

- •Базовый кмоп-элемент или—не

- •Сравнительная оценка базовых логических элементов

- •2.Типовые узлы и элементы вычислительной техники

- •2.1. Типовые комбинационные цифровые устройства

- •2.1.1. Шифратор (кодер)

- •2.1.2. Дешифратор (декодер)

- •Расширение разрядности дешифратора

- •2.1.3. Мультиплексор

- •Расширение разрядности мультиплексора

- •2.1.4. Демультиплексор

- •Расширение разрядности демультиплексора

- •2.1.5. Сумматор

- •Многоразрядные двоичные сумматоры

- •Программируемая логическая матрица

- •2.2. Последовательностные цифровые устройства

- •2.2.1. Интегральные триггеры

- •Асинхронный rs триггер с инверсными входами.

- •Синхронный rs – триггер.

- •Микросхема к555тр2

- •Микросхема к155тв9

- •Микросхема к155тм 2

- •2.2.2. Регистры Общие сведения

- •Параллельно-последовательный регистр

- •2.2.3. Счетчики

- •Микросхема к155ие7

- •2.2.4. Полупроводниковые запоминающие устройства

- •Условные обозначения ис зу

- •Оперативное запоминающее устройство

- •Принцип наращивания емкости памяти

- •Постоянные запоминающие устройства

- •Перепрограммируемые постоянные запоминающие устройства

- •2.2.5. Аналого-цифровое преобразование информации Принцип аналого-цифрового преобразования информации

- •Цап с резисторной матрацей r—2r

- •Аналого-цифровой преобразователь последовательного счета

- •Времяимпульсный аналого-цифровой преобразователь

- •Параметры аналого-цифрового и цифроаналогового преобразователей

Базовый эсл-элемент или/или—не

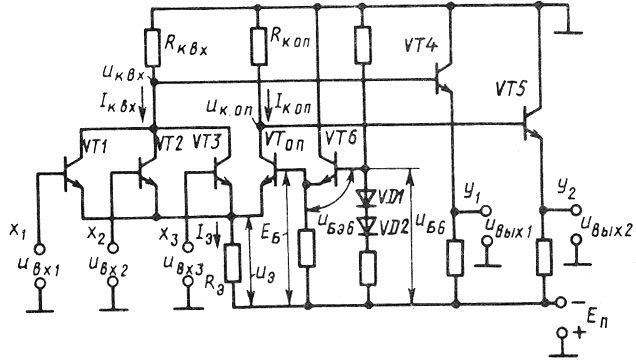

В этом элементе обе логические операции (ИЛИ, НЕ) выполняются эмиттерно-связанными транзисторами, чем и обусловлено название типа логики. Элемент имеет два выхода, на одном из которых фиксируется результат операции ИЛИ, а на другом — операции ИЛИ—НЕ. Обозначают такой элемент ИЛИ/ИЛИ—НЕ. Напряжение, соответствующее логической 1, U1 = — (0,7 0,95) В, а логическому 0 U° = —(1,51,9) В; напряжение питания Еп = 5 В (рисунок 1.3.4.2.)

Рисунок 1.3.4.2.

Основу структуры рассматриваемого элемента (рис. 3.30) составляет переключатель тока, рассмотренный в § 2.7. Он собран на входных VT1, VT2, VT3 и опорном VToп транзисторах, эмиттеры которых связаны. Потенциал базы VToп относительно минусовой шины Еп имеет стабильное значение EБ, а относительно «земли» — значение UБоп = ЕБ — Еп, которое лежит между уровнями входных сигналов: U°< UБоп< U1.

Когда хотя бы на одном входе действует напряжение U1 логической 1, один из входных транзисторов открыт — напряжение uэ на эмиттерах превосходит значение EБ и транзистор VToп заперт. Если напряжение на входе элемента меняется с U1 на U0 (так что х1 = х2 = х3 = 0), то uэ уменьшается и разность ЕБ — uэ оказывается достаточной для отпирания транзистора VT0П. При этом его ток создает на резисторе Rэ напряжение uэ, запирающее входные транзисторы VT1—VT3.

Таким образом, ток Iэ эмиттерной цепи переключается то в коллекторную цепь входных транзисторов (если хотя бы на одном входе логическая 1), то в коллекторную цепь опорного транзистора VToп (когда xl = x2 = x3 = 0).

Наличие тока в коллекторной цепи приводит к падению напряжения на включенном в нее резисторе (RК вх или RК оп) и к уменьшению потенциала коллектора относительно заземленной в данной схеме положительной шины источника питания. Поэтому, например, при х1 = 1 ток IК вх Iэ и uвых1 имеет большое отрицательное значение — логический 0 (y1 = 0), а uвьх2 — меньшее отрицательное значение — логическая 1 (у2 = 1). При X1 = X2 = X3 = 0 ток IК оп Iэ и uвых2= U° (у2 = 0), а uвых1 = U1 (y1 = 1).

Следовательно, по выходу y1 реализуется логическая функция ИЛИ—НЕ, а по выходу у2 — логическая функция ИЛИ.

На транзисторах VT4 и VT5 выполнены эмиттерные повторители. За счет них повышается нагрузочная способность элемента, а также по сравнению с uК вх и uК оп уменьшается уровень выходных сигналов на значение напряжения uБЭ на эмиттерно-базовых переходах VT4 и VT5. В отсутствие эмиттерных повторителей потенциалы с коллекторов данного элемента непосредственно воздействовали бы на базы входных транзисторов следующего элемента, что вызвало бы их насыщение.

Эмиттерный повторитель на транзисторе VT6 является источником стабильного опорного напряжения. При изменении температуры напряжения на диодах VD1 и VD2 изменяются примерно так же, как и uБЭ6. Поэтому ЕБ=uЭ6 = uБ6 — uБЭ6 сохраняется достаточно стабильным.

Обычно в схеме с n-p-n-транзисторами «заземляется» минусовая шина источника питания, имеющая в такой схеме самый низкий потенциал. При этом относительно нее потенциалы точек схемы не могут быть отрицательными. В рассмотренной схеме к «земле» присоединена плюсовая шина источника Еп, имеющего в данной схеме самый высокий потенциал. Поэтому относительно нее потенциалы точек схемы не могут быть положительными. Будем считать, что в среднем U1 = —0,8 В, U° = —1,7 В, UБоп = 0,5 (U1 + U°)= —1,25 В, а напряжение на открытом эмиттерном переходе кремниевого транзистора ео = О,6 В. Когда uвх1 = uвх2 = uвх3 = U°= — 1,7 В, то напряжение на эмиттерных переходах входных транзисторов uбэ=U° — (Uб оп —е0) = —1,7 — (1,25 — 0,6) = 0,15 В, при котором они заперты. Если на одном из входов появляется логическая 1 (например, uвх1 = U1 = — 0,8 В), то на эмиттерном переходе VT1 окажется напряжение uБЭ=u1 — (UБ оп — ео)= —0,8 —(—1,25 —0,6) 1 В, при котором транзистор VT1 откроется. После этого напряжение на эмиттерном переходе опорного транзистора uБЭ = UБoп — (uBX1 — e0) = — 1,25 — (— 0,8 — 0,6) = 0,15 В, при котором опорный транзистор заперт.

«Заземление» положительной шины источника приводит к тому, что при колебаниях величины Еп обеспечивается большее постоянство уровней выходных логических потенциалов U1 и U0.

К классу ЭСЛ относятся, в частности, микросхемы серий К187, К223, К500.