- •Вопрос №1 Создание и эволюция эвм. Нулевое поколение.

- •Вопрос №2 Создание и эволюция эвм. Первое поколение (1940-1950-е годы).

- •Вопрос №3 Создание и эволюция эвм. Второе поколение (1950-1960-е годы).

- •Вопрос №4 Создание и эволюция эвм. Третье поколение (1960- сер. 1970 годов).

- •Вопрос №5 Создание и эволюция эвм. Четвёртое поколение (1975-1990).

- •Вопрос №6 Создание и эволюция эвм. Пятое поколение.

- •Вопрос №7 Основные классы современных эвм. Классификация эвм по принципу действия, по назначению.

- •Вопрос №8 Основные классы современных эвм. Классификация эвм по размерам и вычислительной мощности.

- •Вопрос №9 Понятие архитектуры эвм. Структурная схема современного компьютера.

- •Вопрос №10 Классическая архитектура эвм и принципы фон Неймана.

- •Вопрос №11 Дополнительные интегральные микросхемы: контроллер прямого доступа, контроллер прерываний, математический сопроцессор.

- •Контроллер прямого доступа к памяти (dmac)

- •Контроллер прерываний

- •Математический сопроцессор

- •Вопрос №12 Функциональные характеристики эвм

- •Вопрос №13 Внешние устройства: классификация, краткая характеристика.

- •Манипуляторы

- •Принтеры, плоттеры

- •Вопрос № 14. Внешняя память персонального компьютера: оптические диски (cd-rom, cd-r, cd-rw)

- •Вопрос № 15. Внешняя память персонального компьютера: оптические диски (dvd, Blu- Ray)

- •Вопрос № 16. Внешняя память персонального компьютера: мобильные запоминающие устройства

- •2. Скорость записи/чтения

- •3. Надежность хранения данных

- •4. Дизайн

- •5. Функции защиты информации

- •6. Цена

- •Вопрос №17 Устройства ввода информации (клавиатура, сканер, дигитайзер, манипуляторы).

- •Вопрос №18 Устройства вывода информации (монитор, принтер, плоттер).

- •Монитор

- •Принтеры, плоттеры

- •Вопрос №19 Понятие «информация». Меры информации.

- •Вопрос №20 Представление символьной информации в эвм. Стандартные коды.

- •Вопрос №21 Кодирование графической информации

- •Вопрос №22

- •Вопрос №23 Понятие о системах счисления. Системы счисления, применяемые в эвм.

- •Вопрос №24 Системы счисления: алгоритм перевода целых и дробных чисел из 10-ой системы счисления в 2-ую, 8-ую, 16-ую и обратно.

- •1. Понятие о системах счисления.

- •Вопрос №25 Арифметические операции в позиционных системах счисления.

- •Вопрос №26 Алгебраическое представление двоичных чисел (прямой, обратный и дополнительный код числа).

- •Вопрос №27 Представление чисел в форме с фиксированной и плавающей запятой. Арифметические операции над числами с фиксированной и плавающей запятой.

- •Вопрос №28 Арифметические основы построения эвм.

- •1. Представление информации в компьютере

- •2. Системы счисления

- •3. Перевод числа из одной системы счисление в другую

- •4. Арифметические операции в позиционных системах счисления

- •Вопрос №29 Логические основы построения эвм. Аксиомы, тождества и основные законы алгебры логики

- •Логический синтез вычислительных схем

- •Вопрос №30 Законы и соотношения алгебры логики. Формула де Моргана

- •1. Закон одинарных элементов

- •2. Законы отрицания

- •3. Комбинационные законы.

- •4. Правило поглощения (одна переменная поглощает другие)

- •5. Правило склеивания (выполняется только по одной переменной)

- •Закон де моргана

- •Вопрос №31 Логический синтез вычислительных схем.

- •Вопрос №32 Система элементов эвм. Электронные технологии и элементы, применяемые в эвм

- •Система логических элементов

- •Вопрос №33 Триггеры как элементы памяти эвм: основные типы и их реализация на основе логических элементов.

- •Вопрос №34 Регистры эвм: назначение, классификация и схемная реализация.

- •Вопрос №35 Счетчики эвм: назначение, логика работы.

- •Вопрос №36 Узлы как структурная единица эвм, их типы.

- •2. Оперативная память (озу)

- •3. Постянное запоминающее устройство (пзу)

- •4. Внешняя память

- •5. Устройства ввода

- •6.Устройства вывода.

- •7. Информационная шина (магистраль)

- •8. Некоторые подробности

- •В принципе возможна !!!

- •В принципе возможна !

- •Вопрос №37 Назначение сумматора. Последовательные и параллельные сумматоры: принципы их функционирования.

- •Вопрос №38 Шифраторы, дешифраторы: назначение, виды, уго этих узлов.

- •Вопрос №39 Мультиплексоры, демультиплексоры: назначение, виды, уго этих узлов.

- •Вопрос №40 Общие сведения о запоминающих устройствах

- •Классификация зу:

- •Вопрос №41 Многоуровневая организация памяти эвм (мпп, оп, взу, кэш-память)

- •Вопрос №42 Назначение оперативных запоминающих устройств.

- •Вопрос №43 Статические и динамические озу. Виды модулей dram.

- •Вопрос №44 Общая характеристика постоянной памяти. Принцип работы пзу.

- •Вопрос №45 Основные типы пзу

- •Вопрос №46 Назначение и структура микропроцессора. Устройство мп

- •Вопрос №47 Основные блоки микропроцессора

- •Вопрос №48 Выполнение команд в микропроцессоре. Система команд мп, форматы команд, способы адресации.

- •Вопрос №49 Системы risc и cisc.

- •Вопрос №50 Назначение микропрограммного устройства управления.

- •Вопрос №51 Назначение и структура арифметико-логического устройства.

- •Вопрос №52 Классификация алу. Выполнение операций сложения (вычитания) и умножения в алу. Классификация алу:

- •Алгоритмы сложения (вычитания) и умножения в алу

- •Вопрос №53 Обеспечение достоверности информации.

- •Классификация методов контроля достоверности

- •Методы контроля достоверности

- •Вопрос №54 Понятие о кодировании и коде.

- •Вопрос №55 Понятие избыточности кода. Минимальное кодовое расстояние.

- •Вопрос №56 Код с проверкой по четности/нечетности. Коды с постоянным весом. Циклические коды. Код с проверкой по четности/нечетности

- •Коды с постоянным весом

- •Циклические коды

- •Вопрос №57 Корректирующая способность кода.

- •Вопрос №58 Контроль передачи информации с помощью кода Хемминга

- •Вопрос №59 Коды Рида-Соломона. Код Хаффмана. Оптимальное кодирование Шеннона-Фано Коды Рида-Соломона

- •Идея кодов Рида-Соломона

- •Ошибки в символах

- •Преимущество кодирования

- •Архитектура кодирования и декодирования кодов Рида-Соломона

- •Арифметика конечного поля Галуа

- •Алгоритм Хаффмана

- •Адаптивное сжатие

- •Переполнение

- •Масштабирование весов узлов дерева Хаффмана

- •Алгоритм Шеннона — Фано

- •Основные сведения

- •Алгоритм вычисления кодов Шеннона — Фано

- •Вопрос №60 Современное состояние и перспективы развития элементной базы и средств вычислительной техники.

Вопрос №46 Назначение и структура микропроцессора. Устройство мп

Микропроцессор – центральное устройство ПК, предназначенное для управления работой всех блоков машины и для выполнения арифметических и логических операций над информацией.

Микропроцессор характеризуется: 1) тактовой частотой, определяющей максимальное время выполнения переключения элементов в ЭВМ; 2) разрядностью, т.е. максимальным числом одновременно обрабатываемых двоичных разрядов.

Разрядностть МП обозначается m/n/k/ и включает: m - разрядность внутренних регистров, определяет принадлежность к тому или иному классу процессоров; n - разрядность шины данных, определяет скорость передачи информации; k - разрядность шины адреса, определяет размер адресного пространства. Например, МП i8088 характеризуется значениями m/n/k=16/8/20; 3) архитектурой. Понятие архитектуры микропроцессора включает в себя систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы. Выделяют понятия микроархитектуры и макроархитектуры.

В общем случае под архитектурой ЭВМ понимается абстрактное представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных.

Описание и назначение процессоров

На самом деле то, что мы сегодня называем процессором, правильно называть микропроцессором. Разница есть и определяется видом устройства и его историческим развитием.

Первый процессор (Intel 4004) появился в 1971 году.

Внешне представляет собой кремневую пластинку с миллионами и миллиардами (на сегодняшний день) транзисторов и каналов для прохождения сигналов.

Назначение процессора – это автоматическое выполнение программы. Другими словами, он является основным компонентом любого компьютера.

Устройство процессора

Ключевыми компонентами процессора являются арифметико-логическое устройство (АЛУ), регистры и устройство управления. АЛУ выполнят основные математические и логические операции. Все вычисления производятся в двоичной системе счисления. От устройства управления зависит согласованность работы частей самого процессора и его связь с другими (внешними для него) устройствами. В регистрах временно хранятся текущая команда, исходные, промежуточные и конечные данные (результат вычислений АЛУ). Разрядность всех регистров одинакова.

Кэш данных и команд хранит часто используемые данные и команды. Обращение в кэш происходит намного быстрее, чем в оперативную память, поэтому, чем он больше, тем лучше.

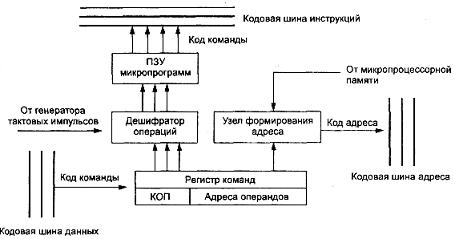

Структура микропроцессора Устройство управления Устройство управления является функционально наиболее сложным устройством ПК. Оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций во все блоки машины. Упрощенная функциональная схема УУ показана на рис. 4.5. Здесь представлены:

Рис. 4.5. Укрупненная функциональная схема устройства управления Регистр команд – запоминающий регистр, в котором хранится код команды: код выполняемой операции и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд. Дешифратор операций – логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов. Постоянное запоминающее устройство микропрограмм – хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК операций обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов. Узел формирования адреса (находится в интерфейсной части МП) – устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП. Кодовые шины данных, адреса и инструкций – часть внутренней интерфейсной шины микропроцессора. В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

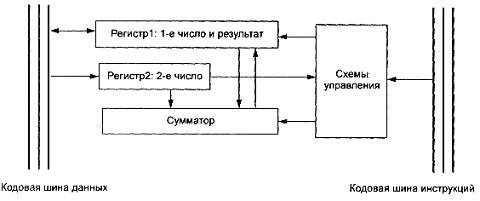

Арифметико-логическое устройство Арифметико-логическое устройство предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ (рис. 4.6) состоит обычно из двух регистров, сумматора и схем управления (местного устройства управления).

Рис. 4.6. Функциональная схема АЛУ Сумматор – вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова. Регистры - быстродействующие ячейки памяти различной длины: регистр 1 (Рг1) имеет разрядность двойного слова, а регистр 2 (Рг2) – разрядность слова. При выполнении операций в Рг1 помещается первое число, участвующее в операции, а по завершении операции – результат; в Рг2 – второе число, участвующее в операции (по завершении операции информация в нем не изменяется). Регистр 1 может и принимать информацию с кодовых шин данных, и выдавать информацию на них, регистр 2 только получает информацию с этих шин. Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ. АЛУ выполняет арифметические операции (+, -, *, :) только над двоичной информацией с запятой, фиксированной после последнего разряда, т.е. только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется или с привлечением математического сопроцессора, или по специально составленным программам. Микропроцессорная память Микропроцессорная память - память небольшой емкости, но чрезвычайно высокого быстродействия (время обращения к МПП, т.е. время, необходимое на поиск, запись или считывание информации из этой памяти, измеряется наносекундами – тысячными долями микросекунды). Она предназначена для кратковременного хранения, записи и выдачи информации, непосредственно в ближайшие такты работы машины участвующей в вычислениях; МПП используется для обеспечения высокого быстродействия машины, ибо основная память не всегда обеспечивает скорость записи, поиска и считывания информации, необходимую для эффективной работы быстродействующего микропроцессора. Микропроцессорная память состоит из быстродействующих регистров с разрядностью не менее машинного слова. Количество и разрядность регистров в разных микропроцессорах различны: от 14 двухбайтных регистров у МП 8086 до нескольких десятков регистров разной длины у МП Pentium . Регистры микропроцессора делятся на регистры общего назначения и специальные. Специальные регистры применяются для хранения различных адресов (адреса команды, например), признаков результатов выполнения операций и режимов работы ПК (регистр флагов, например) и др. Регистры общего назначения являются универсальными и могут использоваться для хранения любой информации, но некоторые из них тоже должны быть обязательно задействованы при выполнении ряда процедур. Интерфейсная часть микропроцессора Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав адресные регистры МПП, узел формирования адреса, блок регистров команд, являющийся буфером команд в МП, внутреннюю интерфейсную шину МП и схемы управления шиной и портами ввода-вывода. Порты ввода-вывода – это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65536. Каждый порт имеет адрес – номер порта, соответствующий адресу ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера. Порт устройства содержит аппаратуру сопряжения и два регистра памяти – для обмена данными и обмена управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и др.) имеют постоянно закрепленные за ними порты ввода-вывода. Схема управления шиной и портами выполняет следующие функции:

Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данных системной шины: при доступе к порту МП посылает сигнал по КШИ, который оповещает все устройства ввода-вывода, что адрес на КША является адресом порта, а затем посылает и сам адрес порта. То устройство, адрес порта которого совпадает, дает ответ о готовности, после чего по КШД осуществляется обмен данными. |

|

|