- •Помехоустойчивое кодирование в современных системах передачи данных.Реализация кодера и декодера ldpc (low-density parity-check)

- •Введение

- •1 Практическая часть

- •2 Преимущества ldpc-кодов, их применение и перспективы развития

- •3 Исследование принципов реализации ldpc кодека на плис

- •3.1 Описание кодера и декодера

- •3.2 Структурная схема кодера на плис

- •3.2 Структурная схема декодера

- •3.3 Моделирование

- •3.4 Зависимость от количества итераций декодирования

- •3.5 Зависимость от наличия дискретизатора на входе декодера

- •3.6 Зависимость от типа используемого декодера

- •Заключение

- •Список литературы

3.1 Описание кодера и декодера

Как любой LDPC код, данный код описывается проверочной матрицей H, которая состоит из линейно-независимых строк. Выход сформирован из проверочных символов, плюс точная копия информационных битов (код систематический). Пусть на вход кодера поступает последовательность длиной k, а на выходе декодера кодовая

последовательность длиной n, тогда скорость определяется отношением: r=k/n. Проверочная матрица H состоит из подматриц размера MxM. Генераторная матрица G состоит из единичной матрицы размера MK*MK (K выбирается в зависимости от скорости кода: K=2 для скорости 1/2, K=4 для скорости 2/3, K=8 для скорости 4/5) и квазициклической матрицы W. Чтобы закодировать исходное сообщение, необходимо его умножить на генераторную матрицу. Матрица W является квазициклической размера m×m(так же, как и матрица H), где m=M/4, что позволяет при кодировании не умножать вектор на матрицу (эта задача требует слишком много ресурсов и времени), а выполнить кодер на основе регистров сдвига. Потребуется 2M/m=8 регистров сдвига длины m, сумматор и умножитель по модулю 2. В регистрах сдвига хранятся значения циклических подматриц порождающей матрицы. Рассматриваемый код для декодирования использует алгоритм «мягкий вход – мягкий выход» (Soft Input – Soft Output - SISO)

Этот метод позволяет осуществить непрерывное улучшение способности исправления, когда процесс декодирования повторяется, т.к. в процессе исправления ошибок передаётся больше информации от выхода одного декодера к входу следующего.

Фильтрованный сигнал подается к декодерам, и декодеры обрабатывают амплитуду сигнала для реализации мягкого решения. При этом используются априорные вероятности входных символов и мягкий выход. Мягкий выход предоставляет собой вещественное число, которое является мерой надёжности жёсткого решения декодера.

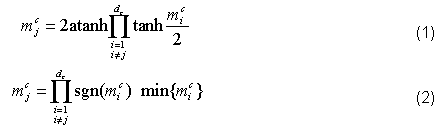

Декодер Sum-Product для вычисления метрик необходимых для декодирования использует сложно реализуемые на ПЛИС математические функции (1), алгоритм minsum (минимум-сумма) является аппроксимацией алгоритма sum-product (сумма-произведение) и использует для вычисления метрик только функции сравнения и сложения (2), которые легко реализуются на ПЛИС. Далее на этапе моделирования в среде MATLAB сравнивается эффективность этих алгоритмов декодирования для канала с гауссовым шумом.

3.2 Структурная схема кодера на плис

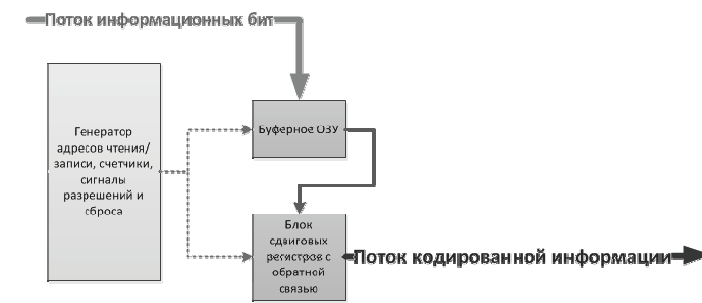

На Рис. 3.1 изображена структурная схема кодера на ПЛИС. Основные элементы кодера:

• оперативное запоминающее устройство (ОЗУ) – буфер данных на два информационных блока (2*1024 бит),

• Буфер на два блока необходим для того, что бы мы могли считывать текущий блок данных и записывать следующий, это необходимо для потоковой работы кодера (без пауз).

• генератор адресов чтения и записи ОЗУ, сигналов разрешений записи (ОЗУ), флагов инициализации и сброса для вычислительных блоков,

• блок сдвиговых регистров

Рисунок 3.1 - Структурная схема кодера

3.2 Структурная схема декодера

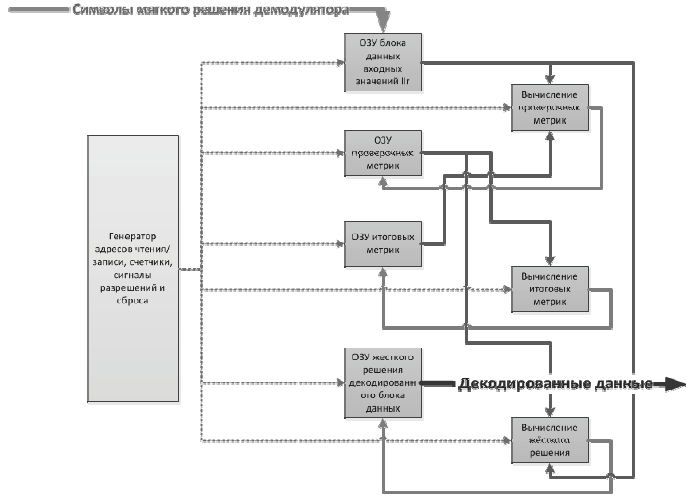

На нулевой итерации декодер обрабатывает канальную последовательность и вычисляет проверочные метрики, из них итоговые, далее процесс повторяется заданное количество раз (итераций). Так с каждой итерацией средняя вероятность ошибки на информационный бит постепенно уменьшается. В модели кодека для сравнения эффективности после каждой операции вычисляется жёсткое решение (в реальном кодеке такой необходимости нет, и поэтому жёсткое решение вычисляется только на последней итерации).

Рисунок 3.2 -Структурная схема декодера

На Рис. 3.2 изображена структурная схема декодера. Основные элементы декодера:

• 4 оперативных запоминающих устройства (ОЗУ):

• буфер данных мягкого решения демодулятора на два кодовых блока (2*2048 бит),

• память для хранения проверочных и итоговых метрик (7680+7680)

• память для хранения 2-х блоков жестких решений (текущего и предыдущего блоков) (2*1024 бит)

• Буфер на два блока необходим для того, что бы мы могли считывать текущий блок данных и записывать следующий, это необходимо для потоковой работы декодера (без пауз).

• генератор адресов чтения и записи ОЗУ, сигналов разрешений записи (ОЗУ), флагов инициализации и сброса для вычислительных блоков,

• блоки вычисления проверочных и итоговых метрик и жёсткого решения.

Скорость декодирования

• R = ½; тактовая частота f~130МГц (При использовании ПЛИС Xilinx Virtex-4 xc4vsx55),

• Время одной итерации ~7695*2 тактов

• Задержка декодирования ~ 7695*2*(I+1) тактов (I – число итераций),

• Cкорость информационного потока на выходе декодера f*1024/(7695*2*(I+1)) бит/с,