- •Классификация современных мп.

- •Организация мп систем

- •Організація однокристального мікроконтролера мсs-51. Типи пам'яті. Карта пам'яті. Режими адресації. Особливості системи команд: команди пересилання.

- •Команды пересылки данных.

- •Регістрова структура мікроконтролера мс5-51. Особливості системи команд: арифметичні команди, логічні команди, бітові операції, команди передачі керування.

- •Блок регистров специальных функций(sfr)

- •Однокристальний мікро контролер mcs-51: порти вводу-виводу, система переривань. Службові регістри переривань, процедура обробки переривань.

- •Регистр приоритетов прерываний (ip)

- •Однокристальний мікро контролер mcs-51: система таймерів-лічильників. Структура таймерів-лічильників. Службові регістри. Режими роботи. Приклад обробки переривань від таймера 0.

- •2.7 Платформа java. Створення та виконання програм. Принципи об’єктно-орієнтованого підходу. Інкапсуляція. Композиція. Наслідування. Поліморфізм.

- •Платформа java. Типи даних. Організація пам’яті. Структура класів. Статичні елементи. Конструктори. Абстрактні класи та інтерфейси. Внутрішні класи. Все является объектом

- •Примитивные типы (примитивы)

- •Создание новых типов данных

- •Поля и методы

- •Методы, аргументы и возвращаемые значения

- •Ключевое слово static

- •Статические методы

- •Конструктор гарантирует инициализацию

- •Класс Class

- •Абстрактные классы и методы

- •Интерфейсы

- •Внутренние классы Вложенные классы (Inner)

- •Классы, вложенные в методы (локальные внутренние классы)

- •Анонимные внутренние классы

- •Статические внутренние классы (nested)

- •Компоненты и контейнеры

- •Диспетчеры компоновки

- •Обработка событий

- •Платформа java: потоки вводу-виводу, Класифікація потоків. Класи-фільтри. Байтові та текствові потоки. Потоки ввода/вывода и файлы

- •Классификация классов ввода-вывода

- •Потоки фильтров

- •Текстовые потоки

Основнвні типи архітектур мікропроцесорних систем. Класифікація мікропроцесорів. Організація мікропроцесорної системи. Двох- і трьохшинна архітектура. Сполучення портів вводу-виводу і пам'яті з процесором.

Основные типы архитектур микропроцессорных систем.

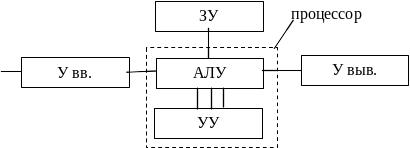

1 ТИП: Архитектура фон – Неймана

У

ЗУ – запоминающее устройство;

АЛУ – арифмет. логич.устройство;

УУ – управляющее устройство.

Эта архитектура характериз.тем, что для хранения прогр.(команд) данных исп.одна область памяти.

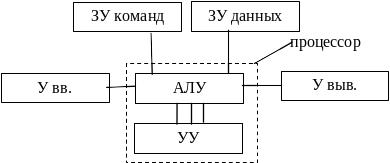

2 ТИП: Гарвардская архитектура

Эта архитектура характериз.тем, что для хранения прогр.(команд) данных исп.разные области памяти.

Классификация современных мп.

Делятся на три класса:

Секционирование с микропрогр.управлением.

2)Однокрист. процессоры с прогр.управл.

RISC (reduced instruction set comp.)

Закон 80/20: - 80% - времени выполняется; 20% - команды.

Основные признаки RISC архитектуры, так как команды простые, то:

- исполнение за 1 такт;

- управление аппаратное;

- упрощенный набор инструкций методом адресации;

- все команды одной длины, позволяет сделать короткий и быстрый конвейер;

- большое кол-во внутр.регистров 64-128.

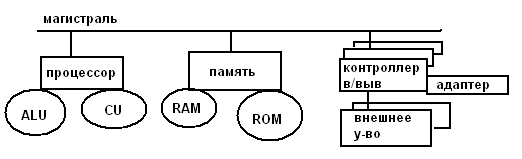

Организация мп систем

ALU – выполняет арифмет.операции.

Память служит для хранения прогр.и данных.

Каждая ячейка имеет адрес(байты). В каждой ячейке хранится одно фи

ксиров.слово машинной длины 8, 16, 32, 64…-это кол-во информации, которой можно обменяться за одно обращение.

2 – х шинная и 3 – х шинная системы.

Шина – часть магистрали, есть 3 типа:

- AB – шина адреса;

- DB – шина данных;

- CB – шина управления.

3-х шинная структура

Helster A,C,D

– формирует адрес, посылает данные Slave D

– принимает данные (память и порт

вв/выв).

Адрес и данные подаются по одной дорожке,

т.е.совмещается адресная шина и шина

данных. «+» - экономия кол-ва

ножек на плате и разъемов «-» - усложнения схемы

обмена вв/выв

2-х шинная структура

Преобразование 2-х шинной структуры в 3-х шинную.

Вхідні і вихідні каскади мікропроцесорних елементів. Еквівалентні схеми вихідних каскадів. Діапазони логічних рівнів. Підвищення завадостійкості мікропроцесорних систем. Виходи з трьома станами та відкритим колектором. Сполучення цифрових та аналогових пристроїв з мікропроцесорними системами.

Устройство выходных каскадов цифрових схем:

С ерия

TTL

ерия

TTL

Это схемотехн.реализация логической схемы «И».

Хотя бы один «0» дает на выходе «0».

Входной ток «0», Iвх0=-1,6мА – прямой ток диода

Обратный ток «1», ток закрытого диода

Iвх1=40мкА

|Iвх0| > |Iвх1|

Серия CMOS

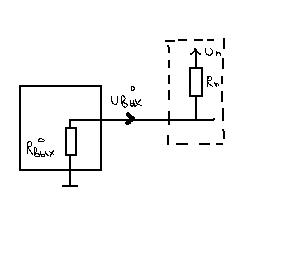

Эквивалентные

схемы выходных каскадов

Эквивалентные

схемы выходных каскадов

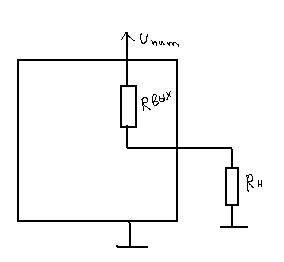

Un-Uвых=Iвых(1)Rвых

Uвых(1)= Un- Iвых(1)Rвых

С увеличением Iвых(1) , Uвых(1) уменьшается

Uвых(0)=

Un-

Iвых(0)Rвых(0)

Uвых(0)=

Un-

Iвых(0)Rвых(0)

С увеличением Iвых(0) , Uвых(0) увеличивается

Uвых(0) и Uвых(1) зависят от Iвых. Для кодирования 0 и 1 используются не урони напряжения, а діапазон уровней напряжений. Например, для мікросхем, віполненіх по технологи ТТЛ(ш)

Источники помех в цифровых схемах – паразитные емкости внутри цепи. Любое переключение ключей из-за паразит.емкостей дает бросок тока в пров. Напряжения или земли.

Также дорожки имеют паразитную индуктивность.

Защита от помех:

- возле каждой схемы ставится конденсатор-бесперебойник;

- для защиты по цепи питания – фильтрующие конденсаторы;

- запас по помехоустойчивости;

- разные вх. и вых. напр. «0» и «1»;

- мин.необходимое быстродействие;

- конструктивные меры.

В некоторых микросхемах есть возможность разомкнуть оба ключа (0-я и 1-цы).

Z(3-е) состояние – когда ключ «1» и «0» разомкнуты, имеет высокое сопротивление.

Используется для подключения нескольких микросхем, для прием данных на шыну с конретной микросхемы, когда остальные в z-сост.

- открытый коллектор

- вых.каскад с открытым коллектором

Все «1» на линии дают «1» на выходе,

Если «0», на выходе «0». Схема «монтажного И»

Поставив инверторы, получают «монтажное ИЛИ»

+ обьединение вых.без стробирющих сигналов CS

- низкое быстродействие при переходе из «1» в «0»