1) Вычислительная техника, совокупность технических и математических средств, методов и приёмов, используемых для облегчения и ускорения решения трудоёмких задач, связанных с обработкой информации, в частности числовой, путём частичной или полной автоматизации вычислительного процесса; отрасль техники, занимающаяся разработкой, изготовлением и эксплуатацией вычислительных машин.

Наиболее существенно применение средств Вычислительная техника в системах автоматического управления при сборе, обработке и использовании информации с целью учёта, планирования, прогнозирования и экономической оценки для принятия научно обоснованных решений.

2) Информация в технике – сообщение, передаваемое в форме знаков и символов.

И

Н

П

Источник носитель приемник

Виды информации:

1. По уровню сложности:

А) сигнал

Б) сообщение

В) информационный массив

Г) информационный ресурс

2. По типу сигналов:

А) аналоговая

Б) цифровая

3) По уровням доступа и организации:

А) данные в регистровой памяти

Б) данные в ОП

В) файлы данных на внешних устройствах

Г) базы данных

4) По способам кодирования и представления

А) цифровая

Б) символьная

В) графическая

5) По организации данных

А) табличная

Б) текстовая

В) графическая

Минимальная единица информации – бит.

Килобайт – 1024 байт

Мегабайт – 1024килобайт

Гигабайт – 1024 мегабайт

3) Используется двоичное и троичное представление сигналов

001 001

3.5 + +

1.5 - - - -

двоичное -

троичное

Реальный электронный импульс

Передний

положительный фронт сигнала

Передний

положительный фронт сигнала

Передача данных – физический перенос данных в виде сигналов от точки к точке или от точки к нескольким точкам средствами электросвязи по каналу связи.

Синхронная передача данных – базируется на согласовании таймеров передающего и принимающего устройств. Пари этом биты передаются кадрами.

Асинхронный – передача осуществляется между двумя точками. Информация передаётся порциями, следующая порция передается только после того, как передалась предыдущая порция.

Асинхронная является более простой, но при этой передаче снижается скорость.

5) Код – совокупность знаков, символов и правил представления информации.

правила

с

имвол знаки

имвол знаки

Классификация:

1) По пространственно-временному представлению

А) последовательный (код Морзе)

Б) параллельный (код от мыши к компьютеру)

2) По количеству символов:

А) ASCII

Б) UNI CODE (16-ти разрядное представление символов)

При последовательном коде каждый временный такт предназначен для отображения одного разряда слова. Здесь все разряды слова фиксируются по очереди одним и тем же элементом и проходят через одну и ту же линию передачи (2-ух жильный кабель)

При параллельном коде все знаки символа представляются в одном временном такте, каждый знак проходит через отдельную линию (4-ех жильный кабель), образуя символ.

Для последовательного кода характерно временное разделение каналов при передачи информации, для параллельного – пространственное.

UNICODE захватывает 28 000 букв, знаков, слогов, иероглифов, национальных языков мира , около 25 000 мест в UNICODE зарезервировано. Использование этого резерва дает возможность пользователям вводить математические или технические символы, а также создавать свои собственные символы.

Избыточные коды

Применяются для повышения надежности передачи данных

1) Коды с обнаружением ошибок: корректирующие коды: символы

А) код четности или нечетности

Б) CRC – контрольная сумма

В коде по четным записывается 1, если нечетные – 0

Пример: код Рида – Соломона Хеллинга

ECC позволяет:

1) обнаружить 1 ошибочный бит

2) устранить ошибку

6) Системы счисления

СС – способ именования и изображения чисел с помощью символов, имеющих определенные количественные значения.

В зависимости от способа изображения чисел СС делятся на:

- позиционные

- непозиционные

Непозиционные СС.

В этом случае цифры не меняют своего количественного значения при изменении их расположения в числе.

Самый простой пример – СС, где количество обозначается палочкой.

Непозиционные СС.

Здесь количественное значение каждой цифры зависит от ее размещения (позиции) в числе.

Десятичная СС является позиционной, так как значение каждой цифры зависит от ее места (позиции) в числе.

Основание СС – количеств (P) различных цифр, используемых изображения числа в позиционной СС. Значения цифр лежат в пределах от 0 до P-1.

Нижние индексы определяют местоположение цифры в числе (разряд).

Двоичная СС.

Имеет основание P=2 и использует для представления две цифры 0 и 1.

Двоично - десятичная СС.

При сложении 2-10 чисел каждый раз, когда происходит перенос бита в старший полубайт, необходимо и полубайту, от которого произошел перенос, добавить корректирующее значение 0110.

При сложении 2-10 чисел каждый раз, когда встречается недопустимая для полубайта комбинация, необходимо к каждой недопустимой комбинации добавить корректирующее значение 0110 с разрешение переноса в старшие полубайты.

Пример:

0011100100100111

+

010010001010110

010010001010110

1000000010111101

0110 0110

0110 0110

1000011110000011

D = 3927 = 0011 1001 0010 0111

С = 4856 = 0100 1000 0101 0110

7) Формы представления чисел в ЭВМ. Алгебраическое представление чисел.

В ЭВМ применяется двоичная система счисления. Применяются две формы представления чисел: естественная форма или форма с фиксированной запятой (точкой) и нормальная форма или форма с плавающей запятой (точкой). Фиксированная запятая: числа изображаются в виде последовательности цифр с постоянным для всех чисел положением запятой, отделяющей целую часть от дробной. Например: пусть числа представлены в десятичной СС и имеют 5 разрядов в целой части числа, и 5 в дробной . Числа записанные в такую разрядную сетку имеют вид: +00721.35500, +0000.00328,-10301.20260. Эта форма наиболее проста, естественна, но имеет небольшой диапазон представления чисел, поэтому чаще всего не приемлема при вычислениях. В памяти ЭВМ числа с фиксированной точкой хранятся в 3 форматах: полуслово - обычно 16 бит или 2 байта, слово-32 бита или 4 байта, двойное слово-64 бита или 8 байтов. Отрицательные числа с фикс. точкой записываются в разрядную сетку в дополнительных кодах, которые образуются прибавлением 1 к младшему разряду обратного кода. Плавающая запятая(точка): число изображается в виде двух групп цифр: мантисса; порядок. При этом абсолютная величина мантиссы должна быть меньше 1, а порядок должен быть целым числом. Например: приведенные ранее числа в нормальной форме запишутся следующим образом: +0,721355х103 , +0,328х10-3 и т.д. нормальная форма представления обеспечивает большой диапазон отображения чисел и является основной в современных компьютерах. Все числа с плавающей запятой хранятся в машине в так называемом нормализованном виде. Нормализованный- такое число, в старшем разряде мантиссы которого стоит больше нуля. У нормализованных двоичных чисел, следовательно: 0,5 <|M|<1. Нормализованные, т.е. приведенные к правильной дроби числа: 10,3510=0,103510х10+2; 0,000072458=0,72458х8-4В памяти ЭВМ числа с плавающей точкой хранятся в двух форматах: слово и двойное слово. Разрядная сетка для чисел имеет следующую структуру: нулевой разряд-это знак числа(0-минус,1-плюс). С 1по7 разряд записываются порядок в прямом двоичном коде, пустые разряды заполняются нулями. В первом разряде указывается знак порядка(1-плюс, 0-минус). С 8 по 31(63) указывается мантисса, слева направо без нуля целых в прямом двоичном коде и для отрицательных чисел, и пустые разряды заполняются нулями.

Алгебраическое представление двоичных чисел: для представления чисел с учетом их знака, в вычисл. машинах используются специальные коды: прямой, обратный и дополнительный. При этом 2 последних кода позволяют заменить неудобную для компьютера операцию вычитания на операцию сложения с отрицательным числом. Дополнительный код обеспечивает более быстрое выполнение операции, поэтому в ЭВМ чаще применяется именно он. Знак числа обычно кодируется двоичной цифрой, при этом: код 0 означает +, код 1 означает -, . Если при сложении в ЭВМ оба слагаемые имеют одинаковый знак, то операция сложения выполняется обычным путем. Если при сложении слагаемые имеют разные знаки, то сначала необходимо выявить большее по абсолютной величине число, из него произвести вычитание меньшего по абсолютной величине числа и разности присвоить знак большего числа. Выполнение операций умножения и деления в прямом коде выполняется обычным образом, но знак результата определяется по совпадению или несовпадению знаком учувствовавших в операции чисел. Операцию вычитания в этом коде нельзя заменить операцией сложения с отрицательным числом, поэтому возникают сложности связанные с займом значений из старших разрядов уменьшаемого числа. В связи с этим прямой код в ЭВМ почти не применяется. Обратный код: если число >0,тогда обратный код будет: =0,а1,а2,а3.., если число<0, тогда=1,инверсии(а1,а2,а3…)Для того чтобы получить обратный код отрицательного числа, необходимо все цифры этого числа инвертировать, т.е. в знаковом разряде поставить 1, во всех значащих разрядах 0 заменить 1, а 1 на 0. Например: 1011=0,1011; -1011=1,0100. Для получения дополнительного кода отрицательного числа необходимо все символы этого числа инвертировать, кроме последней(младшей) единицы и тех нулей, которые следуют за ней.

8) Машинная арифметика. Операции сложения, вычитания. Выполнение сложения в двоично-десятичной СС: Следует обратить внимание на аналогию в правилах выполнения арифметических действий в двоичной и десятичных СС: если при сложении двух двоичных чисел(представленных в двоичной СС)сумма цифр окажется больше единицы, то возникает перенос в старший разряд, если уменьшаемая цифра меньше вычитаемой, то нужно сделать заем единицы в старшем разряде. Умножение: так как очередная цифра множителя может быть только 1 или 0, то промежуточное произведение равно либо множимому, либо 0. Таким образом операция умножения в двоичной системе фактически не производится: в качестве промежуточного произведения записывается либо множимое, либо 0, затем промежуточные произведения суммируются. Иначе говоря, операция умножения заменяется последовательным сложением. Для вычитания используется дополнительный код, который позволяет эту операцию свести к сложению чисел. Правило вычитания с доп.числом: чтобы вычесть число А из числа В, достаточно сложить В с дополнительным числом с А, и отбросить перенос в соседний старший разряд. Например: чтобы вычесть 623 из 842, достаточно сложить 842 с 377, отбросив перенос получим 219.(842-623=219) Таким образом важнейшее преимущество двоичной арифметики заключается в том, что она позволяет все арифметические действия свести к одному-сложению, а это значительно упрощает устройство процессора ЭВМ. Эти основные принципы положены в основу функционирования элементов и узлов ЭВМ( триггер, сумматор, полусумматор).

Двоично-десятичная арифметика: Для записи одного десятичного разряда используется четыре двоичных бита. Эти 4 бита называют тетрадой. С помощью 4 битов можно закодировать 16 цифр. Лишние комбинации в двоично-десятичном коде являются запрещенными. Суммирование двоично-десятичных чисел можно производить по правилам обычной арифметики, а затем выполнять двоично-десятичную коррекцию. При этом осуществляется проверка каждой тетрады на допустимые коды и если в какой либо тетраде обнаруживается запрещенная комбинация, это- наличие переполнения и необходимость произвести двоично-десятичную коррекцию. Двоично-десятичная коррекция заключается в дополнительном суммировании числа 0110-шесть(число запрещенных комбинаций) с тетрадой, в которой произошло переполнение или произошел перенос в старшую тетраду.Пример: 18+13=31 Сложение тетрад: 00011000+00010011=00101011 Коррекция: 00101011+00000110=00110001

9) Логические функции. Таблицы истинности. Свойства операций с логическими функциями. Алгебру высказывания называют булевой алгеброй. Основу математической логики составляет алгебра высказываний. Это освобождает матлогику от неопределенности в толковании логических выражений, показывающих связь между отдельными суждениями и понятиями. Алгебра логики используется при построении основных узлов ЭВМ(дешифратор, сумматор0 ,шифратор) Алгебра логики оперирует с высказываниями. Под высказыванием понимают повествовательное предложение, относительно которого можно утверждать истинно оно или ложно. К примеру: выражение 5<2-ложно. Преобразование информации в ЭВМ осуществляется элементами(схемами) двух классов: комбинационными, последовательностными (схемы с памятью). Состояние выходов комбинационных схем однозначно определяется состояниями входов в данный момент времени. Состояние выходов в последовательностных схемах определяется не только состоянием входов, но и внутренними состояниями имевшими место в предыдущие моменты времени. Логический элемент компьютера - это часть электронной схемы, которая реализует элементарную логическую функцию. Логическими элементами компьютеров являются электронные схемы И,ИЛИ,НЕ, И-НЕ,ИЛИ-НЕ или другие(называемые так же вентилями), а так же триггер. С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает 2-8 входов, и 1-2 выхода. Конъюнкция: Соединение двух(или нескольких) высказываний в одно с помощью союза И(&)называется операцией логического умножения. Единица на выходе «И» будет тогда, и только тогда, когда на всех входах будут 1. Дизъюнкция: объединение двух(или нескольких) высказываний с помощью союза ИЛИ. Когда хотя бы на одном входе схемы «ИЛИ» будет 1, на её выходе тоже будет 1. Инверсия: присоединение частицы НЕ к некоторому высказыванию. Схема «НЕ»(инвертор) реализует операцию отрицания. Вентили: схема «И-НЕ»: осуществляет отрицание результата схемы «И». «Или НЕ»: состоит из элемента ИЛИ и инвертора, и осуществляет отрицание результата схемы «ИЛИ». «Искл. Или »:соответствует «сложению по модулю два» результат равен 0, если оба операнда равны; во всех остальных случаях результат равен 0. y:= ( инверсия( Х1)&Х2)v(инверсия (Х2)&Х1). «Искл. Или НЕ»:является отрицанием результата схемы «Искл.ИЛИ». Импликация: или логическое следование, иначе

говоря

«Если А, то Б» Таблица истинности:

001,011,100,111. Операция эквиваленции: (A≡B)или

(А~В) таблица истинности: 001,010,100,111.

Свойства операций:

коммутативность(перестановочность):

A&B

=B&A.

AvB=BvA.

Ассоциативный(сочетательный):

Av(BvC)=(AvB)vC=AvBvC.

Дистрибутивный(распределительный):

A&(BvC)=(A&B)v(A&C).

Идемпотентность: A&A=A,

AvA=A.

Двойное отрицание: A=A.

Поглощение: Av(A&B)=A,

A&(AvB)=A.

Склеивание: (A&B)v(инверсия(A)&B)=B,

(AvB)&(инверсия(А)vB).

Операция переменной с её инверсией:

A&инверсия(А)=0,

Av

инверсия(А)=1. Операция переменной с ей

константой: A&1=A,

A&0=0,

Av0=A,

Av1=1.

Законы де Моргана: инверсия(A&B)=

инверсия(А)v

инверсия(В), инверсия(AvB)=инверсия(А)&

инверсия (В).

10) Синтез и оптимизация логических схем: При построении схемы, реализующей произвольную таблицу истинности, каждый выход анализируется( и строится схема) отдельно. Для реализации таблицы истинности с помощью логических элементов «И» достаточно рассмотреть только те строки таблицы истинности, которые содержат 1 в выходном сигнале. Строки содержащие на выходе 0, в построении схемы не учавствуют. Каждая строка, содержащая в выходном сигнале 1, реализуется схемой логического «И» с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы описанные в таблице истинности логической 1, подаются на этот вход этой схемы непосредственнО, а входные сигналы, описанные в таблице логическим 0, подаются на вход через инверторы. Объединение сигналов выходов схем, реализующих отдельные строки таблицы истинности, производится с помощью логического «ИЛИ». Количество строк в этой схеме определяется количеством строк в таблице истинности, в которых в выходном сигнале присутствует логическая 1. Пример: рисунки 1 и 2. Необходимо реализовать таблицу истинности приведенную в таблице 1. Для построения схемы, реализующей сигнал у1, достаточно рассмотреть строки выделенные светлой штриховкой. Эти строки реализуются сборкой(микросхемой) S2 на рисунке 2. Каждая строка реализуется своей схемой «И», затем выходы этих схем объединяются. Для построения схемы реализующей сигнал у2, достаточно рассмотреть строки имеющие более темную штриховку. Эти строки реализуются сборкой S3. Инвертирование входов схемы осуществляется сборкой S1. В частности здесь: y1=(x1&x2&x3&x4)v(x1&x2& x3&x4)v(x1&x2&x3&x4) и т.д.(подчеркивание в формулах означает инверсию)

Преобразование логических формул: служит для упрощения формул приведения их к определенному виду путем использования основных законов алгебры логики. Под упрощением формулы, не содержащей операций импликации и эквиваленции, понимают равносильное преобразование, приводящее к формуле, которая содержит по сравнению с исходной меньшее число операций конъюнкции и дезъюнкции и не содержит отрицаний неэлементарных формул, либо содержит меньшее число вхождений переменных. Некоторые преобразования похожи на преобразования формул в обычной алгебре(вынесение общего множителя, использование переместительного и сочетательного законов и т.п.), тогда как другие преобразования основаны на свойствах, которыми не обладают операции обычной алгебры( использование распределительного закона для конъюнкции, свойства поглощения и склеивания, законы де Моргана и др.) Примеры: 1) xvy&(x&y)=x&y&(x&y)=x&x&y&y=0&y&y=0&y=0(законы алгебры логики применяются в следующей последовательности: закон де Моргана, сочетательный закон, правило конъюнкции переменной с её инверсией и правило операции с константами), 2) x&yvxvyvx=x&yvx&yvx=x&(yvy)vx=xvx=1 (применяется правило де Моргана, выносится за скобки общий множитель, используется правило операций переменной с ей инверсией), 3)(xvy)&(xvy)&(xvy)=(xvy)&(xvy)&(xvy)&(xvy)=y&x (повторяется второй сомножитель, что разрешено законом идемпотенции, затем комбинируются два первых и два последних сомножителя и используется закон склеивания). Все законы описываются во второй половине 9 билета.

Минимизация

логического выражения: целью минимизации

является уменьшение стоимости её

реализации(количества используемых

логических элементов)Общая схема

процесса реализации лог-ой функции :

для неё составляется сумма произведений,

или дизъюнктивная совершенная нормальная

форма. Затем полученное выражение

минимизируют до эквивалентной минимальной

суммы произведений. При оценке стоимости

выражения учитывается общее количество

вентилей и их входных значений(входных

линий), необходимых для реализации

выражения в форме. С тоимость

большой схемы равна 21.(5 вентилей+16

входных значений). Инверсия входных

значений при подсчете игнорируется.

Стоимость более простого выражения

равна 9(3 вентиля+6входных значений).

Сумма произведений считается минимальной,

если не существует эквивалентного ей

выражения меньшей стоимости. Стратегия

упрощения заключается в следующем:

прежде всего термы-произведения

разбиваются на пары, отличающиеся единой

переменной, которая в одном терме стоит

со знаком –(инверсия(х)), а во втором

без него(х). Затем в каждой паре общее

произведение двух переменных выносится

за скобки, а в скобках остается терм:

инверсия(х)+х, всегда равный 1. Вот что

получим применив эту процедуру к первому

выражению для функции

f1=(x1&x2&x3)v(x1&x2&x3)v(x1&x2&x3)v(x1&x2&x3)=x1&x2&(x3vx3)v(x1&x1)&x2&x3=x1&x2&1v1&x2&x3=x1&x2vx2&x3

Это выражение минимально. Соответствующая

ему логическая схема приведена на

рисунке 2(маленькая схемка такая)

тоимость

большой схемы равна 21.(5 вентилей+16

входных значений). Инверсия входных

значений при подсчете игнорируется.

Стоимость более простого выражения

равна 9(3 вентиля+6входных значений).

Сумма произведений считается минимальной,

если не существует эквивалентного ей

выражения меньшей стоимости. Стратегия

упрощения заключается в следующем:

прежде всего термы-произведения

разбиваются на пары, отличающиеся единой

переменной, которая в одном терме стоит

со знаком –(инверсия(х)), а во втором

без него(х). Затем в каждой паре общее

произведение двух переменных выносится

за скобки, а в скобках остается терм:

инверсия(х)+х, всегда равный 1. Вот что

получим применив эту процедуру к первому

выражению для функции

f1=(x1&x2&x3)v(x1&x2&x3)v(x1&x2&x3)v(x1&x2&x3)=x1&x2&(x3vx3)v(x1&x1)&x2&x3=x1&x2&1v1&x2&x3=x1&x2vx2&x3

Это выражение минимально. Соответствующая

ему логическая схема приведена на

рисунке 2(маленькая схемка такая)

11) Интегральные микросхемы: основой электронных технологий являются полупроводники(п\п)-вещества, электропроводимость которых увеличивается с ростом температуры и является промежуточной между проводимостью металлов и изоляторов. Связь электронов в п\п может быть разорвана различными внешними воздействиями: светом, потоком быстрых частиц, электрическим полем и т.д. П\п очень чувствительны к дефектам в кристаллах и примесям. Наиболее часто используемыми в электронике п\п-ами являются кремний и германий. На их основе путем внедрения примесей в определенных точках кристаллов создаются разнообразные п/п-ые элементы, к которым относятся: 1)проводники, коммутирующие активные элементы 2)вентили, выполняющие логические операции, 3)приборы с зарядовой связью(ПЗС), предназначенные для кратковременного хранения электрического заряда и используемые в светочувствительных матрицах видеокамер, 4) диоды и др. В настоящее время используется несколько технологий построения логических элементов: 1)транзисторно-транзисторная логика(ТТЛ), 2)логика на основе комплементарных МОП-транзисторов(КМОП,CMOS), 3) логика на основе сочетания комплементарных МОП- и биполярных транзисторов( BiCMOS). Наибольшим быстродействием и наименьшей помехоустойчивостью обладала технология ЭСЛ(эмиттерно-связанная логика). Принципиальная ее особенность приводит к тому, что в процессе работы накапливаются и усиливаются шумы транзисторов, а это означает что достаточно сложные алгоритмы работы возможно будут выполнятся с ошибками. В настоящее время эта технология производства применяется весьма редко. Следующий вид технологии производства цифровых микросхем-это ТТЛ.Обладают быстродействием соизмеримым с ЭСЛ. Однако энергопотребление микросхемы в этом случае не зависит от скорости переключения логических элементов-решая задачу, требующую высокого быстродействия, или в которой вентили переключаются только несколько раз в секунду, микросхема потребляет одинаковый ток. Наибольшее распространение получила технология CMOS(КМОП-комплементарные транзисторы с изолированным затвором), особенностью которой является то, что микросхемы построены по двухтактной схеме. Поэтому в статическом состоянии если один из транзисторов открыт, то закрыт второй, и наоборот. Это означает что ток через вентиль не протекает ни в состоянии логической , ни в состоянии 0, а в состоянии покоя через микросхему протекают только токи утечки транзисторов. Потребление микросхем КМОП возрастает только при увеличении скорости переключения логических вентилей. При предельных скоростях работы её потребление сравнивается и даже может превосходить потребление микросхем, выполненных по ТТЛ-технологии. Именно поэтому в настоящее время подавляющее большинство микросхем выпускается именно по этой технологии. Интегральные микросхемы, содержащие более 100 элементов, принято называть микросхемами повышенного уровня интеграции, используется также термин «большие интегральные схемы» (БИС) он соответствует четвертой-пятой степеням интеграции .Микросхемы повышенного уровня интеграции имеют по сравнению с микросхемами малого уровня интеграции значительно лучшие габаритные характеристики, меньшую стоимость в расчете на один функциональный элемент, а также ряд других преимуществ благодаря которым удается существенно улучшить основные технико-экономические характеристики аппаратуры. Вид обрабатываемого сигнала: Аналоговые , Цифровые , Аналого-цифровые . Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания. Цифровые микросхемы — входные и выходные сигналы могут иметь два значения: логический ноль или логическая единица, каждому из которых соответствует определённый диапазон напряжения. Например, для микросхем типа ТТЛ при напряжении питания +5 В диапазон напряжения 0…0,4 В соответствует логическому нулю, а диапазон 2,4…5 В — логической единице; а для микросхем ЭСЛ-логики при наприяжении питания −5,2 В диапазон −0,8…−1,03 В — логической единице, а −1,6…−1,75 В — логическому нулю.Аналого-цифровые микросхемы совмещают в себе формы цифровой и аналоговой обработки сигналов .Назначение :Интегральная микросхема может обладать законченным, сколь угодно сложным, функционалом — вплоть до целого микрокомпьютера (однокристальный микрокомпьютер ). Аналоговые схемы: Операционные усилители ,генераторы сигналов, Фильтры (в том числе на пьезоэффекте ) ,Аналоговые умножители, Стабилизаторы источников питания, Микросхемы управления импульсных блоков питания ,Преобразователи сигналов .Цифровые схемы: Логические элементы, Триггеры, Счётчики , Регистры , Буферные преобразователи, Модули памяти , Шифраторы, Дешифраторы , Микроконтроллеры (Микро)процессоры (в том числе ЦПУ в компьютере), Однокристальные микрокомпьютеры . Модули памяти на основе БИС – полупроводниковая пластина создается из гладкого тонкого дискокремния. Диаметр 150 мм. На пластине создается структура полупроводника и матрицы которые содержит элементы памяти и вспомогательные логические элементы (модули памяти создаются на пластинах образуя полупроводниковый диск) Этапы создания :- выращивание кремниевой заготовки и получение из нее пластины, в дальнейшем из таких монокристаллических заготовок нарезают круглые пластины «таблетки» толщина 0,2-1мм, диаметр от 5 до 20 см., поверхность которых отполировывается до зеркального блеска.- нанесение защитной пленки диэлектрика (оксид кремния), выполняющей функцию диэлектрика и защитной пленки при дальнейшей обработке кристалла крмения. Пластины помещают в камеру, где при высоких температуре и давлении происходит диффузия кислорода в поверхностные слои пластины, приводящая к окислению кремния и образования пленки диоксида кремния. После необходимо удалить пленку с тех мест, которые будут подвергаться дальнейшей обработке. Удаление пленки осуществляется посредством травления, а для того чтобы пленка удалялась только в нужных местах, на поверхность наносят слой фоторезиста (особого состава, который изменяет свои свойства под воздействием ультрафиолетового излучения) Облученные области становятся растворимыми в кислотной среде. После засвечивания слоя фоторезиста приходит очередь травления с целью удаления пленки диоксида кремния. Используется сухой метод травления: для удаления с поверхности пластины диоксида кремния применяется ионизированный газ.(плазма). Газ вступает в реакции. С поверхностью диоксида кремния, в результате чего образуются побочные летучие продукты. После травления, т.е. когда оголены нужные области чистого кремния, удаляется оставшаяся часть фотослоя, и на кремниевой основе остается рисунок, выполненный диоксидом кремния.Процесс внедрения примесей осуществляется посредством диффузии-равномерного внедрения атомов примеси в кристаллическую решетку кремния. Для процесса диффузии легирующей примеси применяется ионная имплантация, при которой ионы нужной примеси проникают в поверхностные слои кремния.Этап ионной имплантации завершается созданием необходимого слоя полупроводниковой структуы, в котором сосредоточены десятки миллионов транзисторов. Далее необходимо в нужной последовательности соединить их между собой проводниками. Для соединения транзисторов друг с другом применяют несколько слоев металлизации. Необходимо создать проводящие контакты стоков, истоков и затворов, для этого по мастке в нужных местах вытравливается слой диоксида кремния, и соответствующие окна заполняются атомами металла. Для создания очередного слоя на полученном рисунке схемы выращивается дополнительный тонкий слой диоксида кремния.После этого наносятся слой проводящего металла и ещё один слой фоторезиста. Процесс нанесения слоев заканчивается когда схема собрана полностью. Прошедшая тестирование матрица помещается в керамический прямоугольный футляр, из которого выходят ножки, микроразъемы интерфейса процессора, с помощью которых процессор помещается и закрепляется в гнезде(socket) на системной плате компьютера.

12) Классификация цифровых устройств вычислительной техники: В общем случае на вход цифрового устройства поступает множество двоичных переменных X(x1 … xn), а с выхода снимается множество двоичных переменных Y(y1 … yk),. Устройство при этом осуществляет определенную логическую функцию между входными и выходными переменными.Цифровые устройства можно разделить на комбинационные и последовательностные.В комбинационных – значения Y в течение каждого такта определяются только значениями X в этом же такте. Такие устройства состоят из логических элементов.В последовательностных – значения Y определяются значениями X, как в течение рассматриваемого такта, так и существовавшими в ряде предыдущих тактов. Для этого в последовательностных устройствах, кроме логических должны быть еще и запоминающие элементы.

Структура

последовательностного и комбинационного

устройства приведена на рис. 4.Запоминающее

устройство может хранить информацию

не бесконечно большого, а только

ограниченного числа тактов, поэтому

цифровые устройства с памятью называют

конечными автоматами, к которым относят

все ЭВМ.Таблицы, показывающие взаимосвязь

между входными и выходными переменными

комбинационных устройств, называют

таблицами истинности. Алгебраическая

форма этих связей представляет систему

уравненийy1

= y1

(x1

, x2

, …, xn),yk

= yk

(x1

, x2

, …, xn).

В общем виде в последовательностных

устройствах выходные переменные yi

зависят не только от входных сигналов

xm

, но и от сигналов элементов памяти,

поступающих за этот же такт.Для описания

работы последовательностных устройств

используются таблицы переходов

состояний.Таблицы истинности соответствуют

только статическим или установившимся

режимам работы цифровых устройств. При

изменении входных сигналов в комбинационной

схеме из-за инерционности логических

элементов в ней начинает протекать

переходный процесс. Максимальная

длительность переходного процесса

определяется максимальным числом

последовательно включенных логических

элементов. Входные сигналы xm

изменяются не мгновенно, а в течение

некоторого времени фф

, т. е. сигналы имеют фронты конечной

длительности. В течение этого времени

входные сигналы имеют неопределенное

значение. По этой причине, а также из-за

задержек сигналов в логических элементах

выходные сигналы комбинационной схемы

в течение переходного процесса могут

принимать значения не соответствующие

описывающим их функциям. Это явление

называют переходными состояниями

.Появление кратковременных ложных

значений выходных сигналов комбинационной

схемы может привести к неправильному

срабатыванию других схем, подключенных

к ее выходам.Цифровые устройства можно

разделить на асинхронные и синхронные.

В асинхронных изменение входных сигналов

сразу же вызывает изменение выходных

сигналов. В синхронных изменение выходных

сигналов, соответствующее новому

сочетанию входных, происходит только

после подачи синхронизирующих (тактовых)

импульсов, управляющих работой автомата.

Период синхроимпульсов является, таким

образом, минимальным временем между

выполнением автоматом двух последовательных

микроопераций, т.е. служит единицей

машинного времени, называемой тактом.

В зависимости от структуры автомата за

один такт могут выполняться одна или

несколько микроопераций, если они

совмещены во времени.В асинхронных

устройствах отсутствуют синхронизирующие

сигналы, поэтому в их структуры обычно

включаются специальные схемы, которые

после окончания каждой микрооперации

вырабатывают сигнал готовности к

выполнению следующей микрооперации.Синхронные

устройства, в принципе, имеют меньшее

быстродействие, чем асинхронные, однако

в них легко устраняются опасные

состязания. Последовательностные:

Триггер, регистр,счетчики, Комбинационные:

кодер,декодер,мультиплексор.(подробные

их описания смотреть в 13-20 билетах)

Структура

последовательностного и комбинационного

устройства приведена на рис. 4.Запоминающее

устройство может хранить информацию

не бесконечно большого, а только

ограниченного числа тактов, поэтому

цифровые устройства с памятью называют

конечными автоматами, к которым относят

все ЭВМ.Таблицы, показывающие взаимосвязь

между входными и выходными переменными

комбинационных устройств, называют

таблицами истинности. Алгебраическая

форма этих связей представляет систему

уравненийy1

= y1

(x1

, x2

, …, xn),yk

= yk

(x1

, x2

, …, xn).

В общем виде в последовательностных

устройствах выходные переменные yi

зависят не только от входных сигналов

xm

, но и от сигналов элементов памяти,

поступающих за этот же такт.Для описания

работы последовательностных устройств

используются таблицы переходов

состояний.Таблицы истинности соответствуют

только статическим или установившимся

режимам работы цифровых устройств. При

изменении входных сигналов в комбинационной

схеме из-за инерционности логических

элементов в ней начинает протекать

переходный процесс. Максимальная

длительность переходного процесса

определяется максимальным числом

последовательно включенных логических

элементов. Входные сигналы xm

изменяются не мгновенно, а в течение

некоторого времени фф

, т. е. сигналы имеют фронты конечной

длительности. В течение этого времени

входные сигналы имеют неопределенное

значение. По этой причине, а также из-за

задержек сигналов в логических элементах

выходные сигналы комбинационной схемы

в течение переходного процесса могут

принимать значения не соответствующие

описывающим их функциям. Это явление

называют переходными состояниями

.Появление кратковременных ложных

значений выходных сигналов комбинационной

схемы может привести к неправильному

срабатыванию других схем, подключенных

к ее выходам.Цифровые устройства можно

разделить на асинхронные и синхронные.

В асинхронных изменение входных сигналов

сразу же вызывает изменение выходных

сигналов. В синхронных изменение выходных

сигналов, соответствующее новому

сочетанию входных, происходит только

после подачи синхронизирующих (тактовых)

импульсов, управляющих работой автомата.

Период синхроимпульсов является, таким

образом, минимальным временем между

выполнением автоматом двух последовательных

микроопераций, т.е. служит единицей

машинного времени, называемой тактом.

В зависимости от структуры автомата за

один такт могут выполняться одна или

несколько микроопераций, если они

совмещены во времени.В асинхронных

устройствах отсутствуют синхронизирующие

сигналы, поэтому в их структуры обычно

включаются специальные схемы, которые

после окончания каждой микрооперации

вырабатывают сигнал готовности к

выполнению следующей микрооперации.Синхронные

устройства, в принципе, имеют меньшее

быстродействие, чем асинхронные, однако

в них легко устраняются опасные

состязания. Последовательностные:

Триггер, регистр,счетчики, Комбинационные:

кодер,декодер,мультиплексор.(подробные

их описания смотреть в 13-20 билетах)

13. Триггер - устр-во последовательного типа состоящее из логических элементов предназначенного для хранения единицы информации(бита). Умеет мгновенно переходить из одного состояния в другое и обратно. Предназначен для запоминания одного разряда двоичного кода.

Триггер хранит свое состояние до тех пор пока комбинация входных сигналов неизменна и (или) на управляющем входе будет ноль.

1)Синхронный (вход С): -стробируемые, один раз подал сигнал и система работает. –тактируемые, каждый раз нужно подавать разрешающий сигнал на С.

2)Асинхронный (нет С)

Асинхронный R(reser)S(set)-триггер

S |

R |

Q |

!Q! |

0 |

0 |

Без изменений |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

Не опред. состяние |

|

R-ставит в 1, S-ставит в 0

Синхронный RS-триггер

С |

S |

R |

Q |

!Q! |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

Не опред. сост |

|

J(set)K(reset)-триггер, содержит схемные дополнения, которые снимают неопределенность состояния при подаче 1 на оба входа, при этом происходит переброс схемы в противоположное состояние. (универсальльный)

J |

K |

Q |

!Q! |

0 |

0 |

Без изм. |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Переброс состояния |

|

Т-триггер, имеет единственный вход, при подаче 1 осуществляется переброс схемы.

Могут использоваться для создания двоичных счетчиков(счетчик адреса команд).

D-триггер имеет информационный вход D и вход синхронизации С. Состояние на выходе D-триггеров отржает информацию, поступившую на его информационный вход в течении воздействия синхросигнала.

Область применения: -в составе более сложных устройств, регистр, счетчик, АЛУ,МП. –«независимо», кнопка вкл/выкл.

14. Регистр-устройство состоящее из триггеров определенным образом связанных друг с другом, предназначенное для хранения магнитного слова. Регистр умеет сбрасываться, принимать слова, выдавать слова, сдвигать слова влево или вправо на требуемое количество разрядов, преобразовать последовательный код в параллельный и наоборот, разрядные логические операции.

По способу приема и выдачи информации регистры делаться на:

-параллельные, исаользуются для выполнения операций приема, хранения, выдачи и поразрядных логических операции над словами и представляют собой совокупность RS,D,T-триггеров, имеющих связанные входные и выходные цепи.

-последовательные,

используются для умножения на

![]() ,если сдвиг осуществляется на К разрядов

в сторону старших разрядов. умножение

,если сдвиг осуществляется на К разрядов

в сторону старших разрядов. умножение

![]() ,если

сдвиг осущ.на К разрядов в сторону

младших разрядов. Преобразование кода

из параллельного в последовательный

и обратно. Прямой выход Q предыдущего

разряда поступает на информ.вход D

последующего разряда. Благодаря этому

каждый синхросигнал устанавливает

последующий триггер в состояние, в

котором до этого находился предидущий

триггер, осуществляя тем самым сдвиг

информации на разряды влево или вправо.

,если

сдвиг осущ.на К разрядов в сторону

младших разрядов. Преобразование кода

из параллельного в последовательный

и обратно. Прямой выход Q предыдущего

разряда поступает на информ.вход D

последующего разряда. Благодаря этому

каждый синхросигнал устанавливает

последующий триггер в состояние, в

котором до этого находился предидущий

триггер, осуществляя тем самым сдвиг

информации на разряды влево или вправо.

-универсальные.

15. Счетчик-устройство состоящее из последовательных Т-триггеров для деления частоты(в четное n раз) . Накопительный узел ЭВМ, подсчитывает число импульсов поступивших на его вход.

Характеристики: -коэффициент пересчета(число состояний счетчика)М(количество импульсов, поступивших на вход счетчика, которые переводят его в исходное состояние). –время реакции, интервал времени между поступлением входного сигнала и окончанием самого длительного переходного процесса в счетчике. –разрешающая способность, минимально допустимый период(или макс.частота) следования входных сигналов, при котором счетчик работает без сбоев.

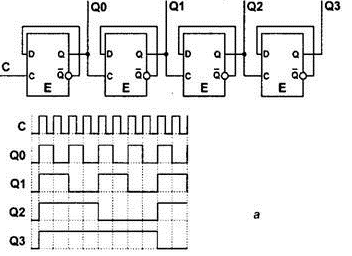

Асинхронные счетчики

Суммирующий счетчик.

Вычитающий счетчик

Вычитающий счетчик, строиться по принципу суммирующего, только подача сигналов осуществляется с инверсных выходов предыдущих разрядов.

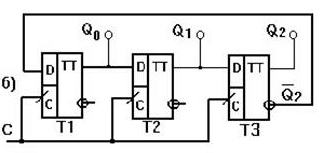

Синхронные счетчики

Трехразрядный кольцевой счетчик

Разрядность

: асинхронные

![]() ,

синхронные 2*n, где n-количество счетчиков.

,

синхронные 2*n, где n-количество счетчиков.

16. Шифратор-устройство комбинационного типа не зависящее от предыдущего значения, предназначенное для преобразования унитарного кода в двоичный. Пример шифратора клавиатура, преобразующая сигналы клавиши в код этой клавиши.

Количество

выходов определяется по формуле

![]() ,

где n-количество выходов. . Если выходов

n, то входных шин должно быть

.

,

где n-количество выходов. . Если выходов

n, то входных шин должно быть

.

17. Дешифратор-устройство комбинационного типа не зависящее от предыдущего значения, предназначенное для преобразования двоичного кода в унтираный. Если входов n, то выходных шин должно быть . Количество входов определяется по формуле , где n-количество выходов.

18. Мультиплексор-устройство вычислительной техники предназначенное для подключения некоторого количества информационных входов к одному выходу. Выбор выходной линии производиться управляющим кодом, поступающим на входы мультиплексора, т.е. в мультиплексорах различаются управляющие и информационные входы. Если управляющих кодов k, то информационных кодов .Мультиплексор обеспечивает временное объединение каналов и является основным узлом, реализующим аппаратную функцию передачи данных.