- •1.3. Параметры цифровых интегральных микросхем

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •2.1. Основы схемотехники элементов ттл

- •Стандартные серии ттл

- •5.1. Классификация и обозначение полевых транзисторов

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •. Диодно-транзисторная логика (дтл)

- •3.2.3. Транзисторно-транзисторная логика

- •3.2.4. Эмиттерно-связанная логика

- •3.2.5. Логические элементы с инжекционным питанием

- •1. Основы микроэлектроники

- •1.1. Гибридные интегральные схемы

- •1.2. Элементы полупроводниковых интегральных схем

- •1.2.1. Биполярные транзисторы и диоды

- •1.2.2. Многоэмиттерные и многоколлекторные транзисторы

- •1.2.3. Транзистор с диодом Шоттки

- •1.2.4. Металл, диэлектрик, полупроводник-транзисторы

- •1.2.5. Резисторы и конденсаторы

- •1.3. Технология изготовления интегральных схем

- •1.3.1. Базовые технологические операции

- •1.3.2. Эпитаксиально-планарная технология

- •1.3.3. Изопланарная технология

- •1.3.4. Технология изготовления мдп-структур

- •2. Аналоговые интегральные схемы

- •2.1. Типовые элементы аналоговых интегральных схем

- •2.1.1. Составные транзисторы

- •2.1.2. Генераторы стабильного тока

- •2.1.3. Динамическая нагрузка

- •2.1.4. Схемы сдвига потенциальных уровней

- •2.2. Усилительные каскады и повторители

- •2.3. Дифференциальные каскады

- •2.4. Выходные каскады аналоговых интегральных схем

- •2.5. Операционные усилители

- •2.6. Применение операционных усилителей

- •2.6.1. Принцип отрицательной обратной связи

- •2.6.2. Инвертирующий усилитель

- •2.6.3. Интегратор и дифференциатор

- •2.6.4 Неинвертирующий усилитель

- •2.6.5. Суммирующий усилитель

- •2.6.6. Дифференциальный усилитель

- •3. Цифровые интегральные схемы

- •3.1. Электронные ключи

- •3.1.1. Электронные ключи на биполярных транзисторах

- •3.1.2. Электронные ключи на полевых транзисторах

- •3.2. Логические элементы интегральных микросхем

- •3.2.1. Транзисторная логика с непосредственными связями

2.1.3. Динамическая нагрузка

Термином «динамическая нагрузка» описывают нелинейные элементы с большим сопротивлением переменному току (большим дифференциальным сопротивлением) и малым сопротивлением по постоянному току, используемые вместо резисторов в выходных цепях усилительных элементов. Фактически речь идет об одной из областей применения генераторов тока. Более того, сам термин «динамическая нагрузка» является условным, так как реальной нагрузкой (получателями сигнала) являются другие элементы.

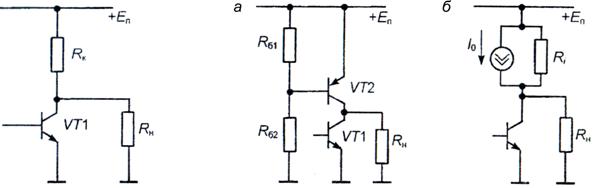

На рис. 2.9 и 2.10,а показаны выходные цепи усилительных каскадов на БТ с линейным резистором Rк и динамической нагрузкой соответственно. Реальная нагрузка (входное сопротивление следующего каскада) обозначена резистором Rн.

Рис. 2.9 Рис. 2.10

Известно, что коэффициент усиления по напряжению возрастает пропорционально увеличению сопротивления нагрузки Rн. Однако, при этом необходимо, чтобы Rк >> Rн, так как в противном случае часть сигнала будет рассеиваться в резисторе Rк. Таким образом, при увеличении Rн необходимо увеличить и Rк, однако, величины, определяющие режим работы по постоянному току Iк(0) и Uк(0) жестко связаны со значениями Rк и En, так как Uк(0) = En – Iк(0) Rк, и возможности изменения Rк практически отсутствуют.

Естественным выходом из данной ситуации является использование вместо Rк генератора тока (рис. 2.10, а). В этом случае легко выполнить условие Ri >> Rн и независимо от него установить любой требуемый ток Iк(0) I0.

Следует отметить, что для получения динамической нагрузки удобно использовать транзисторы с другим типом проводимости (в данном случае р–n–р) и задавать напряжение база-эмиттерV72 относительно шины питания. Применение динамической нагрузки позволяет примерно на порядок увеличить коэффициент усиления по напряжению.

2.1.4. Схемы сдвига потенциальных уровней

В многокаскадных усилителях с непосредственными связями между каскадами на вход каждого следующего каскада поступает не только полезный сигнал, но и постоянная составляющая напряжения с транзистора предыдущего каскада. Устранение избыточного постоянного напряжения осуществляют схемы сдвига потенциальных уровней. При этом переменные сигналы они пропускают без ослабления. Схемы сдвига уровней заменяют разделительные конденсаторы, которые не могут быть реализованы средствами микроэлектроники.

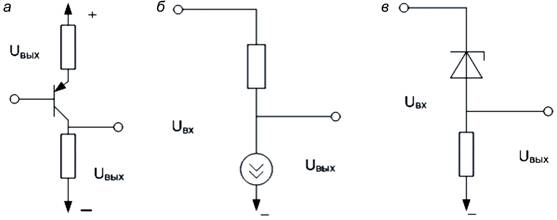

Одним из вариантов решения проблемы накопления постоянных составляющих является чередование каскадов на р–n–р и р–n–р-транзисторах, так как в р–n–р-транзисторах в активном режиме положительное напряжение на коллекторе транзистора больше, чем на базе, а в р–n–р – меньше. Схема сдвига представлена на рис. 2.11, а.

Рис. 2.11

Другим вариантом схем сдвига уровней являются нелинейные делители напряжения.

В схеме на рис. 2.11, б постоянная составляющая на выходе уменьшается на величину I0R0, а в схеме на рис. 2.11, в на величину напряжения стабилизации Uст. При этом для переменных составляющих коэффициенты передачи обеих схем близки к единице, так как на рис. 2.11, б сопротивление R0 выбирается много меньше дифференциального сопротивления генератора тока Ri, а в схеме рис. 2.11, в много больше дифференциального сопротивления стабилитрона rд. Генератор тока может быть построен по любой из ранее рассмотренных схем.