- •1.3. Параметры цифровых интегральных микросхем

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •2.1. Основы схемотехники элементов ттл

- •Стандартные серии ттл

- •5.1. Классификация и обозначение полевых транзисторов

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •. Диодно-транзисторная логика (дтл)

- •3.2.3. Транзисторно-транзисторная логика

- •3.2.4. Эмиттерно-связанная логика

- •3.2.5. Логические элементы с инжекционным питанием

- •1. Основы микроэлектроники

- •1.1. Гибридные интегральные схемы

- •1.2. Элементы полупроводниковых интегральных схем

- •1.2.1. Биполярные транзисторы и диоды

- •1.2.2. Многоэмиттерные и многоколлекторные транзисторы

- •1.2.3. Транзистор с диодом Шоттки

- •1.2.4. Металл, диэлектрик, полупроводник-транзисторы

- •1.2.5. Резисторы и конденсаторы

- •1.3. Технология изготовления интегральных схем

- •1.3.1. Базовые технологические операции

- •1.3.2. Эпитаксиально-планарная технология

- •1.3.3. Изопланарная технология

- •1.3.4. Технология изготовления мдп-структур

- •2. Аналоговые интегральные схемы

- •2.1. Типовые элементы аналоговых интегральных схем

- •2.1.1. Составные транзисторы

- •2.1.2. Генераторы стабильного тока

- •2.1.3. Динамическая нагрузка

- •2.1.4. Схемы сдвига потенциальных уровней

- •2.2. Усилительные каскады и повторители

- •2.3. Дифференциальные каскады

- •2.4. Выходные каскады аналоговых интегральных схем

- •2.5. Операционные усилители

- •2.6. Применение операционных усилителей

- •2.6.1. Принцип отрицательной обратной связи

- •2.6.2. Инвертирующий усилитель

- •2.6.3. Интегратор и дифференциатор

- •2.6.4 Неинвертирующий усилитель

- •2.6.5. Суммирующий усилитель

- •2.6.6. Дифференциальный усилитель

- •3. Цифровые интегральные схемы

- •3.1. Электронные ключи

- •3.1.1. Электронные ключи на биполярных транзисторах

- •3.1.2. Электронные ключи на полевых транзисторах

- •3.2. Логические элементы интегральных микросхем

- •3.2.1. Транзисторная логика с непосредственными связями

1.2. Элементы полупроводниковых интегральных схем

Полупроводниковые интегральные схемы – это интегральные схемы, все элементы и межэлементные соединения которых выполнены в объеме и на поверхности полупроводника. Конструктивной основой ИС является подложка из кремния р-типа или арсенида галлия толщиной 200–300 мкм. Элементы ИС формируются в изолированных от подложки локальных областях n-типа, называемых карманами. Изоляция карманов от подложки может быть осуществлена несколькими способами. Идеальной является изоляция посредством пленки двуокиси кремния (рис. 1.4, б). Однако такой способ технологически трудоемок. Наиболее простым является способ изоляции с помощью обратно смещенного р-n-перехода (рис. 1.4, а), но он не является совершенным из-за наличия обратного тока. Основным способом изоляции в современных ИС является метод комбинированной изоляции (рис. 1.4, в), сочетающий изоляцию диэлектриком и обратно смещенным р-n-переходом.

а SiО2 |

б |

в |

|

||

Рис. 1.4 |

||

1.2.1. Биполярные транзисторы и диоды

Биполярные n–р–n-транзисторы являются основным схемным элементом полупроводниковых ИС. Наибольшее распространение получили транзисторы, имеющие вертикальную структуру, в которой выводы от областей транзистора расположены в одной плоскости на поверхности подложки (рис. 1.5).

Рис. 1.5

Такие структуры формируются в карманах n-типа, глубина которых составляет несколько микрометров, а ширина несколько десятков микрометров. Рабочей областью транзистора является область, расположенная под донной частью эмиттера. Остальные области структуры являются пассивными, они выполняют функции соединения рабочих областей с внешними выводами и обладают значительными сопротивлениями. Изоляция транзистора от подложки обеспечивается путем подачи на коллектор положительного напряжения относительно подложки.

Изопланарные n–р–n-транзисторы также имеют вертикальную структуру и выводы, расположенные на поверхности подложки (рис. 1.6); они отличаются от планарно-эпитаксиальных меньшими размерами и лучшей изоляцией от подложки. При одинаковой площади эмиттерных переходов общая площадь изопланарного транзистора (с учетомплощади изолирующих областей) меньше почти на порядок. Поэтому изопланарные транзисторы находят применение в БИС и СБИС. Глубина залегания эмиттера составляет 0,2...0,4 мкм, толщина базы 0,1…0,2 мкм. В структуре имеются противоканальные области р+-типа, расположенные под вертикальными изолирующими областями. Их назначение – устранить паразитные проводящие каналы между соседними структурами. Для предотвращения появления инверсных каналов создают р+-области, охватывающие электронные карманы в виде кольца.

Рис. 1.6

Транзисторы р–n–р-структуры в ИС играют вспомогательную роль. Их изготовляют одновременно с n–р–n-транзисторами и они, как правило, имеют горизонтальную структуру. В такой структуре эмиттерная и коллекторная области изготовляются одновременно с созданием базовых областей n–р–n-транзисторов. Перенос носителей заряда в таком транзисторе происходит в горизонтальном направлении.

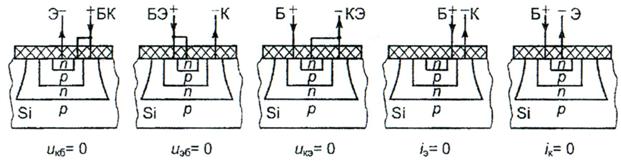

В полупроводниковых ИС в качестве диода можно использовать один из n–р-переходов вертикального n–р–n-транзистора или их комбинацию. Получение диодов таким путем значительно проще, чем формирование специальных диодных структур. Возможны пять вариантов диодного включения n–р–n-транзистора (рис. 1.7). Первый вариант, когда коллектор соединен с базой (Икб = О), обеспечивает наиболее высокое быстродействие диода (восст 1…10 нс), так как избыточный заряд, определяющий быстродействие, накапливается в базе за счет инжекции электронов только со стороны эмиттера. Во всех остальных вариантах накопление избыточного заряда имеет место не только в базе, но и в коллекторе, поэтому быстродействие таких вариантов значительно ниже (восст 10…100 нс).

Рис. 1.7

Для получения высокого пробивного напряжения используют диоды на основе коллекторного перехода.