- •2.Структурная схема импульсного блока питания

- •4.Мультивибраторы на транзисторах (генератор прямоугольных колебаний)

- •5.Одноконтактный трансформаторный с пн (блокинг-генератор)

- •6.Трансформаторные двухтактные пн

- •7.Преобразователи с независимым возбуждением

- •9.Мостовая схема

- •10.Полумостовая схема

- •11.Однотактные преобразователи с независимым возбуджением

- •12.Однотактный преобразователь с обратным включением диода (опно)

- •Достоинство двухтактных преобразователей

- •Недостатки:

- •13.Сравнительный анализ схем преобразователей и область их применения

- •14.Резонансные преобразователи

- •15.Тиристорные преобразователи

- •17. Характеристики и параметры цифровых имс.

- •Статические параметры характеризуют работу имс при статических 0 или 1 на входе и выходе.

- •Динамические характеристики. Они характеризуют работу имс в момент переключения из нуля в единицу или из единицы в ноль.

- •18.Элемент три «и-не» на дтл.

- •19.Параметры интегральных схем

- •21.Каскад с открытым коллектором.

- •22.Логические элементы с тремя выходными состояниями (z-состояние).

- •23.Сравнительные характеристики серии логических микросхем.

- •24.Базовый элемент эмиттерно-связанной логики (эсл).

- •Инвентор

- •26.Инвертор кмоп

- •29.Триггерные системы - rs-триггер как ячейка памяти и уу.

- •30.Функциональное назначение внешних входов

- •31.Асинхронные и синхронные триггеры

- •32.Способы управления триггерами.

- •Двухступенчатый триггер

- •33.Синхронные rs-триггеры.

- •37.Как сделать из jk- триггера d – триггер?

- •40.Несимметричные триггеры (Триггеры Шмита).

- •44.Быстродействующий синхронный многокаскадный счетчик

- •45.Наращивание счетчиков

- •46.Мультиплексоры. Демультиплексоры и дешифраторы.

- •47.Демультиплексоры и дешифраторы.

- •49.Двоичные сумматоры. Одноразрядные двоичные сумматоры. Параллельные многоразрядные сумматоры. Структурные схемы, особенности работы. Основные параметры.

- •51.Однотактный таймер.

- •52.Обобщенная структурная схема многотактного таймера.

- •Одновибраторы, запусаемые при включении напряжения питания.

- •53.Мультивибраторы на однотактном таймере.

- •Базовая структура с диодами.

- •Усовершенствованная схема

- •Мультивибраторы с регулируемыми длительностями импульсов и пауз.

19.Параметры интегральных схем

Для обеспечения работоспособности , необходимо, чтобы логические элементы обладали некоторыми свойствами, которые обеспечат прохождение электрического сигнала по цепочке функциональных узлов без искажений и без потери информации.

Значения уровней сигнала:

-для

ТТЛ (0 - 0,4 (0,5В) -

– напряжение логического нуля;

– напряжение логического нуля;

2,7

– 4,5 -

– напряжение логической единицы )

– напряжение логической единицы )

(эти значения показывают совместимость выходных и входных сигналов)

Нагрузочная способность - сколько входов можно нагрузить на 1 выход; обычно для ТЛ нагрузочная способность = 10;повышенная – до 30 элементов. Выходы могут принимать либо 1 либо отсутствие состояния, а в некоторых схемах есть высокоимпедансное состояние (выход отклонен). Это нужно для………….

Помехоустойчивость – зависит от входных сопротивлений и разницы между уровнями логической 1 и логического 0.

=

(

=

( -

-

)

)

=

(

=

( -

-

)

)

ЭСЛ – 0,1-0,3В

ТТЛ – 0,4-1,1В

КМОП – 2-3В

Входы логических элементов обязательно должны быть подключены к чему-либо ( на 0, 1 или выход предыдущего элемента ). Исключение: ТТЛ (не подключенный вход равносилен логической 1 на входе с пониженной помехоустойчивостью). Неиспользуемые выходы могут оставаться неподключенными. С целью увеличения выходного тока возможно объединение входных и выходных логических элементов. Элементы, рассчитанные на некоторую максимальную емкость нагрузки, которая не должна превышаться. Во избежание снижения помехоустойчивости, уменьшение крутизны выходных фронтов, а так же возможного повреждения выходных транзисторов.

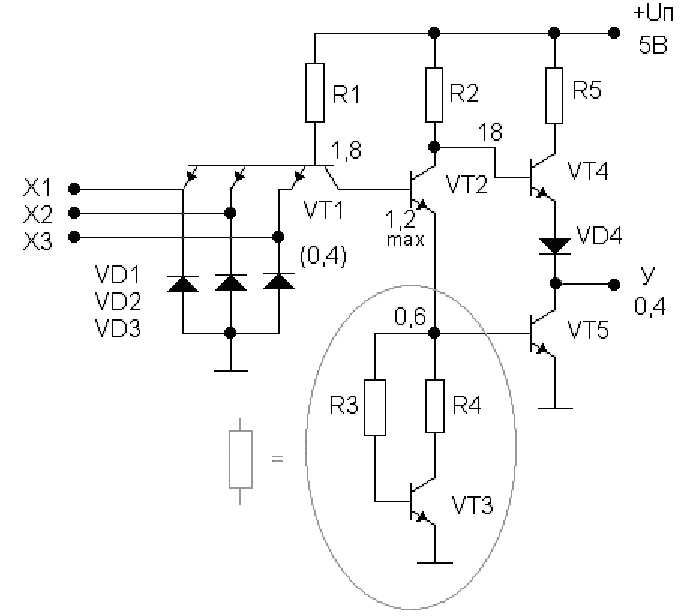

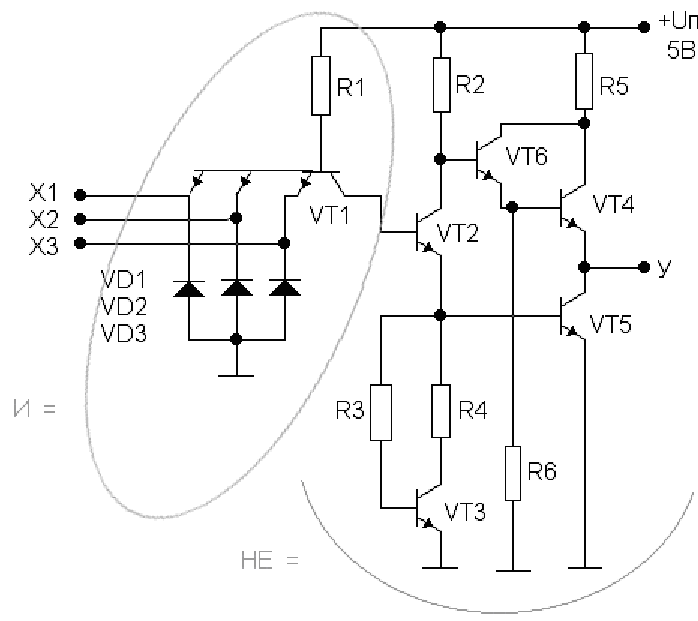

20.Элементы на основе ТТЛ.

В основе – многоэммитерный транзистор.

Серия 155.

При Ux1=Ux2=U1=2,4В VT1 будет включен в инверсном режиме, т.к. UK1max<1,2D, UЭ12=2,4В, т.е. эмитерные переходы заперты, а коллекторные открыты, ток от источника питания через Rб и открытый переход VT1 попадает в базу VT2 и затем VT5

отпирает их и Uy=Uo=0,4В.

Uб4=0,6+0,4=1В, Uk5=0,4В, 1-0,4=0,6В недостаточно чтобы открыть VT4 и VT3(VD3 предотвращает отпирание VT4).

Если хотя бы на одном из входов U0=0,4В UЭ1=0,4В, UЭ < UK, следовательно, VT1 будет в усилительном режиме и открыт эмиттерный и закрыт коллекторный переход.

От источника питания через Rб в базу VT1 течет отпирающий его ток, UK1=0,4+0,4=0,8В, что недостаточно для отпирания VT2 и VT% и они закрыты Uби <=Uпит

VT3 увеличивает крутизну переходной характеристику и в первом приближении её можно считать.

Серия повышенного быстродействия.

VT1, VT2 – VT5 – используются транзисторы Шоттке.

Следующим шагом к повышению быстродействия стало использование транзистора Шотке.

Е сли

на базу подать большое напряжение, то

транзистор может войти в режим насыщения

и его быстродействие уменьшается.

сли

на базу подать большое напряжение, то

транзистор может войти в режим насыщения

и его быстродействие уменьшается.

У диода Шотке напряжение отпирания 0,3-0,4 В. Напряжение на базе транзистора Шотке не может превышать напряжение на его коллекторе более, чем на 0,4 В, т.е. коллекторный переход никогда полностью не открывается транзистор не заходит в режим насыщения, что резко увеличивает его быстродействие.