- •1.Функциональное описание микроконтроллера i80196kc

- •1.1. Обзор архитектуры

- •1.1.1. Ядро 80xc196kc

- •1.1.1.1. Файловый регистр (Register File)

- •1.1.1.2. Регистровое арифметико-логическое устройство (ралу)

- •1.1.1.4. Контроллер памяти ( Memory Controller)

- •1.1.1.5. Контроллер прерываний и pts (Interrupt Controller)

- •1.2. Параметры синхронизации

- •1.3. Внутренние периферийные устройства

- •1.3.1. Стандартные порты ввода-вывода

- •1.3.2. Последовательный порт ввода-вывода

- •1.3.3. Быстродействующий модуль

- •1.3.4. Аналого-Цифровой Преобразователь (ацп)

- •1.3.5. Широтно-импульсный модулятор (шим)

- •1.3.6. Сторожевой Таймер

- •2.Введение в программирование 8xc196kc

- •2.1. Типы программирования микроконтроллера

- •2.2. Система команд

- •2.3. Типы данных

- •2.4. Способы адресации

- •3. Карта памяти микроконтроллера i80c196kc

- •3.1. Основные разделы памяти

- •3.1.1. Разделы внешней памяти

- •3.1.2. Порты 3 и 4

- •3.1.3. Программная память и Память Специального назначения

- •3.1.3.1. Управление доступом к внутренней или внешней памяти

- •3.1.3.2. Память для программ

- •3.1.3.3. Память специального назначения

- •3.1.4. Регистровый Файл(Register File)

- •3.1.4.1. Указатель Вершины стека (sp)

- •3.1.4.2 Регистры Специальных Функций

- •3.2. Работа через горизонтальное окно

- •3.2.1. Выбор hWindow

- •3.3.1. Выбор vWindow

- •3.3.2. Работа с вертикальными окнами и Способы Адресации

- •4. Прерывания

- •4.1 Обработка Прерывания

- •4.2. Описание работы Контроллера Прерывания

- •4.3. Описание работы Периферийной Станции Транзакций(pts)

- •4.4. Приоритеты Прерывания

- •4.5. Изменение Приоритетов Прерывания

- •4.6. Программы Обработки прерывания

- •4.7. Распознавание Прерываний

- •4.8. Время Ожидания Прерывания

- •4.9. Специальные Прерывания

- •4.9.1. Прерывание по Невыполняемому Коду

- •4.9.2. Прерывание по Ловушке Программного

- •4.9.3. Немаскируемое Прерывание

- •4.10. Программирование Прерываний

- •4.11. Предоставление pts Прерывания

- •4.12. Предоставление Стандартных Прерываний

- •4.13. Выбор Источников Прерывания

- •4.14. Регистры Маскирования Прерываний

- •4.15. Регистры Захвата Прерывания

- •4.16. Pts Прерывания

- •4.16.1. Управляющие Блоки pts

- •4.16.1.1. Регистр ptscount

- •4.16.1.2. Прерывание End-of-pts

- •4.16.1.3. Регистр ptscon

- •4.16.2. Краткий Обзор Режима Одиночной

- •4.16.2.1. Пример Режима Одиночной Передачи

- •4.16.3. Краткий Обзор Режима Поблочной

- •4.16.3.1. Пример Режима Поблочной Пересылки

- •4.16.4. Краткий Обзор Режима Сканирования

- •4.16.4.1. Pts Циклы в Режиме Сканирования ацп

- •11Eh ad_result для ach0

- •102H ad_result для acHx

- •100H ad_command для acHx

- •4.16.5. Hsi. Краткий Обзор Режима

- •4.16.5.1. Пример Режима hsi

- •4.16.6. Hso. Краткий Обзор Режима

- •4.16.6.1. Пример Режима hso

- •6. Парраллельные порты ввода - вывода

- •6.1. Краткий Функциональный Обзор

- •6.2.Контакты Порта Ввода

- •6.3. Контакты Порта Вывода

- •6.4. Контакты квази-двунаправленного порта

- •6.5 Контакты Двунаправленного Порта с открытым стоком

- •6.6.Программирование Портов ввода-вывода

- •6.7.Организация Портов Ввода

- •6.7.1. Порт 0

- •6.8. Организация Портов Вывода

- •6.9. Порт 1

- •6.10. Порт 2

- •6.11. Доступ к Порту 3 и Порту 4

- •6.11.1. Порт 3 и Порт 4

- •6.12. Особенности работы с квази - двунаправленными портами

4.16. Pts Прерывания

4.16.1. Управляющие Блоки pts

Каждое PTS прерывание требует блока данных, называемого PTS Управляющим Блоком, Блоком Управления PTS (PTSCB). PTSCB определяет режим PTS, число циклов PTS, и адреса источника и адресата передач данных. Вы должны установить PTSCB для каждого источника прерывания PTS, перед предоставлением прерываний PTS.

Каждый PTSCB требует восьми байтов данных в регистрах RAM. Адрес первого (самого младшего) байта PTSCB хранится в таблице Вектора PTS в памяти специального назначения. Первый байт записывается в адрес, кратный 8 ( граница четырех слов). На рис.11 приведены PTSCB для каждого PTS режима. Неиспользуемые байты PTSCB могут использоваться как дополнительная оперативная память.

Рис.11. Управляющие Блоки PTS

4.16.1.1. Регистр ptscount

Первая ячейка каждого PTSCB - всегда регистр PTSCOUNT. PTSCOUNT определяет число циклов PTS, которые надо последовательно выполнить, без вмешательства цент-

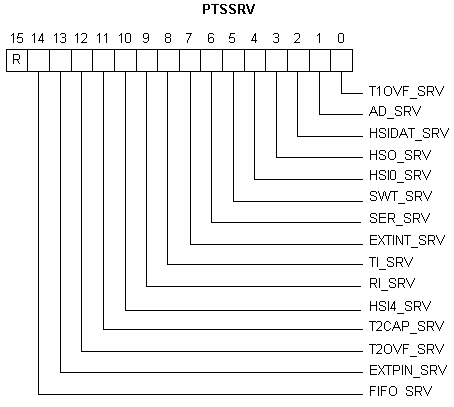

рального процессора. Так как PTSCOUNT - 8-битная величина, то максимальное число циклов - 256. PTSCOUNT уменьшается в конце каждого цикла PTS. Когда PTSCOUNT достигнет нуля, аппаратные средства очищают соответствующий бит регистра PTSSEL и устанавливают соответствующий бит регистра PTSSRV, который запрашивает прерывание "end-of-PTS"(конец PTS). Когда прерывание “end-of-PTS” вызывается, аппаратные средства очищают соответствующий бит в PTSSRV. Для возобновления работы PTS канала, бит в PTSSEL должен быть установлен пользователем.

4.16.1.2. Прерывание End-of-pts

Регистр PTSSRV(07H/06H,HWindow1) регистрирует запросы на прерывания "end-of-PTS". Прерывание “end-of-PTS” - стандартное прерывание, которое указывает, что PTS нуждается в обслуживании. Контроллер Прерывания обрабатывает его программой обработки прерывания, адрес которой хранится в ячейке памяти как у любого стандартного вектора прерывания. Например, PTS обслуживает Transmit прерывание, если установлен PTSSEL.8. Вектор PTS прерывания - 2050H, а соответствующий вектор "end-of-PTS" прерывания - 2030H, стандартный вектор прерывания.

Когда векторы "end-of-PTS" прерывания обслуживаются программой обработки прерывания, аппаратные средства

очищают бит PTSSRV. Программа обработки прерывания должна устанавливать соответствующий бит PTSSEL, чтобы повторно разрешить обслуживание PTS прерывания.

4.16.1.3. Регистр ptscon

Вторая ячейка каждого PTSCB - всегда регистр PTSCON. Три бита регистра PTSCON определяют режим PTS: Одиночная Передача(Single Transfer), Поблочная Пересылка (Block Transfer), Сканирование Аналого-Цифрового преобразователя (A/D Scan), Загрузка CAM HSO (HSO), или Чтение FIFO HSI(HSI)(см.табл.4).

PTS режим определяется следующими битами( см. табл.5 для режимов Одиночной и Поблочной Пересылки и

табл.6 для других режимов ). PTSCON имеет одну конфигурацию для режимов Одиночной и Поблочной Пересылки ( см. риc.12 ) и другую для A/D Scan, HSO, и HSI режимов ( см. Рис.13 ).

Таблица 4. Выбор Режима PTS(Биты 5,6,7 регистра PTSCON)

Бит 7 Бит 6 Бит 5 Выбранный Режим

0 0 0 Block Transfer

0 0 1 HSO Режим

0 1 0

0 1 1 HSI Режим

1 0 0 Single Transfer

1 0 1

1 1 0 A/D Scan

1 1 1

Таблица 5. Биты 0-4 регистра PTSCON (Режимы Одиночной (Single Transfer) и Поблочной (Single Transfer) Пересылки)

Номер Мнемоника Имя Описание

0 DI АВТОИНКРЕМЕНТ PTSDST.Установка этого бита заставляет регистр-приемник

PTS увеличиваться в конце каждого PTS цикла

1 SI АВТОИНКРЕМЕНТ PTSSRC.Установка этого бита заставляет регистр- источник

PTS увеличиваться в конце каждого цикла

2 DU Модификация PTSDST. Установка этого бита заставляет регистр PTSDST сохранять своё последнее значение в конце PTS цикла.Очистка этого бита будет сохранять значение регистра PTSDST , которое было в начале PTS цикла

3 SU Модификация PTSSRC. Установка этого бита заставляет регистр PTSSRC сохранять своё последнее значение в конце PTS цикла. Очистка этого бита будет сохранять значение регистра PTSSRC , которое было в начале PTS цикла

4 BW Передача БАЙТА / СЛОВА. Установка это го бита определяет передачу байта. Очистка этого определяет передачу сло ва.

Рис.12. Регистр PTSCON (Режимы Одиночной и Поблоч- ной Пересылки )

Таблица 6. Бит 3 регистра PTSCON (A/D Scan, HSI, and HSO Режимы)

3 UPDT Модификация Регистра. Установка этого бита заставляет соответствующий регистр(см. ниже)

загружаться значением, которое достигает- ся в конце каждого PTS цикла.

Очистка приводит к загрузке регистров значе- нием, существовавшем в начале PTS цикла

Режим Регистр

A/D PTS_S/D

HSI PTSDST

HSO PTSSRC

Рис.13 Регистр PTSCON ( A/D Scan,HSI,и HSO Режимы )