Формат команд

Формат команд обработки данных группы ARM приведен на рис. 7. Эта команда будет выполнена, если условие Cond истинно, в противном случае команда будет пропущена. Все различные условия перечислены в табл. 2; если суффикс условия опущен, то команда выполняется безусловно.

Рис. 7. Команда обработки данных группы ARM

Команда формирует результат, выполняя указанную арифметическую или логическую операцию с одним или двумя операндами.

Первый операнд – всегда регистр (Rn). Второй операнд (shifter_operand) (табл. 3) может быть регистром со сдвигом (Rm), или 8-битной константой с циклическим сдвигом (#imm8) (в зависимости от значения бита "I" в команде). Следует отметить, что формат команды не позволяет записать константу боле 8 бит и, поэтому недопустимыми являются значения #0x1FF, #0x1FE, #0x1234. Однако, эта записанная в поле команды константа может автоматически циклически сдвигаться на любое четное значение (0, 2, 4, 6, .., 30) и, таким образом, программист может написать константы #0x12, #0xFF, #0x2FC0, #0xC000003F – значение поля сдвига формируется компилятором автоматически. Кроме того, следует знать, что команды, например, ADD и SUB, AND и BIC эквивалентны (комплементарны) за исключением соответственно отрицания и инвертирования операнда 2. Если циклически сдвинутая константа не может быть представлена в 8-битном поле, то используется комплементарная команда, если это не приводит к успеху – выдается сообщение об ошибке.

Флаги CPSR могут оставаться без изменений (S = 0) или выставлены в зависимости от результата выполнения этой команды (S = 1). Некоторые команды (ТSТ, TEQ, CMP, CMN) не записывают результат в регистр Rd. Они используются только для того, чтобы в зависимости от результата установить/сбросить флаги CPSR и, поэтому не включают поле S (предполагается S = 1).

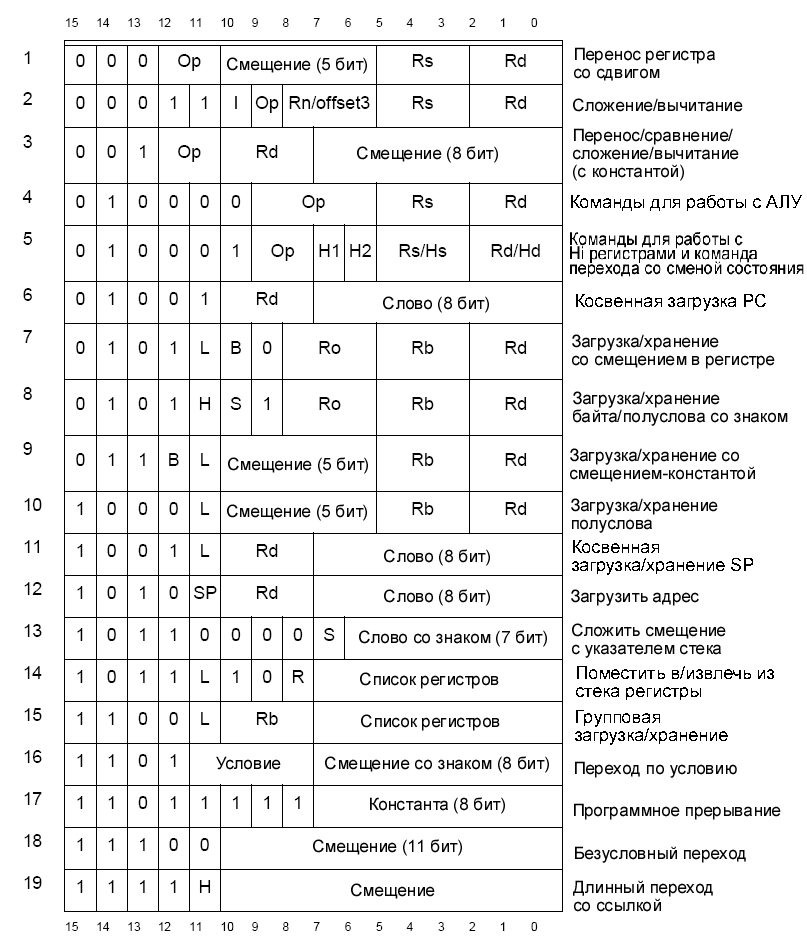

Ниже приведена полная таблица форматов команд набора инструкций ARM

Ниже приведены форматы команда обработки данных группы THUMB

Система команд

Далее приведена таблица 4, которая включает в себя краткое упрощенное описание команд ARM рассматриваемого микроконтроллера. Рассмотрены режим команды, мнемоника в ассемблере, способы адресации, действие команды, число циклов и слов (ЧС). В таблице приведены лишь основные режимы использования команд, она наглядна и понятна для восприятия – в большинстве случаев этого достаточно для использования команд; поле второго операнда Op2 заменяется любым выражением из последней колонки таблицы 3. Для простоты в командах обработки опущены поля {<cond>} (таблица 2, суффикс) и {S} (символ как таковой), если они присутствуют оба. Еще раз напомним, что команда не выполняется, если значение поля <cond> не соответствует полю флагов регистра состояния CPSR, а сгенерированный флаги не запоминаются, если отсутствует символ S. Полное описание каждой команды, включающее все детали и нюансы ее применения, содержится в учебном пособии “Справочник по системе команд”. Кроме того, удобно пользоваться справочной системой, открыв вкладку Books в окне Project Workspace и далее Complete User Guide – здесь Вы найдете информацию и об ассемблере, включая псевдо операторы организации программного кода, и о системе команд – последнее в разделе ARM Instruction Set User’s Guide.

В таблице 4 использованы следующие обозначения:

Rd, Rn, Rm, Rs – угловые скобки в адресах <Rd>, <Rn>, <Rm>, <Rs> этих регистров будут опускаться с целью экономии места в таблице;

cond – условие выполнения команды <cond> из табл. 2 (угловые скобки будут опускаться);

Op2 – один из способов представления операнда 2 <shifter_operand> из табл. 3 (угловые скобки будут опускаться);

* b – число машинных тактов, необходимых для выполнения пустых тактов сопроцессора, а S, I и C зависят от типа машинных тактов (информация взята с сайта http://www.gaw.ru)

Н – Непосредственная адресация

П – Прямая адресация

К – Косвенная адресация

И – Индексная адресация

cad – Command Address – метка, указывающая команду в ассемблерной программе, к выполнению которой следует перейти при определенных условиях. Фактически cad представляет собой 32-х разрядный адрес команды, но этот адрес автоматически преобразуется в относительной смещение со знаком rel и в таком виде храниться в формате команды

rel – относительное смещение со знаком между командой к выполнению которой следует перейти и командой перехода; диапазон возможных переходов зависит от формата команды – для команд B – ±32 Мбайта

#imm, #imm8, … – 8-битная константа (число бит определяется) с автоматическим циклическим сдвигом на любое четное значение (0, 2, 4, 6, .., 30)

РС (= R15) – Program Counter – счетчик команд

НС – непосредственное смещение

РгС – регистровое смещение

Таблица 4. Краткое представление инструкций ARM

|

Мнемоника |

Адр. |

Содержание |

Число циклов |

ЧС |

Примечание |

|

ADD R2, R4, Op2 |

П, Н |

(R2)← (R4) + (Op2) |

1S* |

1 |

Сложение |

|

ADC R5, R3,Op2 |

П, Н |

(R5) ← (R3)+(Op2) + (C) |

1S* |

1 |

Сложение с переносом |

|

AND R2, R4,Op2 |

П, Н |

(R2) ← (R4) & (Op2) |

1S* |

1 |

Логическое «И» , поразр. |

|

B{cond} Rn B{cond} cad B{cond} cad |

П Н Н |

(PC) ← (Rn) (PC) ←rel Если (cond), то (PC)←rel |

2S+1N |

1 |

Команда перехода |

|

BIC Rd,Rn,Op2 |

П, Н |

(Rd) ← (Rn) & (Op2>) |

1S |

1 |

Bit Clear поразрядно |

|

BL{cond} cad |

Н |

(R14) ← (R15); (R15) ← rel |

2 |

1 |

Branch with Link |

|

BX{cond} Rm |

П |

(R15) ← (Rm); еслиRm[0]=0, переключение вARMрежим; еслиRm[0]=1 – то вTHUMB. |

2S+1N |

1 |

Перейти и сразу переключить ядро в другой режим |

|

BLX{cond} Rm |

П |

(R15)← адрес след. истр. BXRm |

|

1 |

Запомнить адрес возврата |

|

CDP{cond} <coproc>, <opcode_1>, Rd, Rn, Rm {, <opcode_2>} |

П |

Сообщение сопроцессору (если он есть) выполнить операции (opcode_1), (opcode_2) |

1S+bI |

1 |

Coprocessor Data Processing |

|

CMP Rn, Op2 |

П, Н |

(Rn) – (Op2); установка флагов |

1S |

1 |

Rd не меняется |

|

CLZ{cond}Rd,Rm |

П |

(Rd) ← число нулевых битов до первого единичного бита в регистре (Rm) |

1 |

1 |

|

|

CMN{cond}Rn, Op2 |

П, Н |

(Rn) + (Op2); установка флагов |

|

1 |

Rd не меняется |

|

EOR Rd, Rn, Op2 |

П, Н |

(Rd) ← (Rn) (Op2) |

1S |

1 |

Исключающее ИЛИ поразрядно |

|

LDC{cond}{L} Coproc, CRd, [Rn] |

|

Передача данных между памятью и сопроцессором |

|

|

|

|

LDM | STM {cond} <mode> Rn{!}, <registers_without_pc> |

П.-И Пр.-И |

Загружает подмножество регистров. Поддерживает различные режимы стека. Эффективна для сохранения / восстановления контекста и передачи больших массивов данных |

nS+1N+ +11 |

1 |

Load Multiple |

|

LDR{cond}Rd, [Rn] |

П, К |

(Rd) ← ((Rn)) |

1S + 1N + 1I |

1 |

Load register |

|

LDR{cond} Rd, [Rn,#imm5] |

П, К |

(Rd) ← ((Rn)+imm5) |

1S + 1N + 1I |

1 |

Load register |

|

LDR{cond}Rd, cad |

П |

(Rd) ← (R15)+rel |

|

1 |

Загрузить адрес команды |

|

LDR{cond}B LDR{cond}H LDR{cond}SB LDR{cond}SH |

П |

Команды аналогичны LDR, но загружают соответственно байт (суффикс “B”), полуслово (суффикс “H”) и с расширением знака (суффикс “S”) |

|

1 |

|

|

MCR{cond} p6,0,R4,c5,c6

|

П, К |

(c6) ← p6 execute (opcode 0) with (R4) |

1S+(b+1)*I+1C |

1 |

Регистровый обмен с сопроцессором |

|

MLA Rd, Rm, Rs, Rn |

П |

(Rd) ← (Rm)*(Rs) + (Rn);

|

1S+I* *(m+1) |

1 |

Умножение с накоплением |

|

MOV Rd, Op2 |

П, Н |

(Rd) ← (Op2) |

1 |

1 |

Move |

|

MRC<cond> <coproc>, <opcode_1>, Rd, <CRn>, <CRm> {, <opcode_2> |

П, К |

Передача данных из сопроцессора в ARM регистр |

1S+ +(b)I+1C |

1 |

|

|

MRS Rd, SPSR MRS Rd, CPSR |

П |

(Rd)← (SPSR) (Rd) ← (CPSR) |

1 |

1 |

Чтение статусного рег. |

|

MSR{cond} SPSR_<fields>, Rm MSR{cond} CPSR_<fields>, Rm MSR{cond} SPSR_<fields>, #imm8 MSR{cond} CPSR_<fields>, #<immed_8r> |

П |

(SPSR) ← (Rm)

(CPSR) ← (Rm)

(SPSR) ← imm8

(CPSR) ←imm8

|

1 |

1 |

Move to Status Register –Запись в статусный регистр |

|

MUL Rd,Rm,Rs |

П |

(Rd) ← (Rm)*(Rs) |

2 |

1 |

Умножение |

|

MVN Rd, Op2 |

П, Н |

(Rd) ← (Op2>) |

1 |

1 |

Загрузка инверсного значения |

|

NOP |

П |

Нет операции; не может использоваться с cond |

1 |

1 |

No OPeration |

|

ORRRd, Rn, Op2 |

П, Н |

(Rd) ← (Rn) OR (Op2) |

1 |

1 |

Поразрядно |

|

RSB Rd,Rn, Op2 |

П, Н |

(Rd) ← (Op2)– (Rn) |

|

|

Reverse subtract |

|

RSС Rd Rn Op2 |

П, Н |

(Rd)←(Op2)–(Rn)– (C) |

|

|

with carry |

|

SBCRd,Rn, Op2 |

П, Н |

(Rd) ← (Rn)–(Op2)– (C) |

1 |

1 |

Вычитание с учетом переноса |

|

SMULBB{cond} Rd,Rm,Rs SMULBT{cond} Rd,Rm,Rs SMULTB{cond} Rd,Rm,Rs SMULTT{cond} Rd,Rm,Rs |

П |

(Rd)←Rm[15:0]*Rs[15:0]

(Rd)←Rm[15:0]*Rs[31:16]

(Rd)←Rm[31:16]*Rs[15:0]

(Rd)←Rm[31:16]*Rs[31:16] |

4 |

1 |

Умножение знаковых 16-битных операндов с 32-битным знаковым результатом |

|

SMLAL<x><y><cond><RdLo>,<RdH1>, Rm,<Rs> |

Пост-И, пред-И |

(RdHi):(RdLo)← (Rm)*(Rs)+(RdHi):(RdLo) |

1S+I* *(m+2) |

1 |

Умножение знаковых 16-битных операндов с 64-битным аккумулированием |

|

STC{cond}{L} <coproc>, <CRd>, <addressig_mode> |

П-И, Пр-И |

Сохранение регистров сопроцессора непосредственно в памяти |

(n-1)S+ +2N+bl |

1 |

|

|

STR{cond} Rd, [<Rb>, #Imm] |

К с НС |

((Rb)+Imm)←(Rd) |

2N |

1 |

Store register |

|

STR{cond} Rd, [<Rb>,<Ro>] |

К с РгС |

((Rb)+(Ro)) ←(Rd) |

2N |

1 |

|

|

STR{cond}Rd,cad |

П |

(R15)+rel ←(Rd) |

2N |

1 |

Сохранить адрес команды |

|

STR{cond}B |

|

Аналогично STR, но сохраняет байт, аRdможет быть только R0, R2, R4, R6, R8, R10, R12 |

2N |

1 |

|

|

STR{cond}H |

|

Аналогично STR, но сохраняет полусловоRd[15:0] |

2N |

1 |

|

|

SUBR2,R4, Op2 |

П |

(R2) ← (R4) – (Op2) |

1 |

1 |

Вычитание |

|

SUB Rd,PC,#imm3 |

П, Н |

(Rd)← (PC) – imm3 |

2S+1N+ +1I |

1 |

Вычесть смещение, заданное в # imm3 из содержимого рег-ра PC |

|

SWI{cond} <imm24> |

Н |

(PC) ←0x08; (SPSR_svc) ← (CPSR); переключение в режим Supervisor |

2S+1N* |

1 |

Прогр. прерывание |

|

SWP{cond} Rd, Rm, [Rn] |

П, К |

(Rd) ← ((Rn)); ((Rn)) ← (Rm) |

2S+1N+1I* |

1 |

Обмен между регистрами и памятью словами |

|

SWP{cond}BRd,Rm, [Rn] |

П, К |

Аналогично SWP, но пересылаются байты без знака |

2S+1N+1I* |

1 |

|

|

TEQ{cond}Rn,Op2 |

П, К |

(Rn)(Op2) ; установка флагов |

1 |

1 |

Тестирование по исключающему ИЛИ |

|

TST{cond}Rn,Op2 |

П, К |

(Rn) & (Op2), установка флагов |

1 |

1 |

|

Список литературы по LPC2000

Интегрированная среда Keil μVision3: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”/ Сост.: М. С. Куприянов, И. С. Зуев, Д.А.Варакин.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С., Варакин Д.А. Порты ввода/вывода микроконтроллеров семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С. Архитектура микроконтроллеров семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Справочник по системе команд микроконтроллера LPC2000 на базе ARM-ядра. Учебное пособие к лабораторным работам по дисциплине “Микропроцессорные системы”/ Сост.: М. С. Куприянов, И. С. Зуев.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С., Варакин Д.А.. Система прерываний микроконтроллеров семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С. Таймеры микроконтроллеров семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С. Модуль ШИМ семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С. Аналого-цифровой преобразователь семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С., Варакин Д.А. Универсальный асинхронный приемопередатчик семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы””.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.

Куприянов М. С., Зуев И.С., Варакин Д.А. Интерфейс SPI семейства LPC2000: Методические указания к лабораторным работам по дисциплине “Микропроцессорные системы”””.– СПб.: СПбГЭТУ “ЛЭТИ”, каф. ВТ, в электронном виде, 2008.