- •Тема II Предельные возможности интегральной микроэлектроники.

- •2.1. Физические ограничения на уменьшение размеров и рост степени интеграции.

- •2.1.1. Минимально допустимые напряжения и токи в ис.

- •Допустимые плотности токов в шинах ис. Электромиграция.

- •2.1.3. Статистическая воспроизводимость технологического процесса.

- •2.1.4. Теплофизические ограничения на рост интеграции.

- •2.1.5. Задержка и искажение импульсов на связях.

- •1) Задержка цифрового сигнала на связях

- •2) Задержка цифрового сигнала на связях (rlc – модель)

- •2.2. Технологические ограничения на уменьшение размеров элементов ис.

- •2.2.1. Предельные возможности фотолитографии.

- •2.2.2. Электронная и ионная литография в микроэлектронике.

- •2.2.3. Формообразующие характеристики процессов легирования.

- •2.3.Предельная степень интеграции.

- •2.3.1. Минимальная площадь, занимаемая одним элементом ис.

- •2.3.2. Плотность записи мдп зу в функции от размеров элемента ис.

2.2.2. Электронная и ионная литография в микроэлектронике.

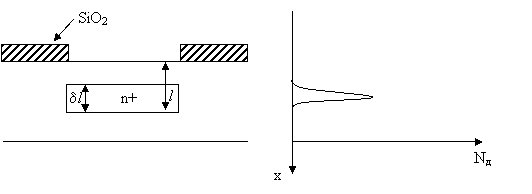

Р ассеяние

электронов в резисте и в ИС.

ассеяние

электронов в резисте и в ИС.

l может достигать 0,5 мкм.

Электронный пучок с малой энергией Е = 5 – 10 кэВ трудно сфокусировать. При E > 100 кэВ растет рассеяние.

Электронная литография достаточно широко применяется при изготовлении фотошоблонов на основе металлических пленок на стекле.

Ионно - лучевая литография обеспечивает предельно высокое разрешение (до 0.01 мкм (10 нм)).

При этом приходится решать ряд специфических проблем:

1) Ионная оптика

2) Управление пучком ионов или создание маски для пучка ионов.

3) Особая трудность – получение устойчивых моноэнергетических пучков ионов достаточной интенсивности.

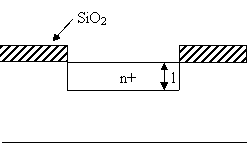

2.2.3. Формообразующие характеристики процессов легирования.

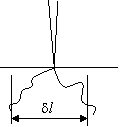

Диффузионное легирование :

П роисходит

размывание краёв области легирования.

роисходит

размывание краёв области легирования.

Ионная имплантация (ионное легирование) :

В этом случае получаются резкие края зоны

легирования.

этом случае получаются резкие края зоны

легирования.

|

|

|

|

С помощью ионной имплантации можно получить заглубленное легирование.

Для этого подбирается энергия ионного пучка. Возможна последующая диффузионная разгонка.

Обратите внимание на получение утоньшённых областей истока и стока в транзисторе с 50 нм каналом. (раздел 1.4.3.).

2.3.Предельная степень интеграции.

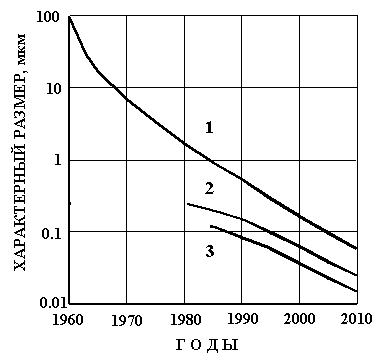

Решающим фактором, определяющим степень интеграции, является характерный размер ИС - в случае КМДП схем это длина канала.

Длина канала определяется разрешающей способностью литографии. В обозримом будущем литография в массовом производстве ИС – это фотолитография. На рисунке показано совершенствование разрешающей способности трёх основных видов литографии по годам: 1 – фотолитография, 2- электронная литография, 3 – ионная литография.

|

|

|

|

2.3.1. Минимальная площадь, занимаемая одним элементом ис.

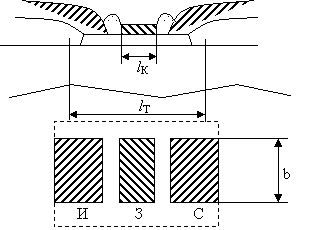

Рассмотрим МДП-транзистор.

Положим :

lT = 10 lK

b = 20 lK

Примем к рассмотрению следующие оценочные соотношения:

Sтр = lTb = 200lK2

Sэл = 5Sтр

Здесь обозначено:

Sтр – площадь, занимаемая непосредственно транзистором.

Sэл – площадь, приходящаяся на один транзистор с учетом подводящих шин и необходимого расстояния между ними.

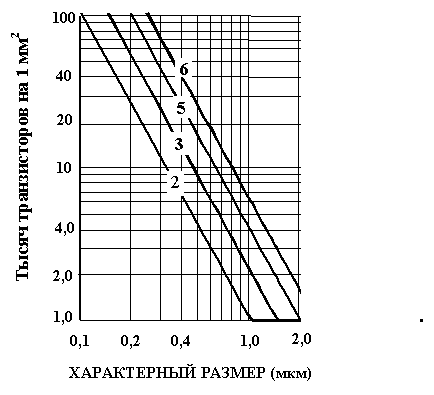

Из приведённых двух формул получаем следующее соотношение, которое связывает площадь, приходящуюся на один транзистор, с его характерным размером:

Sэл = 1000 lK2

Полученная оценочная формула справедлива для случая расположения проводников разводки только на одном уровне.

Статистические данные производства ИС показывают, что с достаточной степенью надежности можно положить:

Sэл = (1000lК2)/m,

где m – число уровней разводки межсоединений.

Это подтверждается графиками, приведёнными на нижеследующем рисунке, на котором показана плотность размещения элементов ИС в тысячах транзисторов на квадратный миллиметр в функции от характерного размера транзистора (длины канала). Цифры на графиках отвечают числу уровней разводки.

|

|

|

|