- •Особенности схемотехники и основные параметры транзисторно-транзисторной логики.

- •Особенности схемотехники ттлш.

- •Особенности схемотехники эмиттерно-связанной логики.

- •Особенности схемотехники и основные параметры инжекционной интегральной логики.

- •Ключевые схемы на мдп (моп)-транзисторах.

- •Принципы проектирования комбинационных устройств.

- •Сумматоры и вычитающие устройства.

- •Цифровые компараторы.

- •Преобразователи кодов.

- •Кодирующие и декодирующие устройства.

- •Мультиплексоры и демультиплексоры.

- •Триггеры: общие сведения.

- •Регистры.

Цифровые компараторы.

Компараторы (устройства сравнения) определяют отношения между двумя словами. Основными отношениями, через которые можно выразить остальные, можно считать два — "равно" и "больше". Определим функции, вырабатываемые компараторами, следующим образом: они принимают единичное значение (истинны), если соблюдается условие, указанное в индексе обозначения функции. Например, функция Рд = в = Ь

если

А = В и принимает нулевое значение при

А ф В. Приняв в качестве основных отношения

"равно" и "больше", для остальных

можно записать:

![]()

Эти отношения используются как логические условия в микропрограммах, в устройствах контроля и диагностики ЭВМ и т. д. В сериях цифровых элементов обычно имеются компараторы с тремя выходами: "равно", "больше" и "меньше" (рис. 2.16). Для краткости записей в индексе выходных функций указывается только слово А.

Устройства

сравнения на равенство строятся на

основе поразрядных операций над

одноименными разрядами обоих слов.

Слова равны, если равны все одноименные

их разряды, т. е. если в обоих нули или

единицы. Признак равенства разрядов![]()

Признак

неравенства разрядов![]()

Признак равенства слов R = rn_i rn_2...ro.

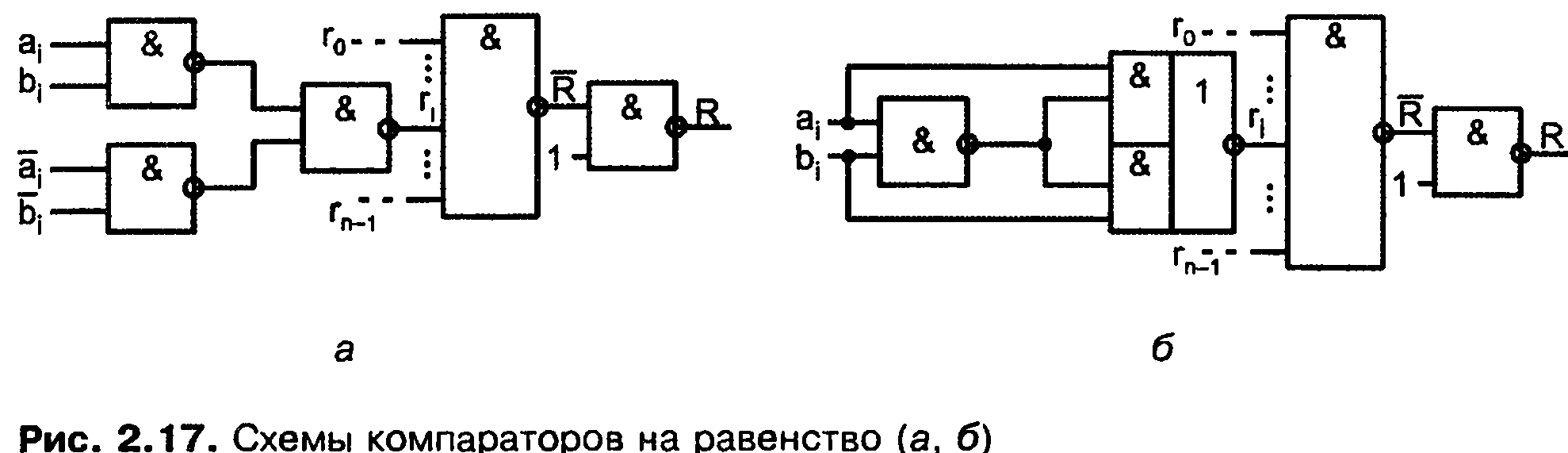

Схема компаратора на равенство в базисе И-НЕ показана на рис. 2.17, а.

Схема без парафазных входов (рис. 2.17, б) основана на выражениях для г„

преобразованных

следующим образом:

![]()

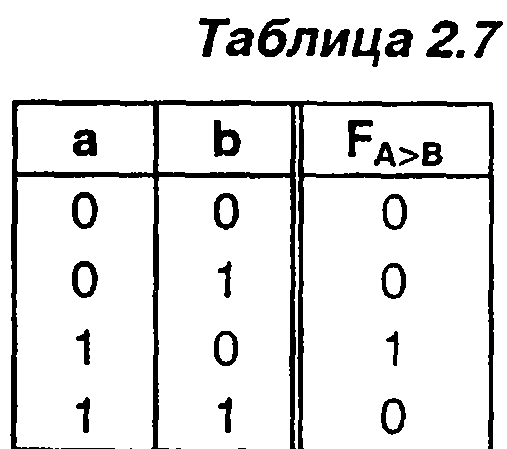

Построение компаратора на "больше" для одноразрядных слов (табл. 2.7) требует реализации функции FA>B=a5.

Преобразователи кодов.

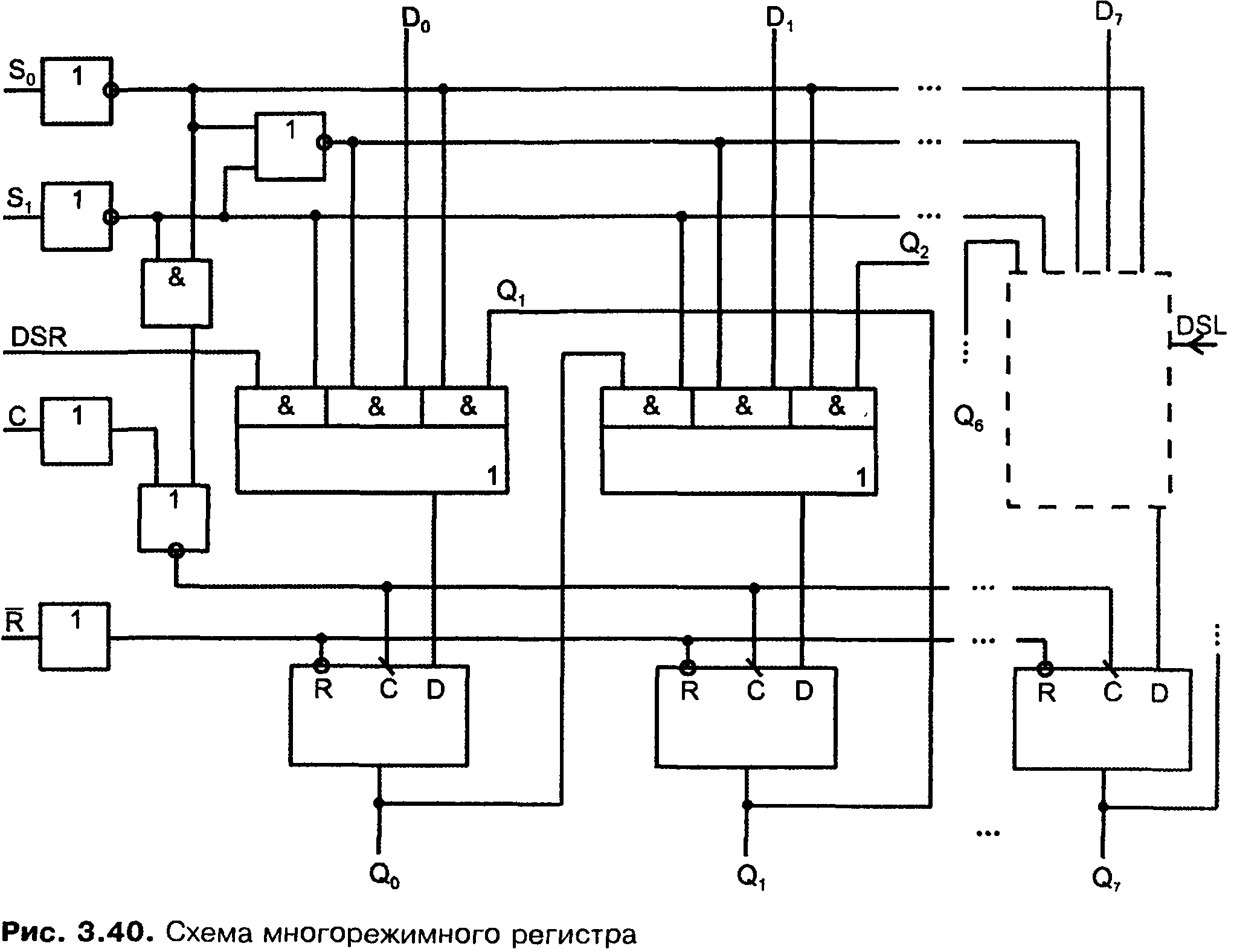

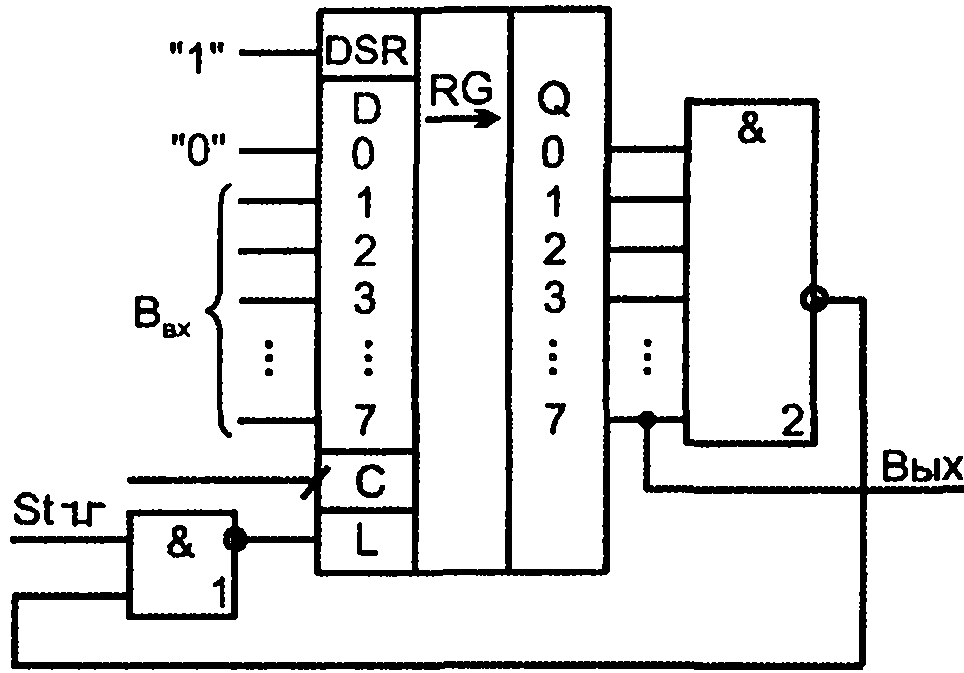

Регистры, имеющие разнотипные вход и выход, служат основными блоками преобразователей параллельных кодов в последовательные и обратно. На рис. 3.42 показана схема преобразователя параллельного кода в последовательный на основе восьмиразрядного регистра типа SI/PI/SO. В этой схеме отрицательный стартовый импульс St, задающий уровень логического нуля на верхнем входе элемента 1, создает единичный сигнал параллельного приема данных на вход L (Load — загрузка), по которому в разряды 1...7 регистра загружается

преобразуемое слово Di_7, а в нулевой разряд — константа 0. На последовательный вход DSR подана константа 1.

Таким образом, после загрузки в регистре формируется слово 0D1D2...D7. Тактовые импульсы, поступающие на вход С, вызывают сдвиги слова вправо (для условного обозначения это соответствует сдвигу вниз). Сдвиги выводят слово в последовательной форме через выход Q7. Вслед за информационными разрядами идет ноль (константа "О"), после которого цепочка единиц. Пока ноль не выведен из регистра, на выходе элемента 2 действует единичный сигнал. После вывода нуля все входы элемента 2 становятся единичными, его выход приобретает нулевое значение и через элемент 1 формирует сигнал автоматической загрузки следующего слова, после чего цикл преобразования повторяется.

В перечне микроопераций, выполняемых

регистрами, были указаны поразрядные

логические операции. Современные

регистры мало приспособлены для

выполнения этих операций, однако при

необходимости их можно выполнить,

пользуясь регистрами на RS-триггерах.

Для выполнения операции ИЛИ на S- входы

статического регистра с исходным нулевым

состоянием подается первое слово А,

единичные разряды которого устанавливают

соответствующие триггеры. Затем без

сброса регистра на S-выходы подается

второе слово В. Ясно, что в результате

получим результат Q = А\/В. При выполнении

поразрядной операции И в первом такте

на S-входы регистра подается слово А,

устанавливающее те разряды регистра,

в которых слово А имеет единицы. Затем

следует подать на регистр слово В.

перечне микроопераций, выполняемых

регистрами, были указаны поразрядные

логические операции. Современные

регистры мало приспособлены для

выполнения этих операций, однако при

необходимости их можно выполнить,

пользуясь регистрами на RS-триггерах.

Для выполнения операции ИЛИ на S- входы

статического регистра с исходным нулевым

состоянием подается первое слово А,

единичные разряды которого устанавливают

соответствующие триггеры. Затем без

сброса регистра на S-выходы подается

второе слово В. Ясно, что в результате

получим результат Q = А\/В. При выполнении

поразрядной операции И в первом такте

на S-входы регистра подается слово А,

устанавливающее те разряды регистра,

в которых слово А имеет единицы. Затем

следует подать на регистр слово В.

Чтобы в регистре сохранились единицы только в тех разрядах, в которых

единицы имеют оба слова, слово В подается на входы R триггеров в ин-

версном виде. Сложение по модулю 2 может быть выполнено схемой с триггерами типа Т в

разрядах путем последовательной во времени подачи на нее двух слов А и В.