- •Особенности схемотехники и основные параметры транзисторно-транзисторной логики.

- •Особенности схемотехники ттлш.

- •Особенности схемотехники эмиттерно-связанной логики.

- •Особенности схемотехники и основные параметры инжекционной интегральной логики.

- •Ключевые схемы на мдп (моп)-транзисторах.

- •Принципы проектирования комбинационных устройств.

- •Сумматоры и вычитающие устройства.

- •Цифровые компараторы.

- •Преобразователи кодов.

- •Кодирующие и декодирующие устройства.

- •Мультиплексоры и демультиплексоры.

- •Триггеры: общие сведения.

- •Регистры.

Принципы проектирования комбинационных устройств.

В состав ЦУ, как правило, входят типовые функциональные узлы и некоторое количество логических схем, специфичных для данного конкретного проекта (как иногда говорят — произвольной логики). Проектирование произвольной логики комбинационного типа производится по этапам.

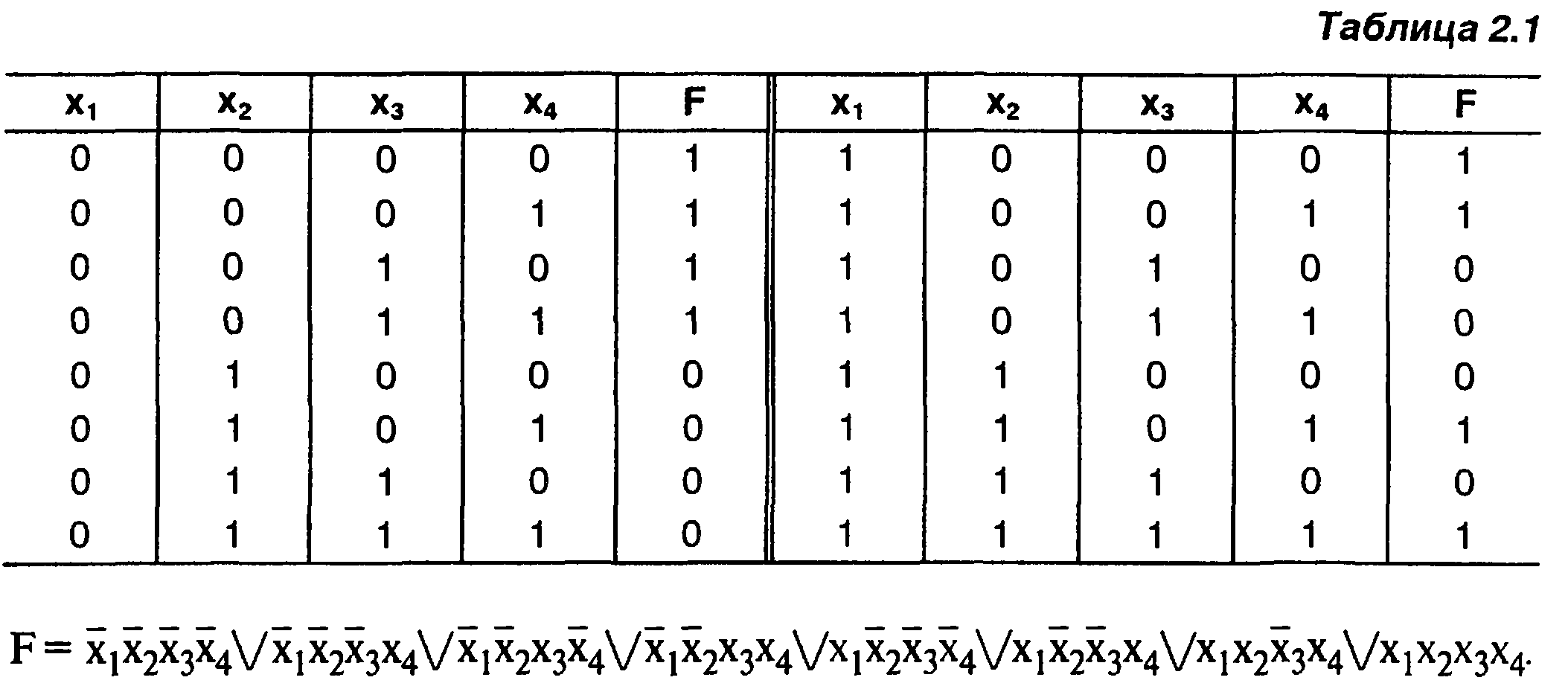

Прежде всего, задается характер функционирования КЦ. Это может быть сделано различными способами, чаще всего пользуются таблицами функционирования (таблицами истинности), задающими значение искомых функций на всех наборах аргументов. От таблицы легко перейти к СДНФ искомых функций (СДНФ — совершенная дизъюнктивная нормальная форма, т. е. дизъюнкция конъюнктивных членов одинаковой размерности).

Для этого составляют логическую сумму тех наборов аргументов, на которых функция принимает единичное значение.

Например, для подлежащей воспроизведению функции четырех аргументов,

заданной табл. 2.1, получим.

Дальнейшие действия зависят от средств реализации функций, к которым в современной схемотехнике относятся:

Логические блоки табличного типа (LUTs, Look-Up Tables).

Логические блоки в виде последовательности матриц элементов И и ИЛИ (PLA, Programmable Logic Array; PAL, Programmable Array Logic).

3. Универсальные логические блоки на основе мультиплексоров.

4. Логические блоки, собираемые из логических элементов некоторого базиса (SLC, Small Logic Cells).

Если КЦ будет реализована на основе логических блоков табличного типа, то СДНФ явится окончательным выражением функции, и никаких дальнейших преобразований этой формы не потребуется.

Если данный проект реализуется на логических блоках, в виде последовательно включенных матриц элементов И и ИЛИ либо их эквивалента в другом базисе, то исходную СДНФ можно минимизировать, если, конечно, возникает такая необходимость.

Как только находится форма с достаточно малым числом термов, поиск других форм можно прекратить, т. к. дальнейшее уменьшение числа термов системы эффекта не даст.

Синтез КЦ на логических блоках типа SLC, т. е. на вентильном уровне, является самым традиционным и изученным (термином "вентиль" называют базовые логические ячейки, выполняющие простейшие операции, для многих ИС эту роль играют элементы И-НЕ с двумя-тремя входами).

В этом варианте проектирование КЦ содержит следующие этапы:

П минимизацию логических функций;

D переход к заданному логическому базису.

Сумматоры и вычитающие устройства.

Сумматоры выполняют арифметическое (в противоположность логическому) сложение и вычитание чисел. Имеют самостоятельное значение и являются также ядром схем арифметико-логических устройств (АЛУ), реализующих ряд разнообразных операций и являющихся непременной частью всех процессоров. Аппаратная сложность и быстродействие сумматора являются очень важными параметрами и поэтому разработано множество вариантов сумматоров, которые имеют разветвленную классификацию. Выделяя главные варианты, остановимся на следующих типах сумматоров:

Одноразрядный

сумматор

имеет три входа (два слагаемых и перенос

из предыдущего разряда) и два выхода

(суммы и переноса в следующий разряд).

Аналитические

выражения функций суммы и переноса![]() ;

;

Сумматор для последовательных операндов содержит всего один одноразрядный сумматор, обрабатывающий поочередно разряд за разрядом, начиная с младшего. Сложив младшие разряды, одноразрядный сумматор вырабатывает сумму для младшего разряда результата и перенос, который запоминается на один такт. В следующем такте складываются вновь поступившие разряды слагаемых с переносом из младшего разряда и т. д.;

Сумматор для параллельных операндов с последовательным переносом строится как цепочка одноразрядных, соединенных последовательно по цепям переноса.

Там, где в разряд сумматора должны подаваться инверсные аргументы, в их линиях имеются инверторы, а там, где вырабатывается инверсная сумма, инвертор включен в выходную цепь. Важно, что инверторы не входят в цепь передачи переноса — они при этом не замедляют работу сумматора в целом.;

П сумматор для параллельных операндов с параллельным переносом разработаны для получения максимального быстродействия.;

О сумматор групповой структуры с цепным переносом при £ группах имеет £~ 1 блок

переноса. Блоки переноса включены последовательно и образуют тракт передачи переноса (рис. 2.30). Слагаемые разбиты на m-разрядные поля, суммируемые в группах. Результат также составляется из m-разрядных полей. ;

О сумматор с условным переносом давно известная структура, которая со временем вышла из широкого применения, но сейчас возродилась в новейших СБИС программируемой логики. Эта структура улучшает быстродействие сумматоров с последовательным переносом. В СБИС программируемой логики FLEX 8000 была реализована цепь последовательных переносов с малыми задержками A не на разряд). Это возродило интерес к структурам с последовательным переносом и, соответственно, к методам улучшения их быстродействия.

Наряду с сумматорами могут быть реализованы вычитатели, однако это почти никогда не делается, поскольку вычитание выполняется через сложение с применением дополнительных либо обратных кодов.